SiC MOSFET:栅-源电压的浪涌抑制方法

本文关键要点

・浪涌抑制电路的电路板布局要考虑大电流高速开关的情况。

・尽量将寄生电容、电感、电阻控制得更低。

・尽量减少回流线环路,以便有效地控制EMI(电磁干扰)。

此前,我们已经就SiC MOSFET的正电压浪涌对策和SiC MOSFET的负电压浪涌对策进行了说明。本文将介绍实际制作这种浪涌抑制电路时电路板布局方面的注意事项。

关于SiC功率元器件中栅极-源极间电压产生的浪涌,在之前发布的Tech Web基础知识 SiC功率元器件 应用篇的“SiC MOSFET:桥式结构中栅极-源极间电压的动作”中已进行了详细说明,如果需要了解,请参阅这篇文章。

关于浪涌抑制电路的电路板布局注意事项

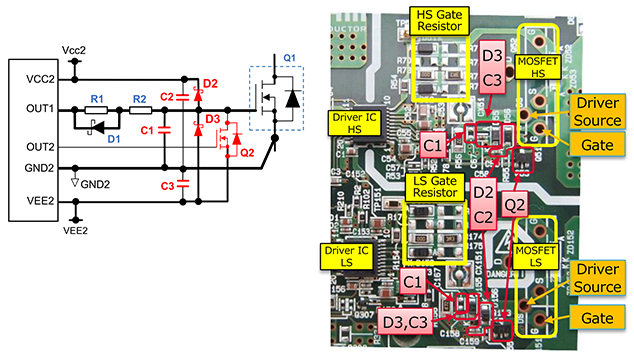

浪涌抑制电路的元器件布局和焊盘布局会直接影响浪涌抑制效果,因此为了获得理想的效果,在此介绍几点需要着重注意的问题。首先,请看浪涌抑制电路和电路板布局的示例。该电路图是此前用过的电路图的一部分。电路板上配置了HS和LS两个电路。

浪涌抑制电路和电路板布局示例

在这块电路板上,桥式结构的HS MOSFET配置在上方,LS MOSFET配置在下方,栅极引脚和驱动器源极引脚被配置在各MOSFET的下方。VGS浪涌电压抑制电路紧靠各栅极引脚配置,是以最短距离连接的。这种精心的布局旨在更大程度地降低寄生电容、电感和电阻。

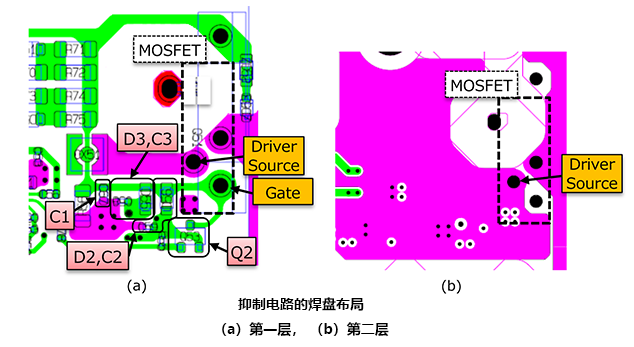

接下来,请看浪涌抑制电路的焊盘图案布局。

如果具有多个浪涌抑制电路,那么应当优先确定米勒钳位用MOSFET(Q2)的安装位置。其次时配置负浪涌钳位SBD(D2)及其旁路电容(C2),并按正浪涌钳位SBD(D3)、旁路电容(C3)和误导通抑制电容(C1)的顺序决定配置位置。这样做的原因是由于布线电感的影响,会导致浪涌抑制效果大大降低,尤其是当米勒钳位MOSFET距离只有几厘米时。

另外,非常重要的一点是,要尽量缩短由浪涌抑制电路的回流线(从驱动器源极引脚返回的线)和浪涌抑制电路的布线所形成的环路。由于SiC MOSFET的高速开关,ID中的di/dt会引起较大的EMI,所以其布线环路应尽量避免受ID产生的EMI的影响。这次评估的电路板是4层结构,第2层全为回流线。因此,可以将回流线直接置于浪涌抑制电路正下方,从而可以更大程度地缩小环路面积。

如果来自驱动电源的阻抗足够小,那么就不需要与钳位SBD并设的旁路电容器,但是由于驱动电源通常距离较远,所以需要在SBD附近安装一个旁路电容器,以便SBD能够以低阻抗工作。此外,在选择电容器时,请充分考虑阻抗特性并选择在几十MHz频段上具有谐振点的电容器(0.1µF,1.0×0.5mm尺寸)。

审核编辑:汤梓红