什么是移位运算符

描述

数字硬件建模SystemVerilog-移位运算符

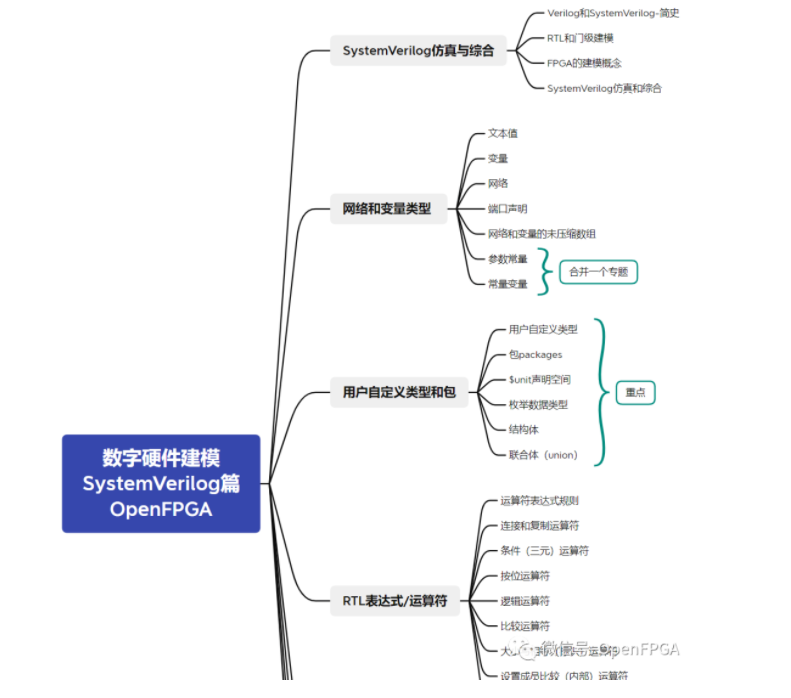

经过几周的更新,SV核心部分用户自定义类型和包内容已更新完毕,接下来就是RTL表达式和运算符。

移位运算符

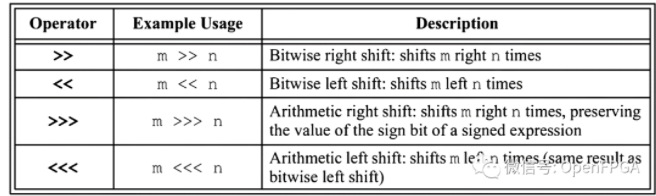

移位运算符将向量的位向右或向左移位指定的次数。SystemVerilog具有按位和算术移位运算符,如表5-18所示。

表5-18:RTL建模的移位运算符

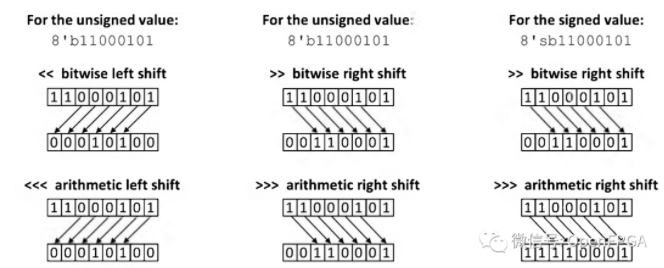

按位移位只是将向量的位向右或向左移动指定的次数,移出向量的位丢失。移入的新位是零填充的。例如,操作8’b11000101 << 2将产生值8’b00010100。按位移位将执行相同的操作,无论被移位的值是有符号的还是无符号的。

算术左移位对有符号和无符号表达式执行与按位右移位相同的操作。算术右移位对“无符号”和“有符号”表达式执行不同的运算。如果要移位的表达式是无符号的, 算术右移位的行为与按位右移相同,即用零填充输入位。如果表达式是有符号的,则算术右移将通过用符号位的值填充每个输入位来保持值的有符号性。

图5-11显示了这些移位操作如何将向量的位移动2位,

图5-11:按位和算术移位运算-将值向左或向右移动2位图5-11:按位和算术移位运算-将值向左或向右移动2位

可综合移位操作

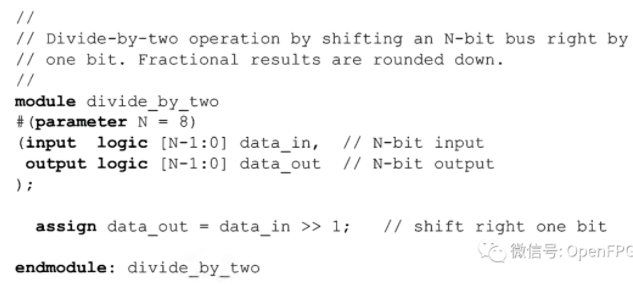

移动固定的次数。固定次数的移位操作只需将总线的位重新布线,“输入位”接地。实现固定移位不需要逻辑门。示例5-11说明了一个简单的除二组合逻辑模型,其中通过将8位总线右移一位来进行除法。

示例5-11:使用移位运算符:通过右移一位除以二

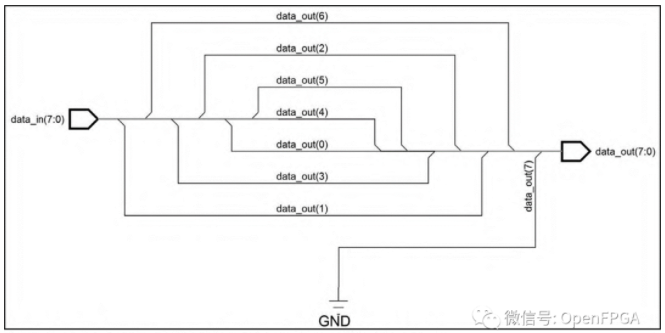

图5-12显示了固定位数的右移是如何综合的。综合编译器在模块的输入和输出上放置了缓冲区,但没有使用任何额外的门来执行操作。

图5-12:示例5-11的综合结果:移位运算符,按1位右移

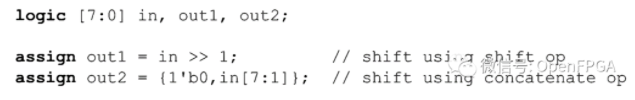

固定次数的移位也可以使用连接操作来表示。下面两行代码在功能上是相同的。

执行移位操作的两种类型都将综合为相同的布线硬件,一种类型没有优于另一种类型的优势。

移动次数可变。可变次数的移位操作代表是桶形移位器(barrel shifter)的功能,但具体实现将取决于特定目标库中可用的门级功能。一些目标设备可能有一个已经针对该设备进行了优化的预构建桶形移位器,其他设备可能需要综合以从较低级别的门构建桶形移位器。

桶形移位器的一个应用是用2的幂乘(向左移位)或除(向右移位)。例如,左移1位将值乘以2。左移2位将一个值乘以4。

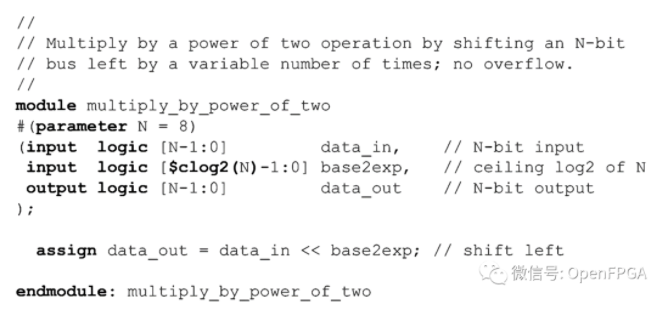

示例5-12显示了可变左移操作的代码

示例5-12:使用移位运算符:通过向左移位乘以二的幂

本例中的$ciog2系统函数用于计算base2exp输入端口的宽度。此函数用于返回一个log2值的的上限(分数向上舍入到下一个整数)。该函数是计算一个值需要多少位的便捷方法。

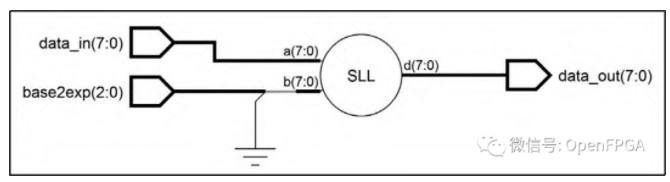

图5-13说明了该模型可能如何综合。该示意图是“在将移位功能映射并优化”到特定设备之前的“中间综合结果”。通用的“左移位逻辑”组件表示未映射的移位操作。

图5-13:综合结果“例如5-12:移位运算符,可变左移位”

综合结果中的通用左移分量对其两个输入具有相同的位数。base2exp输入未使用的高位与地相连。当综合将通用左移组件映射到特定的目标实现时,这些未使用的位可能会被删除。

移位运算符可用于乘以或除以除2的幂以外的值,以下示例将向量移动7次。

可以在硬件中使用cading shift实现非2次方的移位,例如,操作可以通过链接4位左移位器、2位左移位器和1位左移位器来完成7次左移位。

让综合器完成它的工作!综合使工程师能够在抽象层次上进行设计,专注于功能,而不必陷入实现细节的泥潭,也不必过度关注特定ASIC或FPGA的功能。综合编译器将抽象功能模型转换为目标ASIC或FPGA的有效实现。虽然可以在更详细的层面上仿真barrel shift行为,但这样做通常没有好处。现代综合编译器使用移位运算符识别抽象RTL模型中的barrel shift行为,并将在目标设备中生成此功能的最佳实现。对于不同的目标设备,这种实现可能会有所不同,具体取决于该设备中可用的标准单元、LUT或门阵列。

-

18_移位运算符 [001100000064] - 第1节 #硬声创作季充八万 2023-08-18

-

32 Java语言基础移位运算符 #硬声创作季充八万 2023-07-26

-

#硬声创作季 #基于FPGA的汽车应用系统开发 16 移位运算符醉 2022-12-14

-

#硬声创作季 #单片机应用 27 移位运算符醉 2022-12-08

-

C/C++中移位运算符的工作原理2022-07-28 1852

-

【梦翼师兄今日分享】 常见的关系运算符(移位运算符)2019-12-17 4893

-

数字设计FPGA应用:移位运算符2019-12-03 3941

-

移位运算符的应用实例讲解2019-11-19 4150

-

【FPGA】VHDL 语言的运算符有哪些?计算的优先级是怎样的?2018-09-12 11128

-

VHDL中移位运算符的实现之SLL使用2016-08-14 24892

-

炼狱传奇-移位和位拼运算符之战2015-04-30 3438

全部0条评论

快来发表一下你的评论吧 !