芯片堆叠技术在系统级封装SiP中的应用存?

描述

芯片堆叠技术在SiP中应用的非常普遍,通过芯片堆叠可以有效降低SiP基板的面积,缩小封装体积。目前来看,芯片堆叠的主要形式有四种:金字塔型堆叠,悬臂型堆叠,并排型堆叠,硅通孔TSV型堆叠。

为什么芯片可以进行堆叠呢?这里面我们讲的主要是未经过封装的裸芯片。曾经有用户问我,封装好的芯片可不可以进行堆叠呢?一般来说是不可以的,因为封装好的芯片引脚在下表面直接焊接到基板上,而裸芯片的引脚一般在芯片上表面,通过键合的方式连接到基板。正是由于裸芯片引脚在上方,和基板的连接方式比较灵活,才有了芯片堆叠的可行性,参看下图。

1 金字塔型堆叠

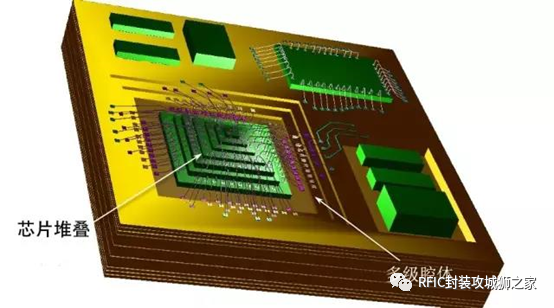

金字塔型堆叠是指裸芯片按照至下向上从大到小的方式进行堆叠,形状像金字塔一样,故名金字塔型堆叠,这种堆叠对层数没有明确的限制,需要注意的是堆叠的高度会受封装体的厚度限制,以及要考虑到堆叠中芯片的散热问题。金字塔型堆叠参看下图。

2 悬臂型堆叠

悬臂型堆叠是指裸芯片大小相等,甚至上面的芯片更大的堆叠方式,通常需要在芯片之间插入介质,用于垫高上层芯片,便于下层的键合线出线。这种堆叠对层数也没有明确的限制,同样需要注意的是堆叠的高度会受封装体的厚度限制,以及要考虑到堆叠中芯片的散热问题。悬臂型堆叠参看下图。

3 并排型堆叠

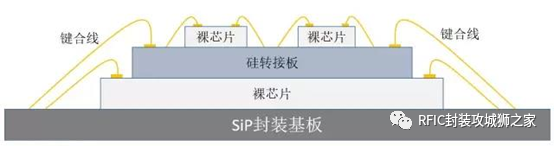

并排堆叠是指在一颗大的裸芯片上方堆叠多个小的裸芯片,因为上方小的裸芯片内侧无法直接键合到SiP封装基板,所以通常在大的裸芯片上方插入一块硅转接板,小的裸芯片并排堆叠在硅转接板上,通过键合线连接到硅转接板,硅转接板上会进行布线,打孔,将信号连接到硅转接板边沿,然后再通过键合线连接到SiP封装基板。并排型堆叠参看下图。

4 硅通孔TSV型堆叠

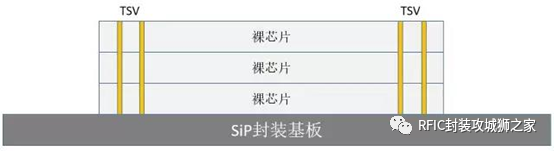

硅通孔TSV型堆叠一般是指将相同的芯片通过硅通孔TSV进行电气连接,这种技术对工艺要求较高,需要对芯片内部的电路和结构有充分的了解,因为毕竟要在芯片上打孔,一不小心就会损坏内部电路。这种堆叠方式在存储领域应用比较广泛,通过同类存储芯片的堆叠提高存储容量。目前也有将不同类芯片通过TSV连接,这类芯片需要专门设计才可以进行堆叠。TSV型堆叠参看下图。

上面介绍的是SiP设计中四种最基本的芯片堆叠方式。

在实际应用的时候,这几种堆叠方式可以组合起来形成更为复杂的堆叠。另外,还有通过将键合芯片和倒装焊芯片进行堆叠,通过柔性电路折叠的方式对芯片进行堆叠,以及通过POP形式的堆叠等几种,这些芯片堆叠方式在SiP设计中也比较常见。

审核编辑 :李倩

-

系统级封装技术解析2025-08-05 2660

-

一文详解多芯片堆叠技术2025-04-12 3294

-

SIP封装技术:引领电子封装新革命!2025-01-15 3792

-

系统级封装(SiP)技术介绍2024-11-26 3459

-

SiP系统级封装、SOC芯片和合封芯片主要区别!合封和sip一样吗?2023-11-24 2128

-

系统级封装(SIP)简介2023-05-19 6587

-

什么是系统级封装(SiP)技术?2023-02-10 3642

-

SiP系统级封装设计仿真技术2022-08-29 1264

-

系统级封装SiP在PCB的设计优势2022-08-09 2864

-

芯片堆叠的主要形式2020-11-27 4776

-

SiP的11个误区盘点2020-08-06 3138

-

SIP系统封装技术浅析2020-05-28 3688

-

系统级封装(SiP)的发展前景(上)2018-08-23 4396

-

一文看懂SiP封装技术2017-09-18 4876

全部0条评论

快来发表一下你的评论吧 !