MOS晶体管的静态特性(一)

模拟技术

描述

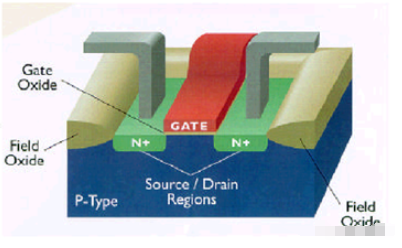

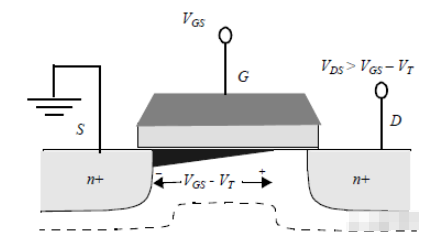

目前MOSFET仍是数字集成电路广泛使用的器件,根据MOS管的静态模型,以NMOS为例,分析其电流电压特性。 器件部分涉及到很多半导体物理、器件物理相关知识,暂不深入探究,MOS管的基本结构如图所示。

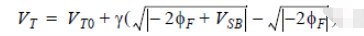

<阈值电压>

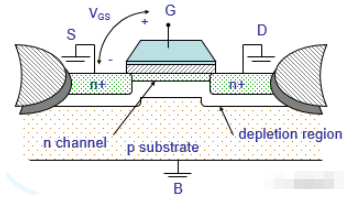

MOS管强反型发生时VGS的值称为阈值电压VT。

强反型的发生:假设源、漏均接地,当栅电压开始为正时,与SiO2接触的硅表面多子(空穴)减少; 当栅电压升高,空间电荷区(也称耗尽层)开始出现; 栅电压继续升高到硅表面的电势达到临界值,出现强反型,发生的电压等于两倍的费米电势。

不同偏置条件下的阈值电压:

参数γ称为体效应(衬偏效应)系数,表明V某人的影响。 说明一点,源、漏极取决于两边电压的高低,在反型后多子流出的称为源极(Source),流入的称为漏极(Drain)。

<电阻工作区>

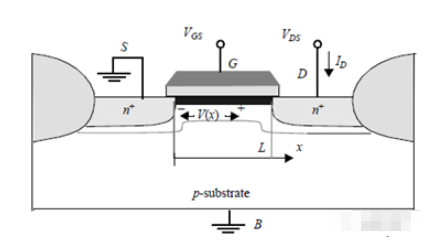

假设V 一般事务人员 >V T ,在漏区和源区之间加上一个小电压V DS 。

在沟道的x处,电压为V(x),栅至沟道的电压为V 一般事务人员 -V(x)。 处于电阻工作区,电压在整个沟道超过了阈值电压,x点所感应出单位面积沟道电荷:

Qi(x) = –Cox [VGS – V(x) – VT]

式中,C牛为栅氧的单位面积电容。

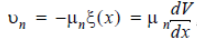

电流是载流子的漂移速度un与存在电荷的乘积:

ID = –a(x)Qi(x)W

式中,W是垂直于电流方向的沟道宽度。 电子通过的速度与迁移率的参数mn和电场相关。

所以,联合上面两式,可以得出:

IDdx = unCoxW(VGS–V – VT)dV

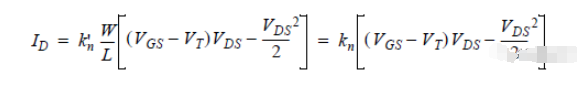

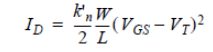

MOS晶体管的输出电流-电压特性的经典萨氏方程:

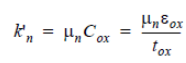

kn'称为工艺跨导参数,为:

当VDS值的值较小时,平方项可忽略,VDS和ID之间呈线性关系。

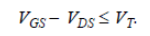

<饱和区>

漏源电压进一步提高时,沟道全长中的部分电压可能出现小于阈值电压的情况:

此时导电沟道开始出现夹断的现象,晶体管处于饱和区。 此时沟道上的夹断点到源的电压差固定为VGS-VT,电流保持稳定值(饱和),漏电流与控制电压VGS之间存在平方关系:

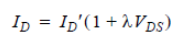

沟道长度调制:在饱和模式下,增加VDS将使漏结的耗尽区加大,缩短了有效沟道的长度。

λ称为沟长调制系数,一般与沟长成反比。

-

CB晶体管的特性曲线解析2024-05-05 3161

-

什么是晶体管 晶体管的分类及主要参数2023-02-03 2620

-

概述晶体管2019-05-05 2866

-

MOS晶体管的应用2019-04-19 9137

-

双极晶体管的静态工作特性2018-09-04 10002

-

MOS晶体管等效电路的电学特性的的PSPICE仿真该如何去做?2014-05-07 5506

-

晶体管的结构特性2013-08-17 3875

-

电力晶体管的基本特性和主要参数有哪些?2010-03-05 3304

-

N沟MOS晶体管2009-11-09 2727

-

电力晶体管的基本特性2009-11-05 1879

全部0条评论

快来发表一下你的评论吧 !