浅谈MOS管的二阶效应

模拟技术

描述

阈值变化

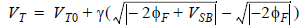

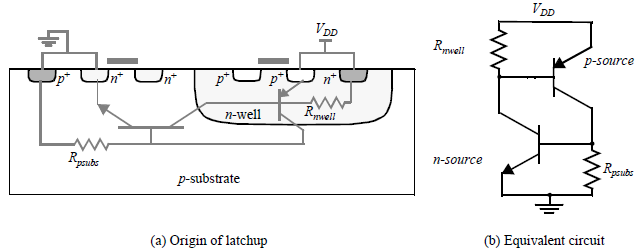

由阈值电压的公式可看出,阈值电压与制造工艺和所加体偏电压VSB有关,所以在设计中把它当成一个常数。 当器件尺寸不断缩小时,此模型不再精确,阈值电压与L、W和VDS有关。

对于图a:通常推导VT0时,假定沟道耗尽区由于所加的栅电压引起的,而忽略了源端和漏端的耗尽区,当沟长缩小时,一个较小的电压足以引起强反型。 所以短沟道期间的VT0随L的减小而减小。

对于图b:通过增加漏-源电压也可得到类似的效应,因为增加了漏结耗尽区的宽度,结果随着电压的增加而降低。

热载流子效应

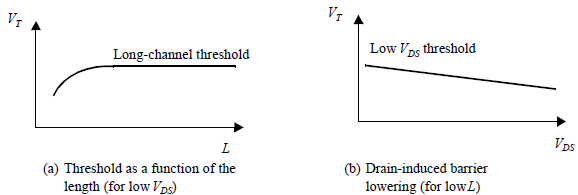

短沟道器件的阈值电压除了设计的偏差之外,也会随时间漂移,这由于热载流子效应的影响。 对于不断缩小的沟道长度,电源工作电压没有大幅下降,使得电场强度逐渐变高,电子的速度增加,达到一定的能量就会离开硅进入栅氧中,引起可靠性问题。

图中显示了NMOS管经过超强度工作前后对比,工作后(虚线)IV特性变差。 所以先进的MOSFET工艺采用一种特别设计的漏区和源区,保证电场的峰值受到限制,避免载流子变成热电子所需的临界值。

CMOS闩锁效应

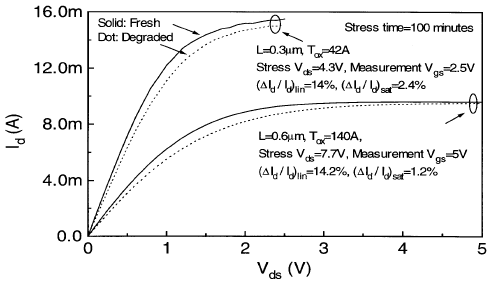

MOS工艺会包含很多内在的双极型管,阱和衬底之间会寄生n-p-n-p的结构。 这些期间一旦激发会导致VDD和VSS之间短路,破坏芯片。

如图(a)中,纵向形成了PNP双极型,横向形成了NPN双极型。 这样就形成了(b)中的正反馈回路,两个双极型的一个正向偏置,就会为另一个提供基级电流,此时及时外界触发条件消失,VDD和VSS之间也会有电流流动。

解决的办法有很多种,书中提供两种:1.使电阻Rnwell和Rpsubs最小,应该是使发射极和基级的电压接近,从而抑制BJT的导通条件之一的发射结正偏。 2.在传送大电流的器件周围加保护环,这些放置在晶体管周围的环形阱/衬底接触可以进一步减小电阻,从而减小寄生双极型管的增益。

-

浅谈HDI同位二阶的实现方式2024-11-27 3667

-

MOS管的基本结构 MOS管的二级效应2023-10-02 8080

-

求大佬明示二阶效应具体是什么?匹配规则要怎么改?2021-06-22 1739

-

一阶电路和二阶电路的时域分析详细资料概述免费下载2018-07-25 1662

-

二阶有源低通滤波器_最简单的二阶低通滤波器电路图2017-07-24 235334

-

二阶有源滤波器的传输函数2010-05-23 20740

-

二阶电路的零输入响应2009-07-27 11121

-

二阶低通滤波电路2009-07-01 2228

-

二阶网络特性测量2009-05-10 5812

-

二阶电路的响应2008-12-22 1164

-

二阶系统的时域响应2008-09-24 4415

全部0条评论

快来发表一下你的评论吧 !