解密首款国产PCB及封装设计平台

描述

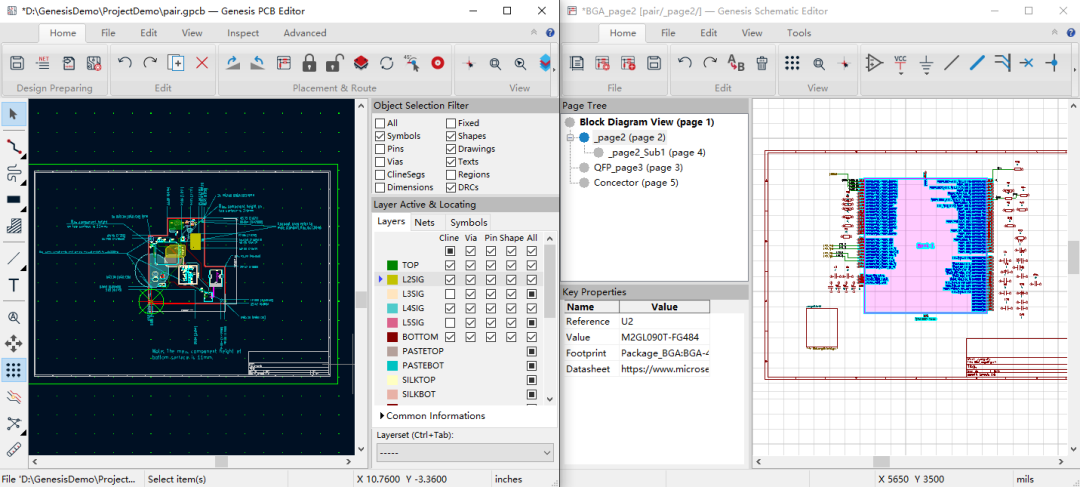

国产EDA行业的领军企业芯和半导体近期发布了全新板级电子设计EDA平台Genesis,这是国内首款仿真驱动设计的PCB及封装设计平台。

Genesis应用背景

电子产业在摩尔定律的驱动下,产品的功能越来越强,集成度越来越高,信号的速率越来越快,产品的研发周期也越来越短。后摩尔时代,集成电路工艺和封装技术高速发展,基于先进封装技术的异构集成,进一步推动电子系统设计向高频,高密,高集成方向发展。在系统模块化,定制化设计需求的驱动下,PCB和基板类产品的设计研发面临跨尺寸工艺,多领域电气拓扑,物理布局布线规则的设置与检查,和多平台,多轮次迭代仿真等难题,同时面向系统级的电热协同设计分析的需求也越来越强烈。

作为电子系统中最重要的一部分,PCB设计不仅仅要完成元器件间的线路连接,更要考虑高速、高密,以及电热,电磁等领域设计电气规则的正确性,以及约束设置,复用和检查,也要应对PCBA物理可制造性带来的各种工艺挑战。

Genesis是一款面向封装和PCB板级系统设计的产品,它集成了多层级跨尺寸设计功能,支持器件选型和建库,原理图设计和PCB设计全流程。完整的设计流程满足封装,基板,PCB等不同大小尺寸规模的设计要求;此外,Genesis是业界首款基于“仿真驱动设计”理念的板级系统设计软件,集成芯和自有仿真能力在设计前-中-后不同流程的协同分析,提前将系统电、磁和热仿真等问题识别和解决在设计初期,实现面向系统的完整仿真设计一体化解决方案,提高产品研发效率。

Genesis产品介绍

Genesis作为面向板级设计平台的设计工具,重点优化高频设计场景效率和工具易用性。统一的界面设计语言和交互逻辑,降低了用户入门成本;另外,相比传统工具,Genesis完整的设计流程,在典型设计场景的交互优化,对关键电气部件的仿真分析对减少设计迭代,指导设计正确性具有很大的优势。目前有项目管理,原理图设计,PCB设计等核心功能,同时包含设计所需的原理图符号,封装库设计模块。

Genesis产品特色

便捷的工程数据管理,快速实现项目网表,BOM,光绘,DFM,仿真等常见输入,输出数据的分类过滤,归档,以及设计库路径统一管理,并支持根据公司自有产品场景进行灵活定制化。

布局,布线阶段,支持从参考设计直接通过拷贝粘贴,自动抓取,旋转等方式实现设计布局布线快速复用,相对于传统工具复杂的导入导出流程更便捷。

设计环境下,支持按参考层,孔,焊盘,铜箔,走线等同类特征的显示和隐藏切换。结合过滤器和鼠标选择,快捷键操作实现高效检视和编辑操作。

支持通过封装名,器件值,自定义关键属性的自动同步;驱动符号库与原理图,封装库与PCB设计环境下设计内编辑和协同优化。

主要功能场景

支持导入Allegro *.brd和AD *.pcbdoc格式的存量设计数据

支持常见的一单元和多单元原理图Symbol设计

支持通过已有原理图符号库进行快速检索和复用,

通过导入模板快速进行多管脚编辑,并支持封装,规格和自定义属性设置

支持从单页简单和多页复杂层次化电路原理图的绘制

支持方便快捷的模块化原理图定义和灵活的端口及连接

支持一键式网表和BOM数据导出

快速分页模块和交互高亮定位

支持常见标准,非标准封装焊盘定义以及封装的快速检索,复用和参数化设计

支持封装管脚脚序参数化重排

支持常见的草图编辑功能

支持第三方网表和结构DXF文件导入

支持原理图分页布局,通过自动抓取的方式完成摆放,支持器件快速跳转,对齐,排列等检视和器件布局功能

支持单端,差分走线和参数化等长功能

支持常见对象类型的规则矩阵设置以及DRC开关

支持针对过孔,焊盘,走线,铜箔导体特征,以及设计常用参考层的分层激活和隐藏显示开关

支持DRC更新和定位,支持测量验证间距规则

支持网络铺铜,以及刷新,避让,跨层拷贝等功能

支持PCB光绘,钻孔,IPC,DXF,IDF等生产制造文件的导出

支持设计信息统计和网络走线长度统计功能

支持通过封装名,器件值,自定义关键属性在PCB和原理图间同步

支持在符号库与原理图,封装库与PCB设计环境下设计内编辑和协同优化

审核编辑 :李倩

-

MUN12AD03-SEC的封装设计对散热有何影响?2025-05-19 3339

-

为什么需要封装设计?封装设计做什么?2024-04-16 1598

-

为什么需要封装设计?2023-03-15 1285

-

【免费资料】《PCB封装设计指导白皮书》,封装实战大全,你值得拥有!2023-01-11 2465

-

PCB封装设计难点讲解和实战案例教程2023-01-04 3398

-

【限时免费】《PCB封装设计指导白皮书》携全套最新“封装实战课程”再度来袭!2022-12-15 3334

-

PCB封装设计步骤PPT课件下载2021-09-02 3983

-

IC封装设计的五款软件2020-07-13 24255

-

Intel宣布首款基于Foveros混合封装的笔记本移动平台的Lakefield2019-01-08 729

-

PCB元件封装设计规范2016-01-14 1375

-

cadence15.2PCB封装设计自我小结2011-07-05 3970

-

cadence15.2PCB封装设计小结2010-04-05 852

全部0条评论

快来发表一下你的评论吧 !