SiC MOSFET的结构及特性

模拟技术

描述

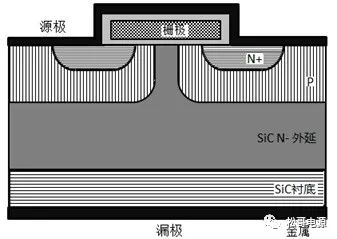

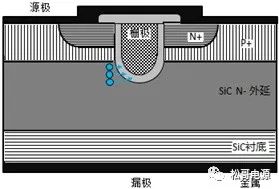

SiC功率MOSFET内部晶胞单元的结构,主要有二种:平面结构和沟槽结构。平面SiC MOSFET的结构,如图1所示。这种结构的特点是工艺简单,单元的一致性较好,雪崩能量比较高。但是,这种结构的中间,N区夹在两个P区域之间,当电流被限制在靠近P体区域的狭窄的N区中流过时,将产生JFET效应,从而增加通态电阻;同时,这种结构的寄生电容也较大。

图1:平面SiC MOSFET的结构

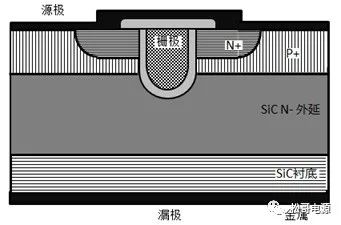

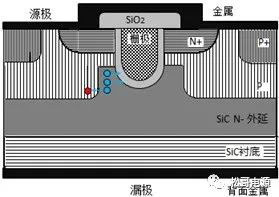

沟槽SiC MOSFET的结构,如图2所示。这种结构将栅极埋入基体中,形成垂直的沟道,由于要开沟槽,工艺变得复杂,单元的一致性、雪崩能量比平面结构差。但是,由于这种结构可以增加单元密度,没有JFET效应,沟道晶面实现最佳的沟道迁移率,导通电阻比平面结构要明显的降低;同时,寄生电容更小,开关速度快,开关损耗非常低,因此,新一代的结构都研究和采用这种结构。

图2:沟槽SiC MOSFET的结构

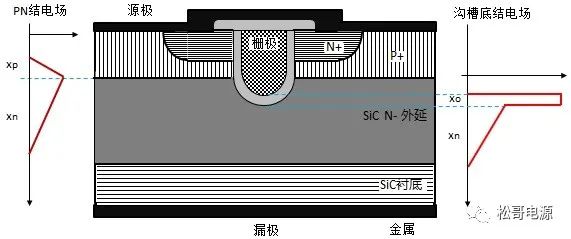

沟槽结构SiC MOSFET最主要的问题在于,由于器件工作在高压状态,内部的工作电场强度高,尤其是沟槽底部,工作电场强度非常更高,很容易在局部超过最大的临界电场强度,从而产生局部的击穿,影响器件工作的可靠性,如图3所示。

图3:沟槽SiC MOSFET结构内部工作电场

因此,新一代的SiC MOSFET沟槽结构,技术演进的方向都是如何减小沟槽底部的工作电场强度,比如Rohm的双沟槽结构、Infineon的非对称沟槽结构,等等,如图4、图5所示。

图4:Rohm双沟槽结构

图5:Infineon非对称沟槽结构

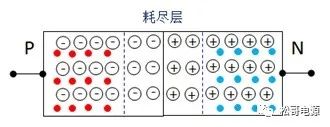

这些结构的核心就是或在 沟槽底部增加缓冲层 , 或把P区下移让P和沟槽底部的N区形成耗尽层 ,如图6、图7所示,从而把 沟槽底部氧化层的电场,部分转移到P区耗尽层,减小沟槽底部的电场 。

(a) P和N接触面形成耗尽层

(b) 沟槽下部电场线

(c) 双沟槽下部电场线

图6:减小沟槽底部工作电场示意图

图7:Infineon非对称沟槽结构内部电场分布(图片来源网络)

平面结构SiC MOSFET的基本工艺和各项成本占比,如图8、图9所示。可以看到,目前SiC晶体的衬底依然占非常大的比例,达到38%,如果加上SiC晶体的衬底的减薄和抛光工艺,比例高达50%以上。

其主要原因在于SiC生长的速慢,温度高,工艺复杂度,容易产生各种晶格缺陷。Si生长速度为100 mm/小时,最大直径450 mm, 最大厚度2 m;SiC生长的速度为100-300 um/小时,2100 °C,最大直径150mm,最大厚度50 mm。

外延工艺的成本占比为17%左右,封装成本的占比为11%左右;产品的良率导致的成本占比为21%。如何控制SiC MOSFET生产过程中产生的缺陷,提高生产过程中的良率,依然是各厂家需要面对的重要的问题,其不仅关系到产品的成本,更关系到产品在客户应用的可靠性。

图8:平面结构SiC MOSFET基本工艺

图9:平面结构SiC MOSFET工艺成本占比

-

SiC MOSFET的静态特性2025-03-12 1981

-

SiC MOSFET的参数特性2025-02-02 3466

-

SiC MOSFET的桥式结构2023-12-07 1373

-

SiC-MOSFET和功率晶体管的结构与特征比较2023-02-08 1411

-

SiC-MOSFET器件结构和特征2023-02-07 1573

-

SiC MOSFET的特性及使用的好处2021-08-13 8892

-

浅析SiC-MOSFET2019-09-17 6420

-

SiC功率器件SiC-MOSFET的特点2019-05-07 5700

-

SiC-MOSFET有什么优点2019-04-09 4690

-

沟槽结构SiC-MOSFET与实际产品2018-12-05 4847

-

SiC-MOSFET与Si-MOSFET的区别2018-11-30 11054

-

SiC-MOSFET的应用实例2018-11-27 6069

全部0条评论

快来发表一下你的评论吧 !