MOSFET的结构、电学符号和电学特性

模拟技术

描述

为什么要学MOSFET?

现在所有电子产品中的芯片、放大器中的基本结构就是MOSFET,学好MOSFET是理解这些芯片、放大电路的前提。

学习MOSFET之前需要具备哪些知识?

基本电路的电路知识包括:电阻、电容、电感的知识、KCL、KVL、戴维南等效电路、诺顿等效电路等。

全文内容:

MOSFET的结构

MOSFET的电学符号和电学特性

1、MOSFET的结构

MOSFET的名字就反应了本文要讲的内容:M-Metal-导体,O-Oxide-氧化物(绝缘体),S-Semiconductor-半导体,F-Field,E-Effect,T-Transistor -场效应晶体管。 前三个字母反应了它的结构,MOSFET就是由导体-氧化物-半导体三层结构组成的器件,而后三个字母则反应了他的工作特性,它是一个感应电压的晶体管。

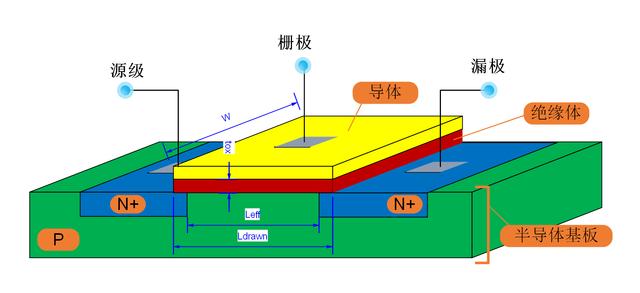

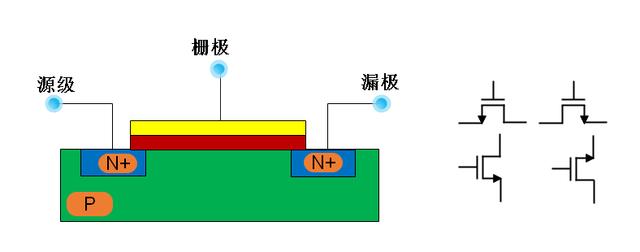

Fig. 1 MOSFET的结构

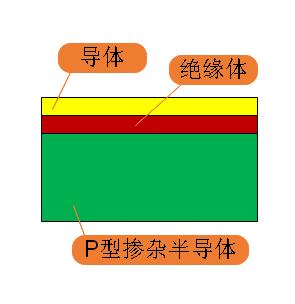

第一眼看到图Fig.1会感觉有些复杂,没关系不要紧,我们从简单的一点点来分析,首先看图Fig. 2,这是一个简单的我们假想的半导体器件,虽然是假想的,但是不妨碍我们对其原理进行理解。 这个我们意淫的器件同样是由导体、绝缘体、半导体三层结构组成,这个半导体是P型掺杂的还是N型掺杂的我们先不管,这里我们以P型掺杂的半导体为例。

Fig. 2 一个简单的假想的半导体器件

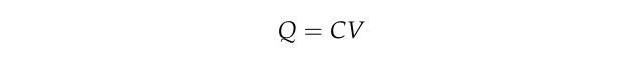

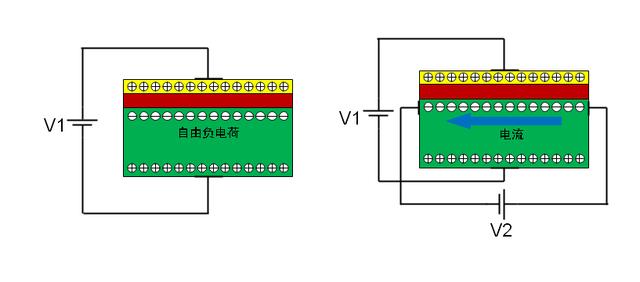

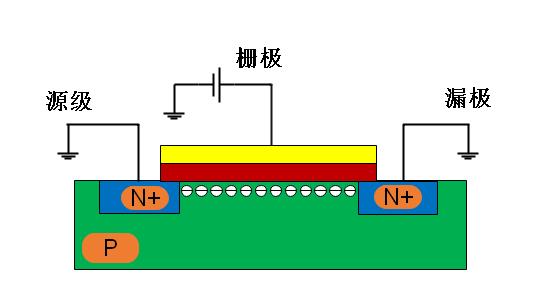

看Fig. 3左图,如果我们在导体和半导体两端加电压V1,因为有绝缘体在中间整个器件没有电流通过,但此时你有没有发现这个器件就是一个电容,导体和电源正极相连带正电荷,P型掺杂的半导体本来能用来导电的自由电子很少,但由于和电源负极相连,自由电子都聚集到和绝缘体相接的表面。 这个自由电荷聚集的区域我们称为沟道,此时,沟道中没有电流,只有电荷,其电荷数量为

Fig. 3 加电压

这里的V就是V1,C就是导体和半导体形成的电容,知道了这个原理,我们可以得到下面两点初步的认识:

①当V1变大,电荷数量Q变大,沟道中自由电荷的密度增大;

②当绝缘体的厚度t_ox下降,则电容C变大,电荷数量变大,沟道中自由电荷的密度增大。

看Fig. 3右图,当在沟道的两端加电压V2,因为沟道中本身存在可以自由移动的电子,此时在沟道中就形成了电流。 当V1增大时,电荷密度增加,导致沟道两端之间的电阻变小,导致电流增大。

有了上面的理论基础我们回过头来再看Fig. 1,是不是感觉亲切了很多,但是和Fig. 3图相比,Fig. 1有四点值得注意:

①该器件在下面的P型半导体基板上注入了两块重掺杂的N型半导体。 这是因为N型半导体能提供自由电子,对沟道中的电流传导有好处;

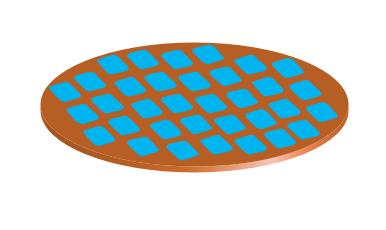

②所有的电压都是在上面加的,这是因为所有的MOSFET器件是做在晶圆上的,晶圆片的示意图如图Fig. 4,其中蓝色的小方格表示一个个小器件,所以,电压只能从上面加,不可能从侧边和下面加。

Fig. 4 晶圆片示意图

③Fig. 3有图有4个端口,即V1的两个端口和V2的两个端口,而Fig. 1只有源级S、漏极D和栅极G三个端口,这是因为习惯上把最下面的半导体基板作为参考电压为零,没有画出来。 而且受源级S、漏极D和栅极G三个端口电压的影响,沟道两边的电压是不均匀的,靠近源级一侧的电压为V_GS,而靠近漏极一侧的电压为V_GD。

④MOSFET器件是对称的,哪一端是源级,那一端是漏极呢? 对于Fig. 1的MOSFET(NMOS)来说,两个N型掺杂半导体上加电压低的一端是源级,这是因为NMOS靠电子导电,从电压低的一端流到电压高的一端,电压低的一端为电子的“源泉”。 (PMOS后面再讲)

2、MOSFET的电学符号和电学特性

① 电学符号

Fig. 5 左为物理结构,右为电学符号

Fig. 5中左图为MOSFET的物理结构,右图为其电学符号,这里我画了4个是为了无论这个符号在电路图中怎么摆放,大家都应该认识。 这里要大家特别注意的是:符号中的箭头不是栅极或漏极的标志,因为MOSFET是对称的,哪一端是漏极或栅极需要看所加电压的大小。 这里的箭头只是区别NMOS还是PMOS,NMOS箭头向外如图中所示,PMOS箭头向里(后面再讲)。 一个简单的记忆方法是,箭头总是从P型半导体指向N型半导体(和二极管的箭头类似)。

② 电学特性

研究一个器件最直接的一种方法就是在各个端口加电压,然后看看各个端口电流的一些性质,也就是研究该器件各个端口的伏安特性曲线。

Case I:如图Fig. 6,在MOSFET栅极加电压,V_G>0,V_S=V_D=0。 此时在沟道中聚集了电荷,电荷密度会随着V_G的增大而增大,但是没有电流。

图6 案例I

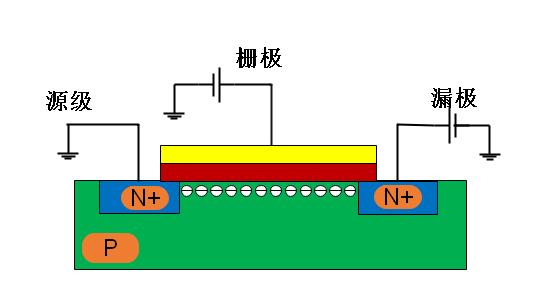

Case II:如图Fig. 7,在MOSFET栅极和漏极加电压,V_G>0,V_D>0,V_S=0。 此时,V_G试沟道聚集了电荷,当V_G>V_TH时,电荷数量聚集达到一定程度,再当V_D>0时,在电压的驱动下自由电荷运动形成电流。

图7 案例二

伏安特性:① 当V_G>V_TH为常数时,从直观上来看流过沟道的电流I_D随着V_D的增大而增大。 ② 当V_D为常数时,因为V_G越大,沟道中聚集的电子数量越多,相当于从沟道一端到另一端的电阻越小,那么从直观上来看流过沟道的电流I_D也会增大。

那具体I_D和V_G、V_D是什么关系呢? 线性关系还是非线性关系呢? 表达式是什么呢? 咱们下回分解。

-

TSV工艺流程与电学特性研究2022-06-16 4062

-

超薄SIMOX材料的Pseudo-MOSFET电学表征2010-04-24 1906

-

漫画电学原理2013-01-28 8260

-

数电学习资料2013-07-07 12121

-

如何入门电学?2014-03-29 3105

-

MOS晶体管等效电路的电学特性的的PSPICE仿真该如何去做?2014-05-07 5409

-

电机与机电学2020-05-22 2144

-

电学计算小程序2009-08-07 943

-

电阻和电容的基本电学特性2009-09-22 689

-

热敏电阻电学特性2010-01-14 751

-

电学计算工具2010-07-26 910

-

电学元件的伏安特性测量2010-10-06 1302

-

半导体器件热特性的电学法测量与分析2016-05-06 695

-

MOSFET的结构和电学特性小结2020-04-04 1981

-

关于MOSFET的结构和电学特性的总结2021-04-23 3985

全部0条评论

快来发表一下你的评论吧 !