模拟电路设计之MOSFET

模拟技术

描述

模拟电路设计之MOSFET

概念

MOSFET释义:

MOSFET即金属-氧化物-半导体场效应晶体管,其全称为METAL-OXIDE-SEMICONDUCTOR FIELD EFFECT TRANSISTOR,顾名思义,是利用电场效应去感应电荷的晶体管,它利用栅极电压去感应出反型层沟道,从而使电荷能够在沟道中移动,即“导通”。

MOSFET工作原理:

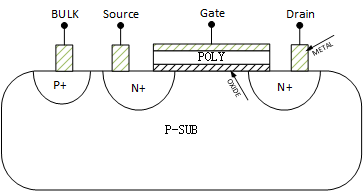

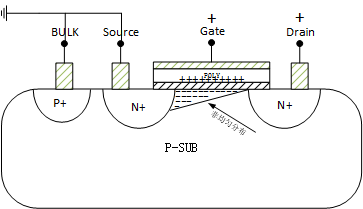

MOS管的工作原理用其剖面图来解释最为直观。

上图为N型MOS管的剖面图,可以看出这是一个四端器件,分别由栅极GATE,源极SOURCE,漏极DRAIN和体端BULK构成,其结构也比较简单,在P型衬底上通过离子注入等方法产生两个N阱,分别作为源极和漏极,上面再覆盖一层氧化层作为绝缘层,再通过腐蚀等方法将部分氧化层去除后在源极、漏极、栅极上垫积金属。

栅极和衬底由于绝缘层的存在而构成了栅极电容,在栅极未加正电压时,MOS管处于断开状态,即使源极和漏极之间存在压差,它们之间依然无电流流过; 当栅极加上正电压后,栅极电容上极板正电荷往下跑,下极板负电荷往上跑,而绝缘层的存在阻隔了这个行动,因此上极板累积正电荷,下极板感应出同样数量的负电荷,这些负电荷在源漏之间形成了一层耗尽区; 随着栅极电压的上升,源漏之间的负电荷累积得越来越多,当其浓度大于等于P衬底的掺杂浓度时,耗尽区就转变成了反型区,源漏之间能够通过反型层连接。 这个能够在产生反型层沟道的临界电压就是该MOS管的阈值电压(VTH); 以上描述针对的是N型MOS管,对于P型MOS管,衬底为N型,栅极电压应低于源极电压。 此时,若在源漏之间存在一定压差,就会有电流流过。

由于MOS管结构上的对称性,原则上其没有固定的源极和漏极,但对于P型MOS管来说,电流流入的一端为源极,电流流出的一端为漏极,衬底接电源; 对于N型MOS管来说,电流流入的一端为漏极,电流流出的一端为源极,衬底接地。 下面继续以N型MOS管为例进行分析。

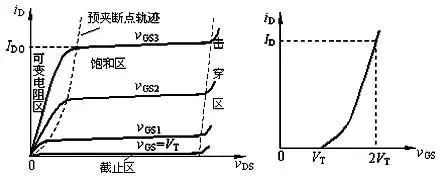

左图为在不同栅源电压VGS下,漏源电流iDS随漏源电压VDS变化的曲线图;右图为漏源电流iDS随栅源电压VGS变化的曲线图,此时漏源电压VDS为定值。从图中可以发现如下几个特性:

①当VGS较小时,MOS管处于截止区,无电流流过;

②iDS随VDS的增大先线性上升(线性区),再趋于平缓(饱和区);

③iDS随VGS的增大呈平方律上升;

下面对上述特性依次分析,让大家对MOS管有一个更全面的认识。首先是截止区,器件工作在截止区的主要原因是栅极电压太小了,还没能把栅极下方的耗尽区转换成反型区,也就是说源漏之间还是断开的,这就不可能有电流流过了。

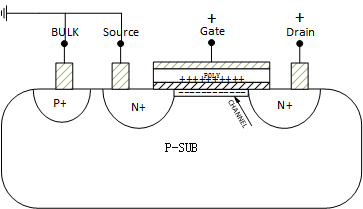

随着栅极电压的上升,当VGS电压到达阈值电压时,耗尽区终于变为反型区,源漏通过沟道连起来了,这时如果VDS还不大,器件就工作在线性区,如下图所示。

可以看出反型层是均匀分布的,均匀分布的反型层可以看作均匀电阻,从源极到漏极流过的电流是接近线性的,因此线性区又叫做可变电阻区,电阻的大小和VGS电压有关。

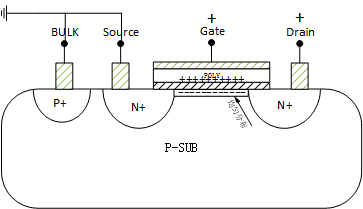

但随着VDS电压的增大,由于栅极和源极之间的压差会大于栅极和漏极之间的压差,因此反型层就会变得不均匀,如下图所示。

非均匀分布的反型层,就让器件慢慢进入了饱和区,因为随着VDS电压的上升,栅极和漏极之间就会因为压差的逐渐减小,而从反型区回到耗尽区,从而出现一个新的状态——夹断。夹断的出现正是保证电流恒定和区的关键,因为漏极电压过大而产生的耗尽区实际上是一个大电阻,此后VDS增加的电压都会分到这个大电阻上而不是反型层上,因此可以认为反型层上出现了恒压的状态,IDS电流也就基本恒定了。

此处插入一条公式:IDS=1/2*K'W/L(VGS-VTH)²,此处k'为工艺因子。

下面就可以根据上述过程推出MOS管进入饱和区的条件了,即VDG≤VTH,其中VGD为栅极和漏极的压差,VTH为MOS管开启的阈值电压,当VDG≤VTH器件就会出现夹断,也就是进入恒流的标志。将VDG≤VTH进行分解,就可以得到一个很经典的MOS管进入饱和区的条件公式:VDS>VGS-VTH。

那么,眼尖的童鞋们就会发现了,上面的ID/VDS图中,当MOS管进入饱和区后,电流并不是一条平的直线,还是微微上升的呀!这时候就需要给大家带来今天的第一个著名效应了,那就是沟道调制效应,沟道调制效应让进入饱和区的IDS电流受VDS影响而变得不恒流。随着VDS电压的上升,耗尽区其实是不断扩大的,这就让反型层的实际长度变短了,毕竟器件的沟道长度也就只有L那么长。因此,为了让器件的恒流做的更好,会考虑把MOS管的沟道长度L做长些,这样耗尽区变长带来的影响就会减小了。

此处插入一条公式:

IDS=1/2K'(VGS-VTH)²W/[L(1-λVDS)]

=1/2K'W/L(VGS-VTH)²(1+λVDS)

=1/2K'W/L(VGS-VTH)²(1+VDS/VA),此处VA为著名的厄利电压,VA越大说明器件的恒流特性越好。

除了沟道调制效应,还有一个很出名的效应就是——衬底偏置效应,这个效应是说假设衬底和源极不是一个电位的,这个状态是很容易出现的,因为通常同一工艺中器件的衬底都是接一块的,比如一般NMOS管的衬底都接在地上,这时如果源极电位比衬底电位高的话,源极和衬底首先就反偏了,在沟道里先感应了点负电荷; 我们上面也说过,栅极和衬底构成了栅电容,下极板先感应了负电荷,那上极板需要感应相应的正电荷才行,因此衬底偏置效应会让阈值电压变高,也就是需要更大的VGS电压才能让MOS管开启。

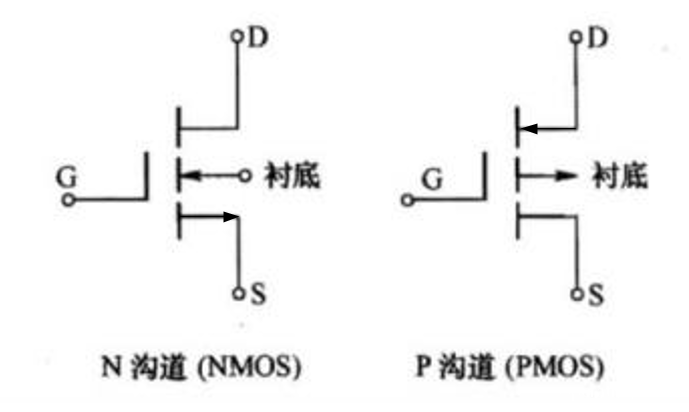

最后我们来看看NMOS和PMOS的符号吧。

还有一种栅极画圈圈的我就不画了,圈圈代表低电平有效,栅极有圈圈的是PMOS,栅极没有圈圈的是NMOS。

-

实用模拟电路设计技术Section92022-07-11 564

-

MOSFET管经典驱动电路设计总结2021-12-17 1660

-

功率MOSFET的驱动电路设计论文2021-11-22 3023

-

功率MOSFET应用研究及主电路设计2021-03-22 1278

-

实用模拟电路设计技术Section22017-03-01 865

-

电路设计中的模拟地与数字地2016-10-10 1435

-

MOSFET驱动电路设计参考2016-06-21 12023

-

MOSFET管开关电路设计2015-12-23 2004

-

MOSFET管经典驱动电路设计大全2012-08-06 17100

-

模拟电源电路设计资料(经典)2010-01-04 1248

-

低电压模拟电路设计技巧-使用基底输入式晶体管2009-10-05 3532

全部0条评论

快来发表一下你的评论吧 !