CS5518 DSI转LVDS方案设计

电子说

描述

TC358764XBG方案|TC358764XBG替代方案|CS5518 DSI转LVDS方案设计

TC358764XBG该芯片的主要功能是DSI到LVDS桥,通过DSI链路实现视频流输出,以驱动LVDS兼容的显示面板。该芯片支持单链路LVDS高达1600×1200 24位/像素分辨率,双链路LVDS最高支持WUXGA(1920×1200 24比特像素)分辨率。作为次要功能,该芯片还支持由DSI链路控制的I2C主机;这可以通过I2C用作任何其他控制功能的接口。

TC358764XBG:在BGA49封装中,它支持多达4条数据通道的DSI-RX,并输出到单链路LVDS。

CS5518 封装方式是QFN48封装,CS5518既可以设计单链LVDS转换输出,也可以双链路LVDS输出。

综上所示:

TC358764XBG方案芯片封装较大,外围器件较多,设计方案较为复杂,整体方案BOM成本较高。

CS5518可以替代兼容TC358764XBG方案,芯片封装管脚为QFN48,芯片封装较小,CS5518芯片集成度较高,外围器件较少且设计简单,整体方案成本比TC358764XBG方案要低。

CS55518

特征

● CS55518 DSI接收器

可配置1-最多4个数据通道DSI链路,在数据通道0上提供双向支持

最大比特率为800 Mbps/通道

视频输入数据格式:

-RGB565每像素16位

-RGB666每像素18位

-RGB666每像素松散压缩24位

-RGB888每像素24位。视频帧大小:

单链路LVDS显示面板分辨率高达1366×768 24位/像素-双链路LVDS显示屏分辨率高达WUXGA(1920×1200 18位像素)支持视频数据传输的视频流数据包。

支持用于访问芯片寄存器集的通用长数据包²

支持主机控制片上I2C主机的路径

● CS55518 LVDS FPD链路发射机

支持单链路或双链路

最大像素时钟频率85 MHz

单链路的最大吞吐量为297.5 MB/秒,双链路的最大吞吐率为595 MB/秒

单链路最高支持1366×768 24位/像素分辨率,双链路最高支持WUXGA(18位/像素)分辨率

支持以下像素格式:-RGB666每像素18位-RGB888每像素24位

采用Magic Square算法,使RGB666显示面板能够产生与RGB888 24位面板相当的显示质量

并行数据输入位排序的灵活映射

支持可编程时钟极性

支持断电

CS5518内置MCU控制系统操作

主机通过DSI链路配置芯片

通过DSI链接,主机使用通用写入和读取数据包访问芯片寄存器集。一个通用长写数据包可以写入多个连续的寄存器地址

包括由主机通过DSI链路控制的I 2 C主功能(不支持多主功能)

省电的电源管理功能

配置寄存器也可通过I2C从接口访问

综上所示:CS5518在功能特性上跟TC358764XBG方案一致,是可以完全替代兼容TC358764XBG方案,TC358764XBG方案是DSI转LVDS单链路转换芯片,CS5518既可以设计DSI转LVDS单链路方案,也可以设计DSI转LVDS双链路方案。

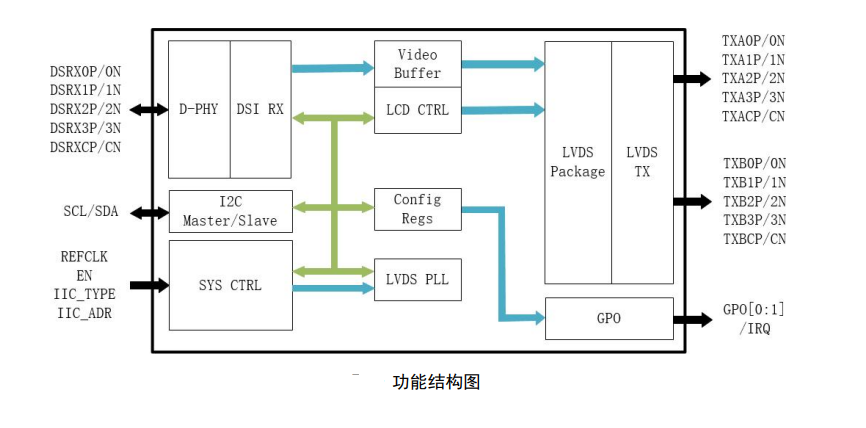

CS5518替代TC358764XBG设计DSI转LVDS转换方案结构框图如下所示:

CS5518结构功能框图

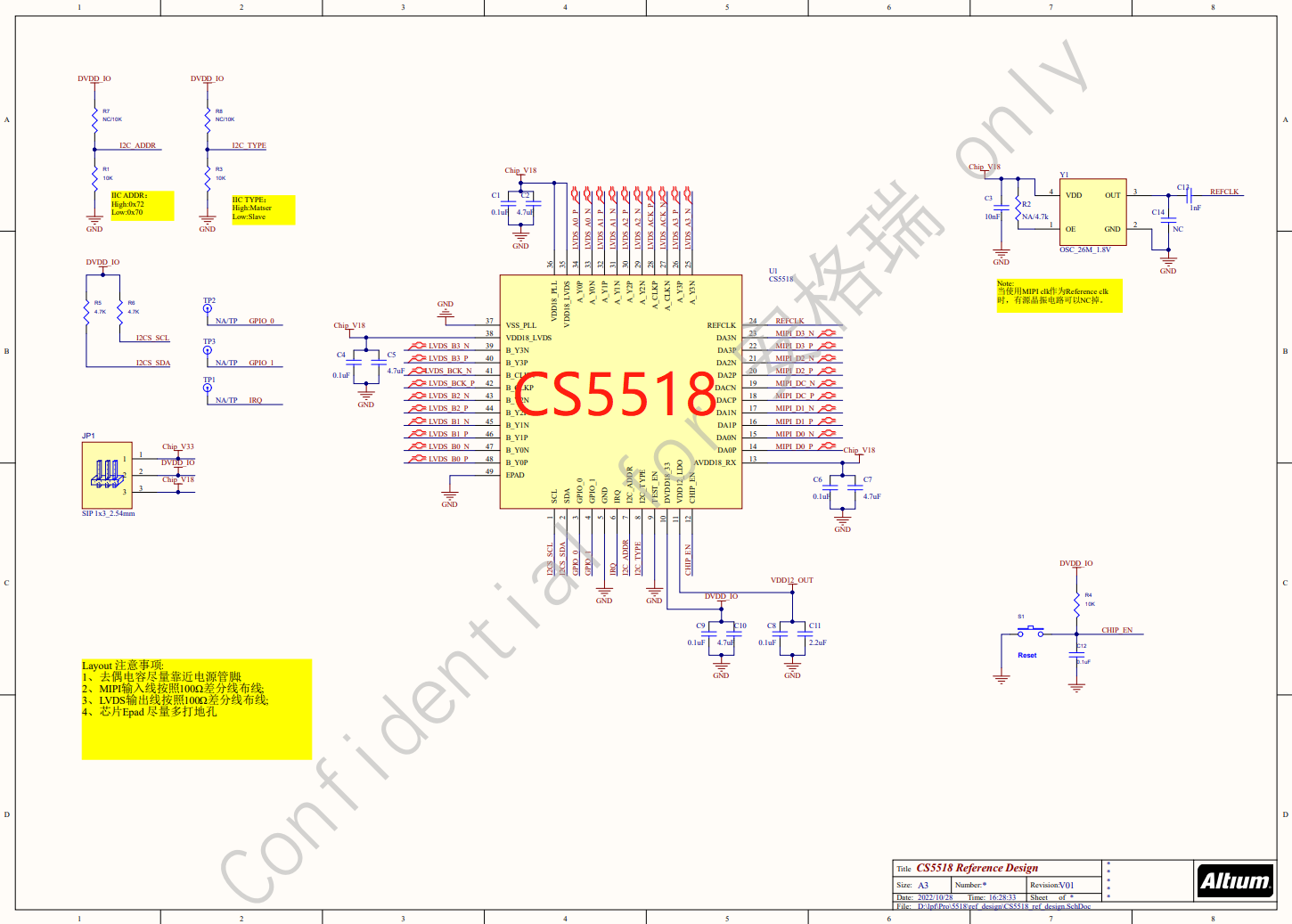

CS5518替代TC358764XBG设计DSI转LVDS转换方案电路原理图如下所:

审核编辑 黄宇

-

SN65DSI84 MIPI DSI桥转FLATlink™ LVDS单通道DSI转双链路LVDS桥接器数据表2024-07-03 639

-

CS5311集睿致远EDP转LVDS屏转接板芯片数据手册2023-08-30 1106

-

MIPI转双通道LVDS CS5518芯片,可pin to pin替代国腾GM8775C2023-02-14 2362

-

CS5518 mipi to lvds开发资料分享2023-01-31 775

-

MIPI转LVDS转换方案芯片CS55182023-01-11 2114

-

CS5518/MIPI转LVDS转换方案芯片2022-12-30 963

-

完美替代GM8775C方案芯片 DSI转双通道LVDS转换方案CS5518|CS5518替代GM8775C设计资料2022-12-14 5429

-

双通道LVDS转换器芯片CS5518手册2022-12-12 839

-

CS5518规格书|CS5518最新版说明书|MIPI DSI转LVDS方案2022-12-10 1351

-

CS5518芯片规格书|MIPI转LVDS转换方案芯片|DSI转LVDS转换方案芯片2022-12-09 2445

-

MIPI解决方案 ICN6202:MIPI DSI转LVDS转换芯片2022-11-15 2682

-

MIPI DSI&eDP转1/2Port LVDS专版介绍2022-11-12 1447

-

CS5518概述 支持视频格式 FULL HD MIPI转LVDS替换国腾GM87752022-06-24 2824

全部0条评论

快来发表一下你的评论吧 !