SiC FET导通电阻随温度变化

模拟技术

描述

比较SiC开关的数据手册可能很困难。SiC MOSFET在导通电阻温度系数较低的情况下似乎具有优势,但与UnitedSiC FET相比,这表明潜在的损耗更高,整体效率低下。

正如谚语所说,“比较是可憎的”,最早记录在1440年左右的约翰·利德盖特(John Lydgate)的“马,鹅和羊之间的辩论”中。除了牲畜之外,现代电源转换器的设计人员必须尝试冷静地将电源开关与其应用进行比较,并提出一系列相互竞争的“最佳性能”主张。问题是将苹果与苹果进行比较,继续农业的比喻,因为如果不考虑与其他措施的权衡,就不能说任何单一的电气参数更好。开关导通电阻就是一个很好的例子 – 您必须比较具有相同额定电压、制造商推荐的栅极驱动电压、相同结温和漏极电流以及相同封装的器件。

Si-MOSFET、SiC-MOSFET 和 SiC FETS 争夺位置

在更高的电压下,从几百伏以上,Si MOSFET、SiC MOSFET和UnitedSiC FET正在争夺位置,数据手册通常给出RDS(ON)特定额定电压、结温和栅极驱动电压下的值。例如,UnitedSiC最近发布的UJ4C075018K4S部件给出了V的导通电阻值一般事务人员= 12V,在25°C至175°C时,均在20A漏极电流下。由此,您可以轻松得出温度系数R的数字DS(ON)在给定的温度下,该部分在Tj = 70C时约为+75-125%。

650V SiC MOSFET的拥护者可能会指出,对于其他类似器件,他们在Tj = 20C时看到的数字通常为+25-125%。这是三倍好吗?首先,需要温度系数的正值来迫使芯片中的电池共享电流而没有热点和热失控。同样,设计人员依靠正值来并联具有自然均流的器件。

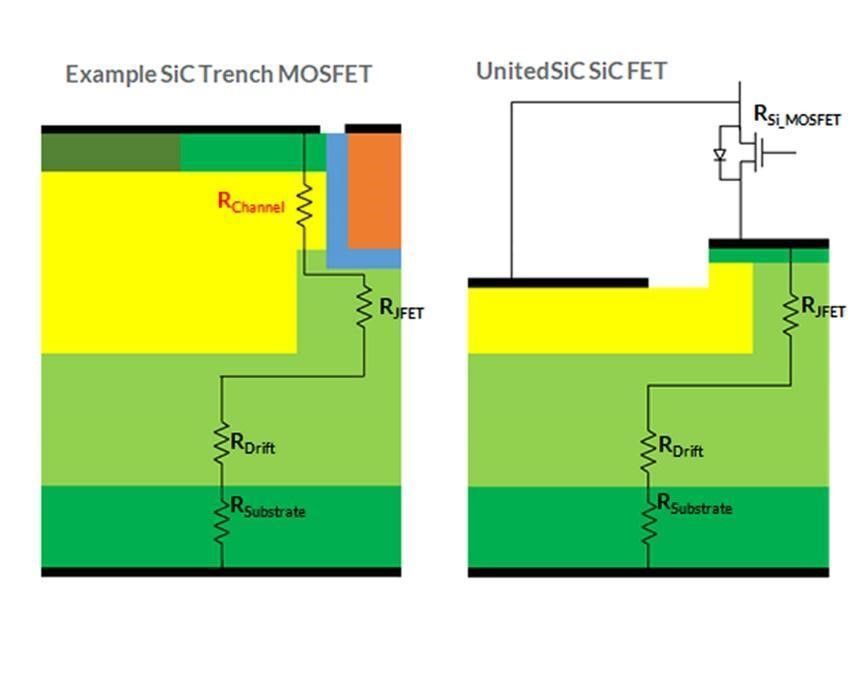

碳化硅 MOSFET 电阻主要由其反转通道主导

R 的较低值DS(ON)SiC MOSFET的温度系数实际上表明正在发生的更深层次的影响;MOSFET和JFET是“单载流子”器件,其电子流过不同的区域 - 衬底,漂移层,JFET区域和通道等。在 650V SiC MOSFET 中,逆温通道主导总电阻,而总电阻实际上随温度降低。通道电阻与(自由载流子数x电子逆温层迁移率)成反比,随着温度的升高,阈值电压降低,通道中自由载流子的数量增加,因此电阻减小。该效应被器件其余区域的正温度系数(即JFET、漂移层和基板电阻)抵消,以产生轻微的净正Tc值。在碳化硅JFET中,没有反转通道来抵消JFET、漂移层和基板的正温度系数。同时,低压 Si MOSFET 仅占总导通电阻的一小部分,这解释了比 SiC MOSFET 更高的 Tc 值,但最明显的一点是,与非理想 SiC 反转层相关的损耗在 SiC FET 中也不存在(图 1)。

图 1:典型的 SiC MOSFET 沟槽结构和 UnitedSiC FET 显示不存在有损耗 SiC MOS 反转通道,导致导通电阻温度系数更高,但损耗更低

碳化硅场效应晶体管具有较低的总导通损耗

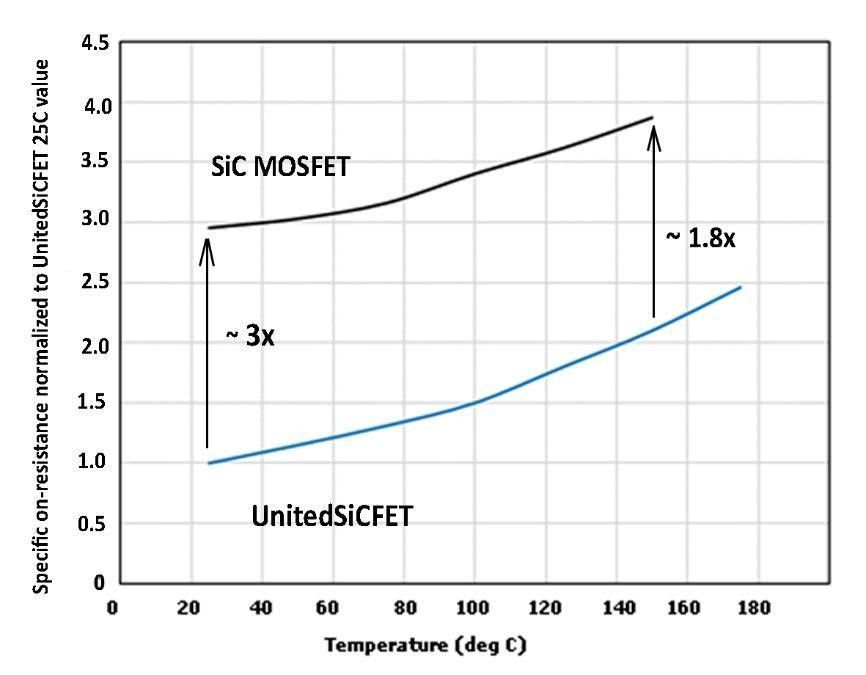

当您查看绝对值时,关键就来了。如图 2 所示,比较 RDS(ON)对于 650/750V 器件,UnitedSiC FET 的起始温度为 25°C,其比导通电阻约为 SiC MOSFET 的三分之一,在 2°C 时仍要好近 150 倍,在相同的有源芯片面积下,导通损耗约为其一半。

图 2:UnitedSiC FET 具有较高的导通电阻 Tc,但绝对值较低

净效应是,UnitedSiC FET的总传导损耗较低,健康的正温度系数为RDS(ON)以确保电池和并联设备之间的有效均流。确保比较有效并了解影响背后的机制显然是值得的——它可以揭示实际重要的事情:降低整体损失。

-

热敏电阻导通时的温度变化2024-12-06 2106

-

Qorvo推出D2PAK封装SiC FET2024-02-01 1616

-

SiC FET 耐抗性变化与温度变化 — 进行正确的比较2023-09-27 1233

-

碳化硅 (SiC) FET 推动电力电子技术发展2022-08-05 1818

-

在正确的比较中了解SiC FET导通电阻随温度产生的变化2021-01-08 3956

-

SIC MOSFET 驱动电路的设计概述2020-12-26 2478

-

ROHM开发出业界先进的第4代低导通电阻SiC MOSFET2020-06-22 1336

-

SiC MOSFET是具有低导通电阻和紧凑的芯片2020-06-15 5233

-

为何使用 SiC MOSFET2017-12-18 6053

-

10K_NTC热敏电阻随温度变化情形曲线图2016-01-12 5572

-

导通电阻,导通电阻的结构和作用是什么?2010-03-23 5807

-

FET导通电阻Ron的修正电路图2009-08-15 1754

全部0条评论

快来发表一下你的评论吧 !