先进封装:谁是赢家?谁是输家?

制造/封装

描述

全球最大的内存芯片制造商三星电子公司可能会加快对包括芯片封装在内的前沿技术的投资,芯片封装可以防止半导体材料的物理损坏和腐蚀。

2 月 17 日,三星集团领导人李在镕在视察韩国忠清南道天安市和温阳市的封装业务现场时表示,全球最大的内存芯片制造商应该坚持其投资和人才培养计划。在参观三星显示器牙山园区

10 天后,他又参观了制造现场,该园区是显示器部门位于同一省牙山市的主要工厂。

当时,李在镕强调,该公司应尽最大努力实现无与伦比的创新和竞争力,表明他将进一步扩大三星与全球同行之间的技术差距。

周五参观工厂时,三星电子执行董事长回顾了芯片制造业务的中长期战略,包括下一代半导体封装技术及其研发。

他还要求三星主要高管积极投资人才和未来技术,包括半导体业务负责人 Kyung Kye-hyun、晶圆代工业务负责人 Choi Si-young 和系统大系统总裁 Park Yong-in。规模集成 (LSI) 事业部。

最终加工阶段的关键技术

内存芯片封装是半导体器件制造的最后阶段,用于保护芯片材料并将芯片连接到电路板。随着谷歌有限责任公司和苹果公司等全球科技巨头提高芯片产量,先进封装技术变得越来越重要。

市场观察人士表示,三星将在芯片封装领域进行积极投资。它在去年底成立了一个专门负责先进封装业务的团队,以加快该技术的发展。

台积电在芯片封装技术上胜过三星。这家台湾半导体巨头去年 7 月在日本筑波建立了一个集成电路研发中心,用于硅堆叠和先进封装。

李在镕正在加快对半导体制造基地的访问——自去年 10 月就任三星电子董事长以来,他已经访问了韩国的七家工厂。

一位消息人士称,该集团对地区工厂的投资不仅促进了当地经济,也促进了三星合作伙伴公司的业务。

三星加码封装,晶圆厂争霸升级

据businesskorea报道,三星电子在其 DX 事业部的全球制造和基础设施部门内设立了测试和封装 (TP) 中心。

据报道,三星全球制造和基础设施部是负责与半导体生产和工厂运营相关的整个基础设施的组织,包括气体、化学、电力和环境安全设施。

借助该TP中心,三星希望能够引领公司在半导体测试和封装领域的激烈竞争中获胜。近来,封测已成为决定半导体业务竞争力的关键因素。台积电和英特尔也在大力投资新的半导体封装技术,例如异构组合。台积电计划在台湾建立新的半导体封装厂,并在日本建立研发中心。英特尔还将分别在马来西亚和意大利投资 70 亿美元(约合 8.63 万亿韩元)和 80 亿欧元(约合 10.85 万亿韩元)建设封装工厂。

三星也在寻求加强其封装能力。2015 年,该公司将苹果的 iPhone 应用处理器 (AP) 生产订单输给了开发扇出晶圆级封装 (FO-WLP) 技术的台积电。三星从这次经历中吸取了重要的教训,此后一直寻求增强其包装能力。

Gartner 预测,半导体封装市场预计将从 2020 年的 488 亿美元增长到 2025 年的 649 亿美元。

新一代2.5D先进封装,三星推出H-Cube解决方案

2021年11月,三星推出了全新2.5D封装解决方案H-Cube(Hybrid Substrate Cube,混合基板封装),专用于需要高性能和大面积封装技术的高性能计算(HPC)、人工智能(AI)、数据中心和网络产品等领域。

“H-Cube是三星电机(Samsung Electro-Mechanics, SEMCO) 和 Amkor Technology公司共同开发的成功案例。该封装解决方案适用于需要集成大量硅片的高性能芯片”,三星电子晶圆代工市场战略部高级副总裁Moonsoo Kang表示,“通过扩大和丰富代工生态系统,我们将提供丰富的封装解决方案,帮助客户突破挑战。”

“现如今,在对系统集成要求日益提升、大型基板供应困难的情况下,三星晶圆代工厂和Amkor Technology公司成功地联合开发了H-Cube(Hybrid Substrate Cube,混合基板封装)技术,以应对挑战。H-Cube降低了HPC/AI市场的准入门槛,晶圆代工厂和OSAT(Outsourced Semiconductor Assembly and Test)公司之间的合作也很成功。”Amkor Technology全球研发中心高级副总裁JinYoung Kim表示。

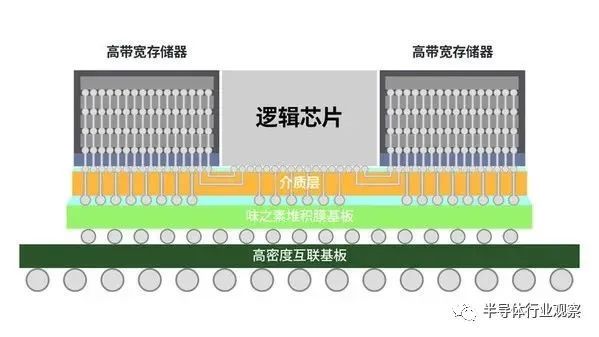

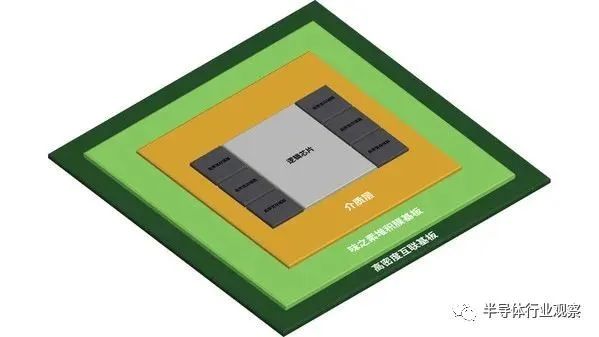

2.5D封装技术,通过硅中介层把逻辑芯片和高带宽内存芯片集成于方寸之间。三星H-CubeTM封装解决方案,通过整合两种具有不同特点的基板:精细化的ABF(Ajinomoto Build-up Film,味之素堆积膜)基板,以及HDI(High Density Interconnection,高密度互连)基板,可以进一步实现更大的2.5D封装。

随着现代高性能计算、人工智能和网络处理芯片的规格要求越来越高,需要封装在一起的芯片数量和面积剧增,带宽需求日益增高,使得大尺寸的封装变得越来越重要。其中关键的ABF基板,由于尺寸变大,价格也随之剧增。

特别是在集成6个或以上的HBM的情况下,制造大面积ABF基板的难度剧增,导致生产效率降低。我们通过采用在高端ABF基板上叠加大面积的HDI基板的结构,很好解决了这一难题。

通过将连接芯片和基板的焊锡球的间距缩短35%,可以缩小ABF基板的尺寸,同时在ABF基板下添加HDI基板以确保与系统板的连接。

此外,通过三星专有的信号/电源完整性分析,即便在集成多个逻辑芯片和HBM的情况下,H-Cube也能稳定供电和传输信号,而减少损耗或失真,从而增强了该解决方案的可靠性。

三星重估先进封装策略

积电今年资本支出拉高至400至440亿美元除全力提升制程技术与产能外,台积电也积极布局先进封测领域,甚至传出有意前往嘉义设封测厂,力拼提供客户一条龙服务。反观,韩媒披露,三星内部将重新评估设立先进封装扇出型晶圆级封装(FOWLP)产线的计划,最主要原因是,即使该产线建置完成,目前三星并没有可靠的大客户能确保产能,可能导致封装产线使用率低落。

《TheElec》报导,消息人士指出,三星原本打算在天安市投资2000亿韩元,建立先进封装扇出型晶圆级封装(FOWLP)产线,并将技术运用在旗下Exynos系列的处理器生产上,但近期的高层会议却对此事提出质疑。

报导指出,高层们认为,即使建立出一条FOWLP生产线,该生产线并无法获得充分利用,主因是目前没有可靠的大客户,可以保证对封装产线的需求。此外,主要潜在客户三星移动(Samsung Mobile)与高通(Qualcomm)的接受度也不高。

此外,客户们认为,使用传统PoP封装技术就能提高处理器的性能,且整体成本也低于FOWLP封装,导致目前客户并没有太大兴趣。不仅如此,三星天安工厂现有的PLP生产线也没有达到三星预期,目前该产线主要用在Galaxy Watch系列等智能手表的芯片封装。

目前三星内部仍未对此计划做出最终决定,而若该计划顺利进行,会先用于最近推出的Exynos 2200行动处理器的后续产品,且消息人士也认为,无论如何,三星仍会寻求扩大FOWLP的生产技术。

先进封装:谁是赢家?谁是输家?

近年来,因为传统的晶体管微缩方法走向了末路,于是产业便转向封装寻求提升芯片性能的新方法。例如近日的行业热点新闻《打破Chiplet的最后一道屏障,全新互联标准UCIe宣告成立》,可以说把Chiplet和先进封装的热度推向了又一个新高峰?

那么为什么我们需要先进封装呢?且看Yole解读一下。

为什么我们需要高性能封装?

随着前端节点越来越小,设计成本变得越来越重要。高级封装 (AP) 解决方案通过降低成本、提高系统性能、降低延迟、增加带宽和电源效率来帮助解决这些问题。

高端性能封装平台是 UHD FO、嵌入式 Si 桥、Si 中介层、3D 堆栈存储器和 3DSoC。嵌入式硅桥有两种解决方案:台积电的 LSI 和英特尔的 EMIB。对于Si interposer,通常有台积电、三星和联电提供的经典版本,以及英特尔的Foveros。EMIB 与 Foveros 结合产生了 Co-EMIB,用于 Intel 的 Ponte Vecchio。同时,3D 堆栈存储器由 HBM、3DS 和 3D NAND 堆栈三个类别表示。

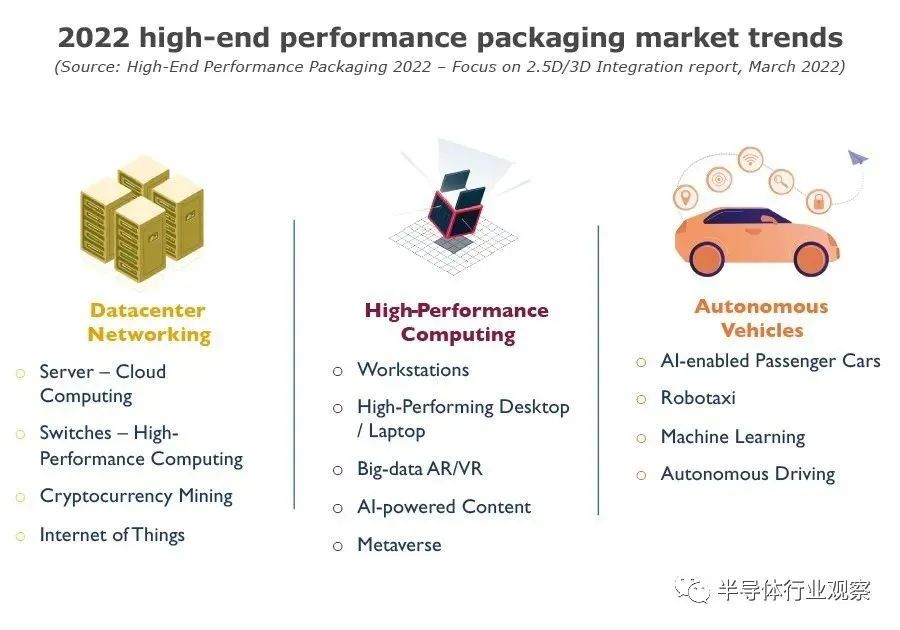

数据中心网络、高性能计算和自动驾驶汽车正在推动高端性能封装的采用,以及从技术角度来看的演变。今天的趋势是在云、边缘计算和设备级别拥有更大的计算资源。因此,不断增长的需求正在推动高端高性能封装的采用。

高性能封装市场规模?

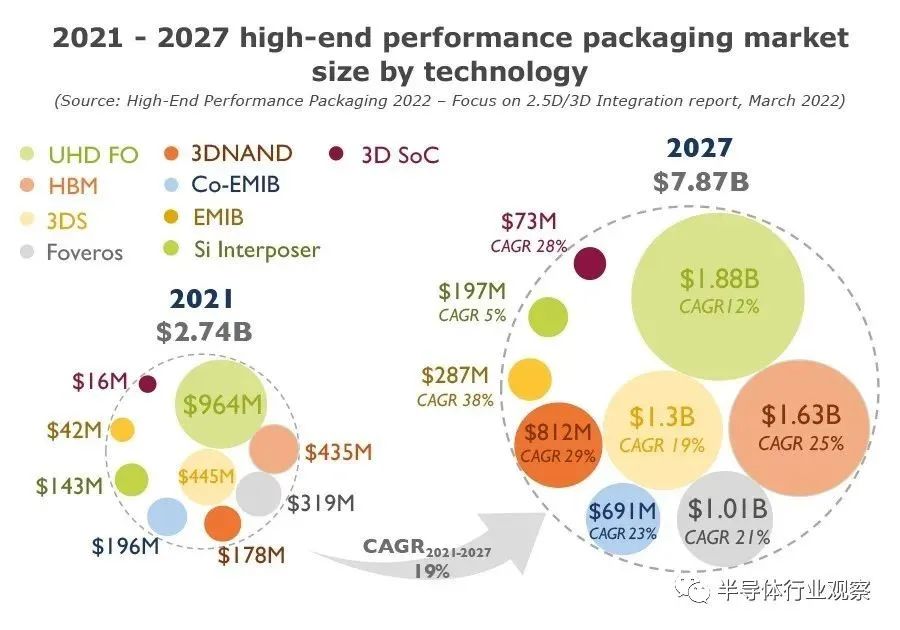

据Yole预测,到 2027 年,高性能封装市场收入预计将达到78.7亿美元,高于 2021 年的27.4亿美元,2021-2027 年的复合年增长率为 19%。到 2027 年,UHD FO、HBM、3DS 和有源 Si 中介层将占总市场份额的 50% 以上,是市场增长的最大贡献者。嵌入式 Si 桥、3D NAND 堆栈、3D SoC 和 HBM 是增长最快的四大贡献者,每个贡献者的 CAGR 都大于 20%。

由于电信和基础设施以及移动和消费终端市场中高端性能应用程序和人工智能的快速增长,这种演变是可能的。高端性能封装代表了一个相对较小的业务,但对半导体行业产生了巨大的影响,因为它是帮助满足比摩尔要求的关键解决方案之一。

谁是赢家,谁是输家?

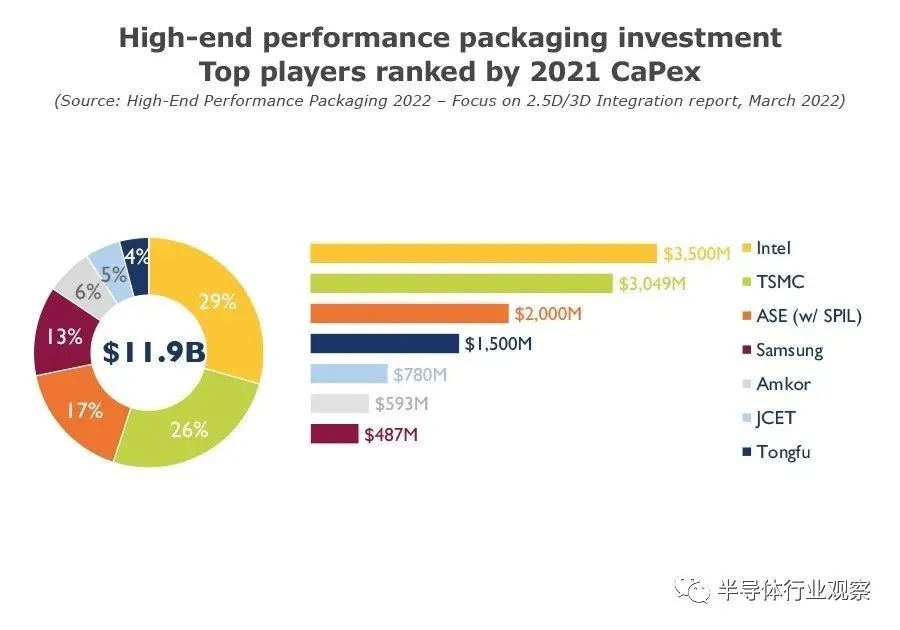

2021 年,顶级参与者为一揽子活动进行了大约116亿美元的资本支出投资,因为他们意识到这对于对抗摩尔定律放缓的重要性。

英特尔是这个行业的最大的投资者,指出了35亿美元。它的 3D 芯片堆叠技术是 Foveros,它包括在有源硅中介层上堆叠芯片。嵌入式多芯片互连桥是其采用 55 微米凸块间距的 2.5D 封装解决方案。Foveros 和 EMIB 的结合诞生了 Co-EMIB,用于 Ponte Vecchio GPU。

英特尔计划为 Foveros Direct 采用混合键合技术。 台积电紧随其后的是 30.5亿美元的资本支出。在通过 InFO 解决方案为 UHD FO 争取更多业务的同时,台积电还在为 3D SoC 定义新的系统级路线图和技术。

其 CoWoS 平台提供 RDL 或硅中介层解决方案,而其 LSI 平台是 EMIB 的直接竞争对手。台积电已成为高端封装巨头,拥有领先的前端先进节点,可以主导下一代系统级封装。

三星拥有类似于 CoWoS-S 的 I-Cube 技术。三星是 3D 堆栈内存解决方案的领导者之一,提供 HBM 和 3DS。其 X-Cube 将使用混合键合互连。

ASE 估计为先进封装投入了 20 亿美元的资本支出,是最大也是唯一一个试图与代工厂和 IDM 竞争封装活动的 OSAT。凭借其 FoCoS 产品,ASE 也是目前唯一具有 UHD FO 解决方案的 OSAT。

其他OSAT 不具备在先进封装竞赛中与英特尔、台积电和三星等大公司并驾齐驱的财务和前端能力。因此,他们是追随者。

编辑:黄飞

-

机器人香饽饽遭哄抢 谁是2016分羹运动大赢家?2016-12-08 810

-

就智能家居来说 CES 2017谁是赢家?2017-01-09 664

-

谁是您心中目录分销的No.1?2010-05-18 1728

-

三星与苹果的专利战争,谁是赢家?2012-09-11 3796

-

谁是真正的凶手?真相只有一个!2016-03-11 9450

-

谁是做智能机器人总体设计的,出来交流一下呗,有惊喜哦2016-07-08 2939

-

数据表与PSoC Creator之间谁是正确的?2019-10-08 1283

-

四核和NFC,2012年智能手机发展的赢家和输家2012-12-16 1653

-

在Micro LED专利布局上谁是领导者2019-05-28 7832

-

相互关联后谁会成为最大赢家2019-08-22 2912

-

荣耀卖身,谁是最大的赢家?2020-11-12 2324

-

全球芯片缺货究竟谁是赢家谁是输家?2021-04-21 3854

-

电容式电气隔离与光耦合器技术对比 — 谁是赢家?2022-11-04 886

-

谁是音频时钟的“老板”?2022-11-07 588

全部0条评论

快来发表一下你的评论吧 !