EDA探索之MOSFET收缩,Happy Scaling Era

EDA/IC设计

描述

·2022年,集成电路半导体行业最热的头条是“EDA被全面封锁”。如何突破EDA封锁,成为行业发展的关键词,也是群体焦虑。在全球市场,有人比喻EDA是“芯片之母”,如果没有了芯片,工业发展和社会进步将处处受制,EDA的重要性也上升到了战略性高度。尽管国际封锁形势严峻,但睿智的中国科技人擅于把危机化为机会,从《加快自主研发应用,让工业软件不再卡脖子》,到《破解科技卡脖子要打好三张牌》,即一要打好“基础牌”,提升基础创新能力;二要打好“应用牌”,加强对高精尖国货的应用;三是要打好“人才牌”,让人才留得住、用得上、有发展……,各种政策、举措和实际行动,处处彰显了我们中国科技的发展韧性。

谈起集成电路,黄发垂髫,言必及摩尔定律,如果以两个字来概括摩尔定律,那必然就是“微缩”。

我们希望集成电路进行微缩后,其器件的性能还能够得以保持。这样就可以保证电路的设计基本不变,只从工艺进步的角度,即可以得到非常大的改进。

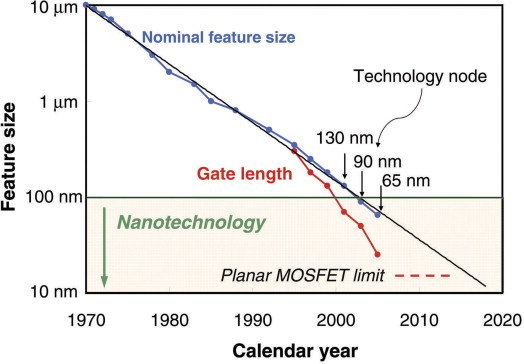

图:MOSFET特征尺寸的缩小。来自Mahmoud Darwish,Memristive Behavior In Vanadium Dioxide Elements: Simulation And Modeling

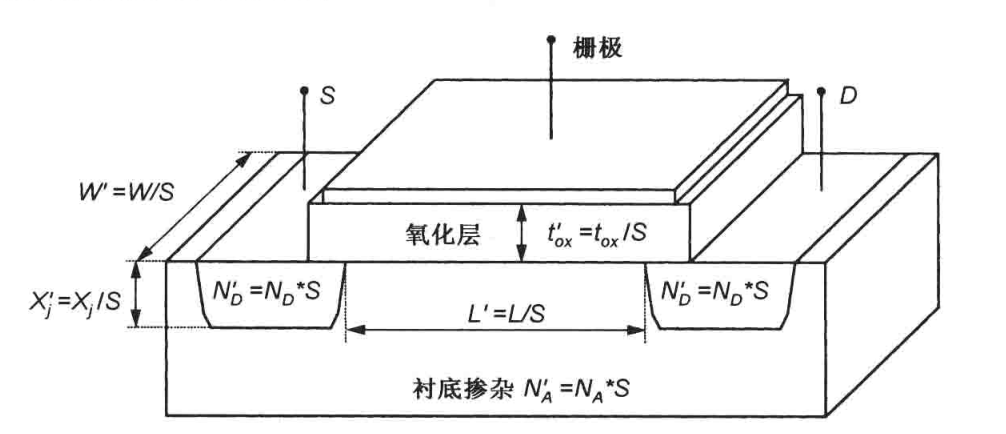

我们假设器件的所有线性尺寸都按S例收缩,如下图所示。S因子是一个大于1的数,代表了收缩的倍数。

器件按S因子缩小示意图。来自《CMOS数字集成电路——分析与设计(第四版)》

一般而言,每一代集成电路工艺在尺寸上缩减至上一代的0.7倍(即S因子1.428),表现在面积上,就是0.7的平方,0.49倍。即面积比原来小一半,密度比原来高一倍。

器件尺寸减小有两种基本的类型:全收缩(也称为恒场强等比例收缩)和恒电压等比例收缩。

全收缩

所谓全收缩,即器件所有的几何线全部收缩。同时要求器件内部的电场强度不变。为了实现这个目标,所有的电压都需要保持同一个收缩因子减小,而掺杂浓度要求以S因子扩大。

我们假设材料的特性(迁移率,介电常数)不随收缩而变化。很容易得出,栅电容密度会相比收缩前增大S倍

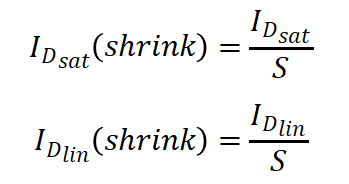

则代入公式可以得到:

即电流也会按S因子缩小。

由于功率是电流与电压的乘积,而电流与电压都按S因子缩小,因此功率P会按S的平方缩小。这是全收缩最突出的优点,即功率显著地缩小。而考虑到面积也是按S的平方缩小,即单位面积的功率不变。

由于面积按S的平方减小,而电容密度则按S增大。因此实际的电容会按S缩小。这意味着与电容相关的延迟都会减小。总的来说,全收缩下芯片的功耗显著降低,而性能有所提高。

恒电压按比例收缩

全收缩方式看上去拥有各种优势,但是它要求电压也按比例缩小在大多数情况下是难以实现的。这往往代表了芯片驱动能力的减弱。尤其是需要与其它相关器件配套使用的芯片,如果电压下降过多,则意味着无法驱动LED灯点亮或者输出电平太低,让耳机声音弱到类似于“蚊子叫”。因此我们需要保持电压不变,同时为了保持电场不变。掺杂浓度需要以S的平方减小。在这种条件下,相应的电流也会增大S倍,由于电压不变,功率会随电流增大S倍。

另一方面,器件的面积按S的平方缩小,所以功率密度会达到S的立方。这是一个非常大的增加,因此需要考虑器件的热效应。如此大的功率密度可能会导致器件剧烈升温,进而导致电介质击穿,材料性能的热退化等等问题。

在集成电路的微米时代,材料的性质一般不会随尺寸的变化发生较大的改变,器件的散热条件,掺杂的浓度都有较大的余量。因此比较容易按照全收缩或者恒电压收缩的方式进行。只要光刻设备能够刻画出相应的图形,后续的工艺也比较容易实现。一切都来得自然而高效,这也被称为Happy Scaling Era。而进入到纳米时代之后,就不那么happy了,需要更多更复杂的技术来推动器件进一步缩小。且等下次探索来分解。

编辑:黄飞

-

松下高压薄膜贴片电阻ERA 8P系列:高性能与高可靠性之选2025-12-22 160

-

EDA探索之MOSFET的微缩- Moore’s Law介绍2023-03-29 826

-

EDA探索之MOSFET的微缩-nanosheet era2023-03-24 883

-

EDA探索:MOSFET Scaling-3D Era2023-03-16 1482

-

EDA探索之MOSFET收缩规则2023-03-13 1058

-

42 MOSFET 的 scaling 规则(1)#硬声创作季学习电子 2022-11-30

-

承德科胜热收缩膜机|面膜盒收缩机|河北收缩机2018-08-25 517

-

EDA学习之万年历电路的设计2018-06-27 1518

-

FFTC问题求解答!!!动态scaling2018-06-21 1973

-

可收缩塑料材料收缩力检测国际标准2015-12-08 497

-

张兴柱之MOSFET分析2014-06-19 12536

-

EDA简介(Eng)2011-10-11 3674

-

探索性数据分析(EDA)及其应用2011-01-24 1843

-

数字电池EDA入门之VHDL程序实现集2009-12-07 596

全部0条评论

快来发表一下你的评论吧 !