编写一个创建模块dut实例的测试平台

描述

题目说明

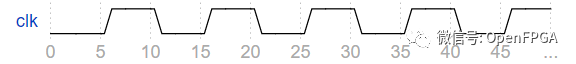

编写一个创建模块dut实例(具有任何实例名称)的测试平台,并创建一个时钟信号来驱动模块的clk输入。时钟周期为 10 ps。时钟应初始化为零,其第一个转换为 0 到 1。

模块端口声明

module top_module ( );

题目解析

生成clock有很多种方式,常见的就是forever和always。

timeunit 1ps ; timeprecision 1ps ; module top_module ( ); logic clk ; dut u1_dut( .clk(clk) ); initial begin clk <= 1'b0 ; end always #5 clk <= ~clk ; endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

Problem 174-tb1

题目说明

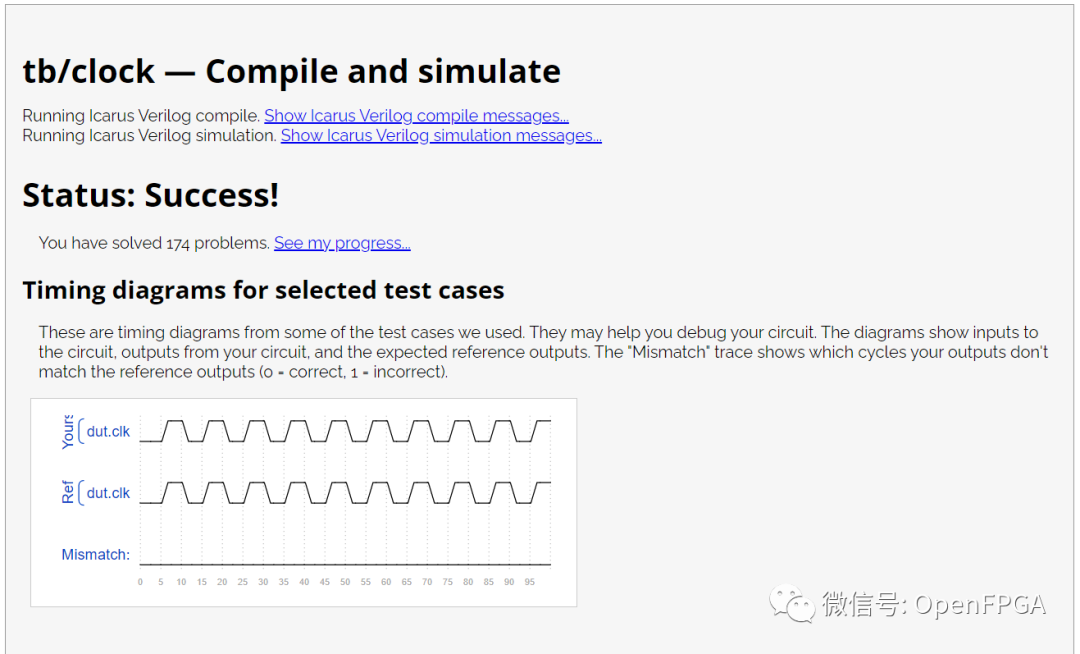

创建一个 Verilog 测试台,它将为输出 A 和 B 生成以下波形

模块端口声明

module top_module ( output reg A, output reg B );

题目解析

initial+# n即可。

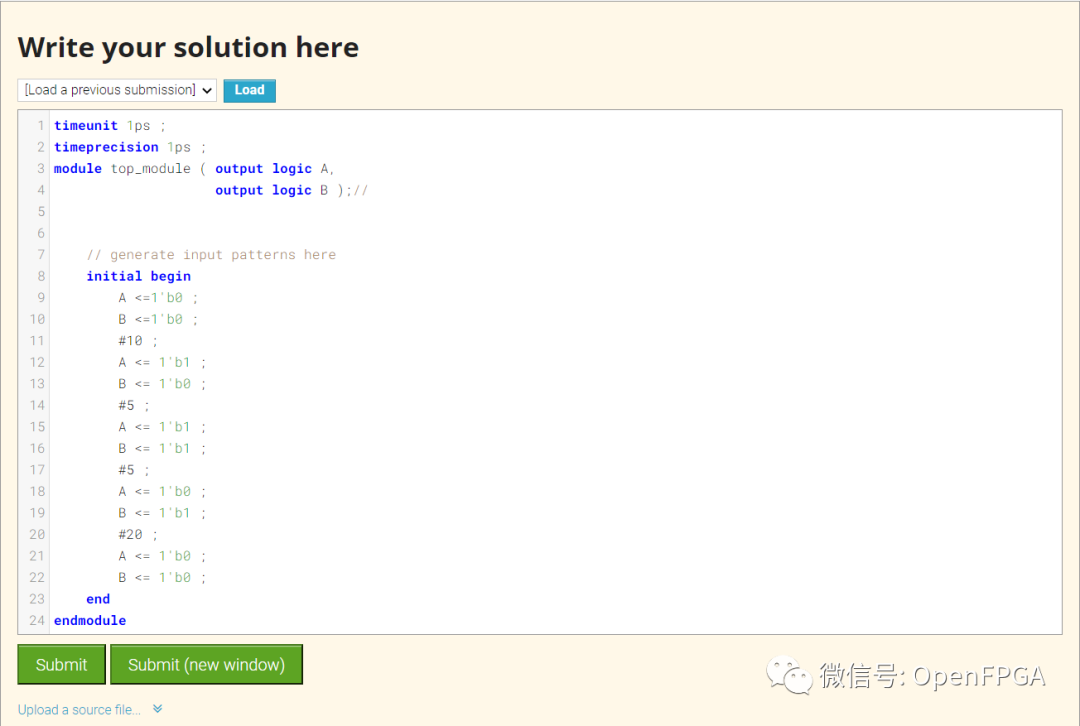

timeunit 1ps ; timeprecision 1ps ; module top_module ( output logic A, output logic B );// // generate input patterns here initial begin A <=1'b0 ; B <=1'b0 ; #10 ; A <= 1'b1 ; B <= 1'b0 ; #5 ; A <= 1'b1 ; B <= 1'b1 ; #5 ; A <= 1'b0 ; B <= 1'b1 ; #20 ; A <= 1'b0 ; B <= 1'b0 ; end endmodule

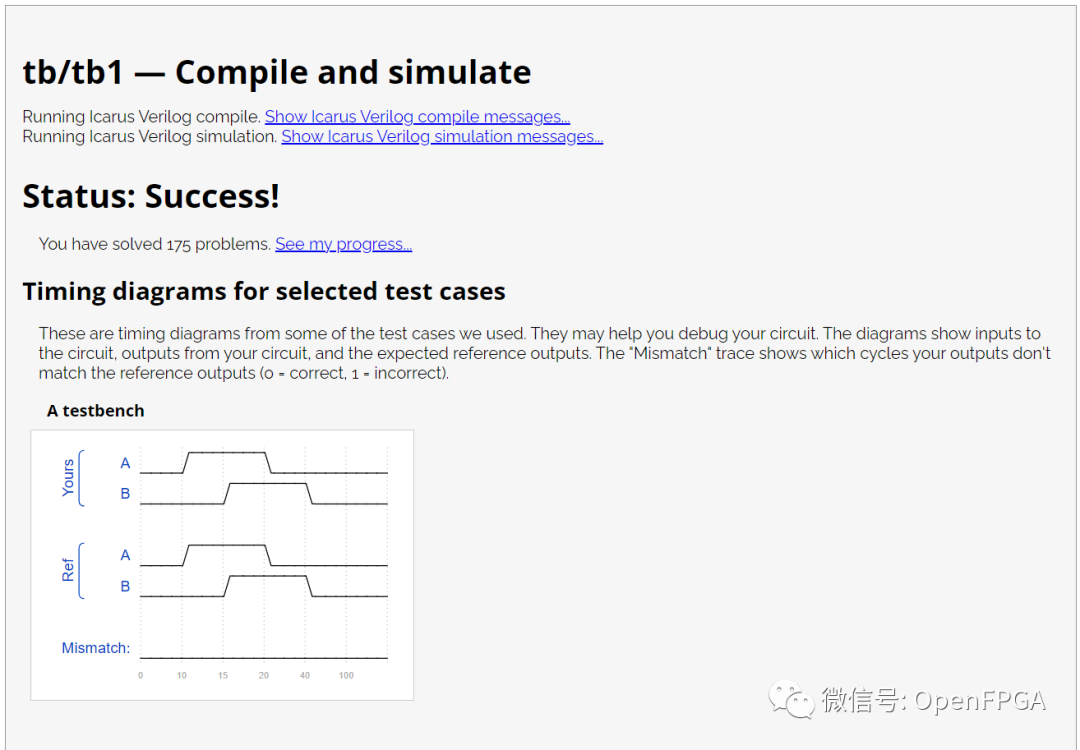

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

Problem 175-and

题目说明

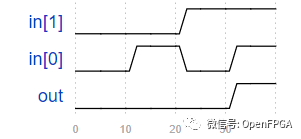

给给定的与门写测试文件,波形参考下图。

模块端口声明

module top_module();

题目解析

和上一题类似。

timeunit 1ps ; timeprecision 1ps ; module top_module(); logic [1:0]in ; wire logic out ; andgate u_andgate( .in(in), .out(out) ); initial begin in <= 2'b00 ; #10 ; in <= 2'b01 ; #10 ; in <= 2'b10 ; #10 ; in <= 2'b11 ; end endmodule

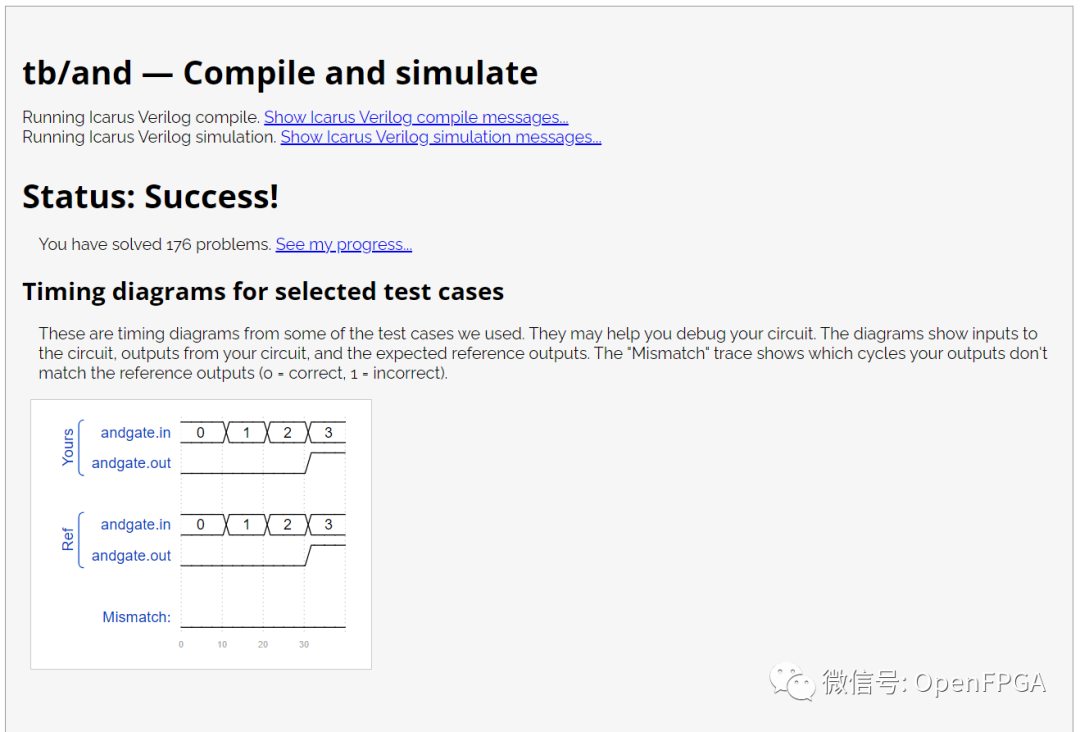

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

Problem 176-tb2

题目说明

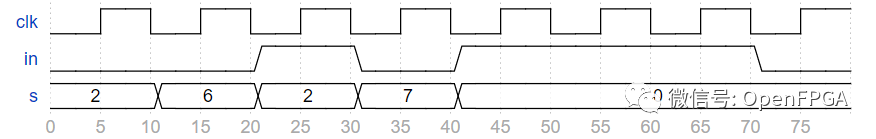

给定一个q7电路,按照下图编写testbench:

模块端口声明

module top_module();

题目解析

timeunit 1ps ; timeprecision 1ps ; module top_module(); logic clk ; logic in ; logic [2:0] s ; wire logic out ; q7 u1_q7( .clk (clk), .in (in ), .s (s ), .out (out) ); initial begin clk <= 1'b0 ; forever #5 clk <= ~clk ; end initial begin in <= 1'b0 ; s <= 3'd2 ; #10 ; in <= 1'b0 ; s <= 3'd6 ; #10 ; in <= 1'b1 ; s <= 3'd2 ; #10 ; in <= 1'b0 ; s <= 3'd7 ; #10 ; in <= 1'b1 ; s <= 3'd0 ; #30 ; in <= 1'b0 ; s <= 3'd0 ; end endmodule

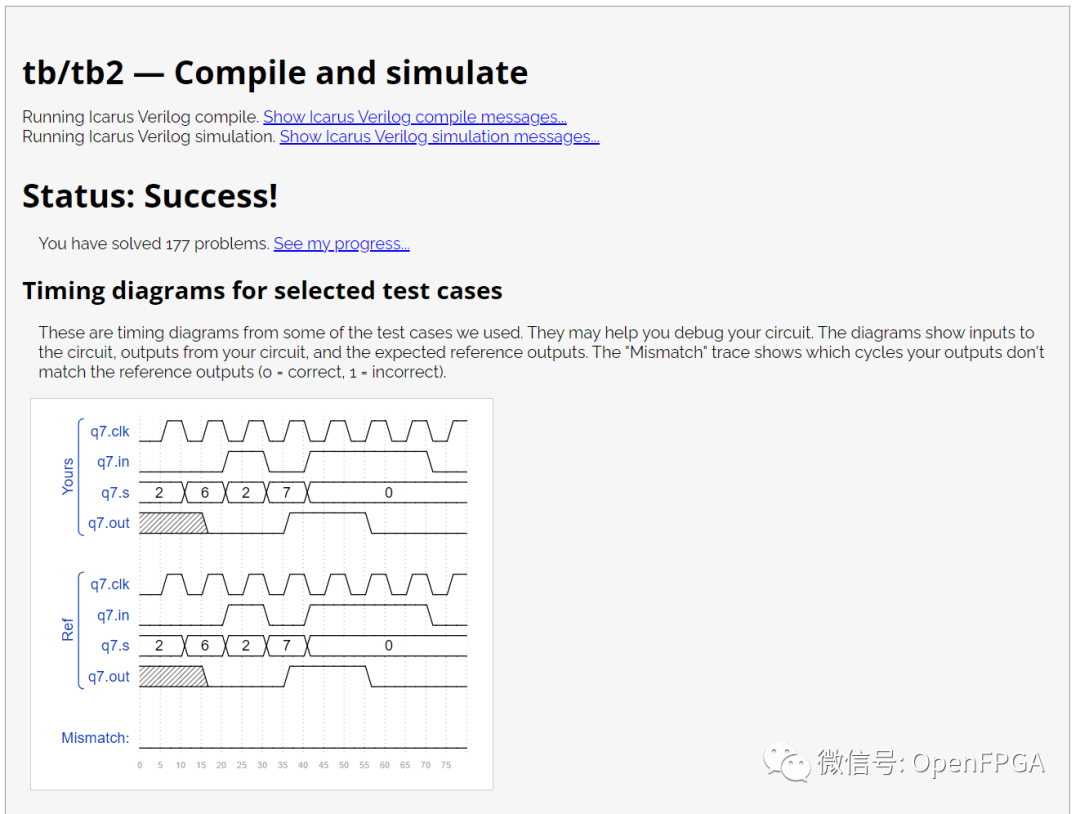

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

Problem 177-tff

题目说明

给题目中给定的tff编写测试文件。

模块端口声明

module top_module ();

题目解析

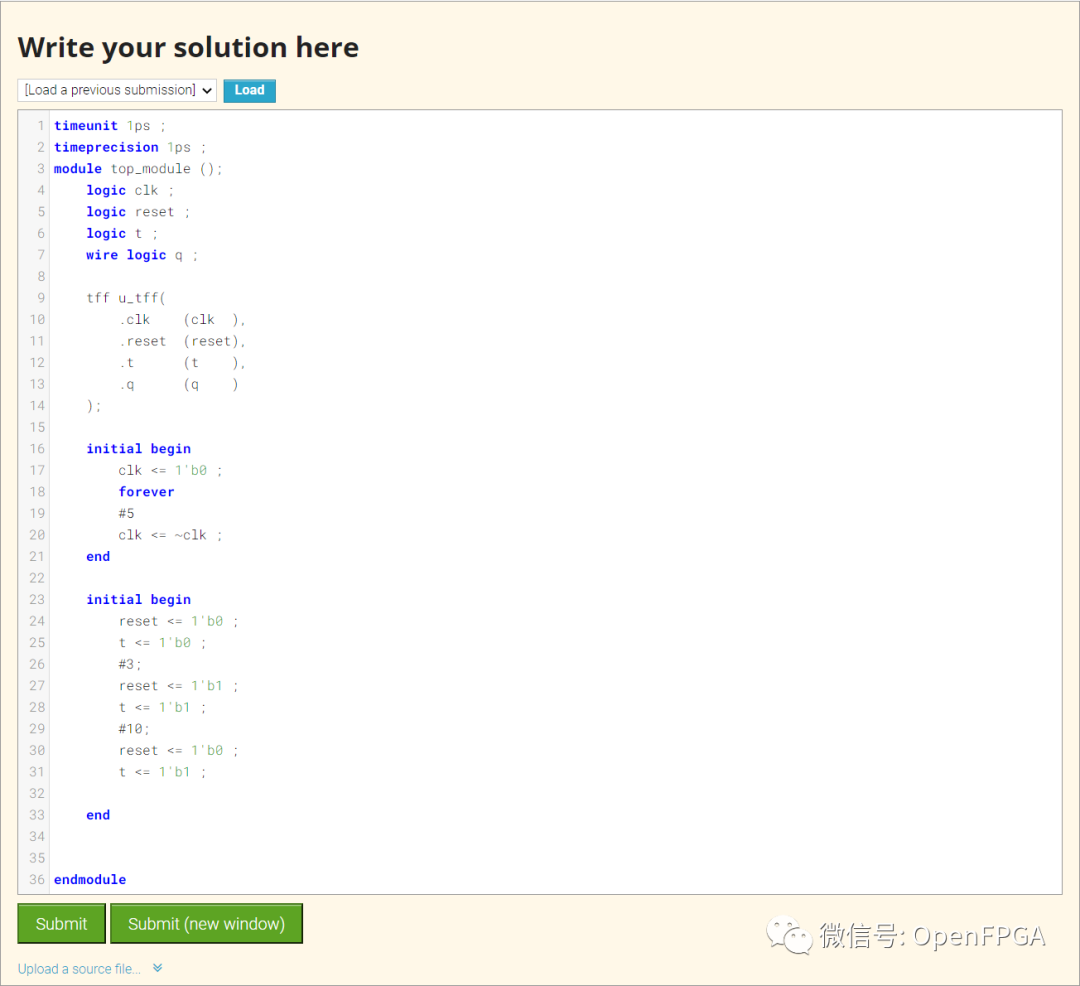

timeunit 1ps ; timeprecision 1ps ; module top_module (); logic clk ; logic reset ; logic t ; wire logic q ; tff u_tff( .clk (clk ), .reset (reset), .t (t ), .q (q ) ); initial begin clk <= 1'b0 ; forever #5 clk <= ~clk ; end initial begin reset <= 1'b0 ; t <= 1'b0 ; #3; reset <= 1'b1 ; t <= 1'b1 ; #10; reset <= 1'b0 ; t <= 1'b1 ; end endmodule

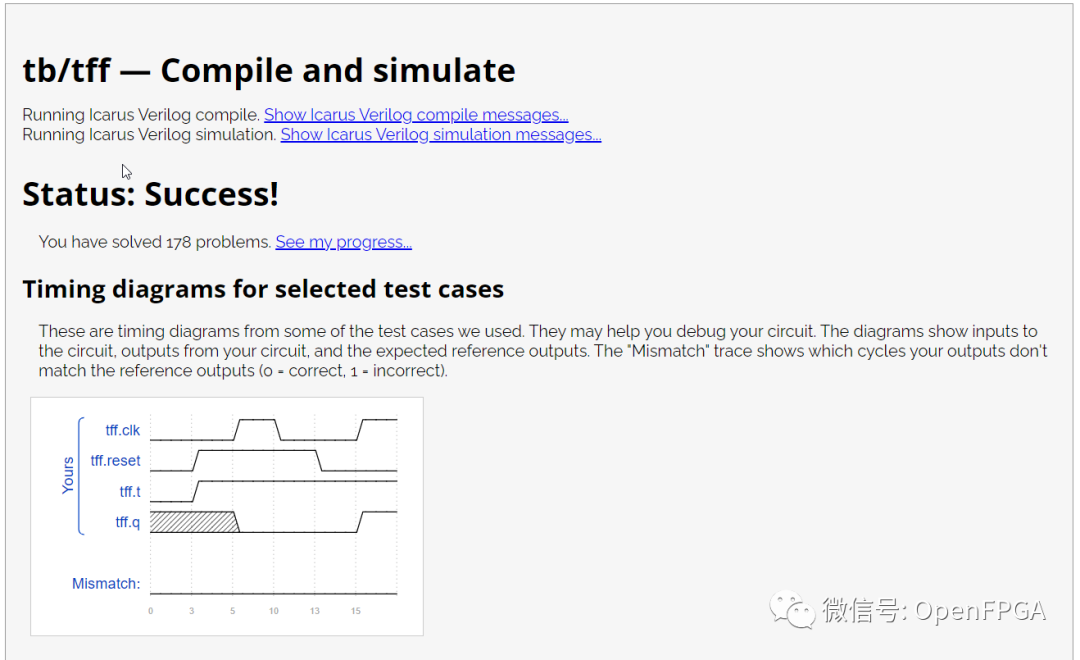

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

审核编辑:刘清

-

如何在PetaLinux流程外创建模块2022-09-28 1605

-

阿里云云效功能升级,支持快速创建多个应用的独立测试环境2018-06-25 1050

-

FPGA固件开发- 测试平台的编写2018-11-28 2810

-

数字IC验证之“构成uvm测试平台的主要组件”(4)连载中...2021-01-22 4624

-

Simulink建模仿真实例快速入门2015-12-28 2952

-

Verilog HDL硬件描述语言_建模实例2016-04-25 782

-

PCB设计:网络分析仪测试DUT出现2个差不多的阻抗?2021-03-24 4089

-

VHDL测试平台编写综述2021-01-20 1225

-

使用物联网平台创建一个温度警报系统2022-11-22 731

-

对DUT输入定向或随机的激励2023-02-24 1669

-

DUT 和 testbench 连接教程2023-03-21 2431

-

SOLIDWORKS曲面建模实例2023-04-06 4657

-

芯片验证需要围绕DUT做什么?2023-06-12 3267

-

可重用的验证组件中构建测试平台的步骤2023-06-13 1544

-

鸿蒙ArkUI-X跨平台开发:【 编写第一个ArkUI-X应用】2024-05-21 2336

全部0条评论

快来发表一下你的评论吧 !