MOSFET选得好,极性反接保护更可靠

电子说

描述

MOSFET选得好,极性反接保护更可靠

当车辆电池因损坏而需要更换时,新电池极性接反的可能性很高。车辆中的许多电子控制单元 (ECU) 都连接到车辆电池,因而此类事件可能会导致大量 ECU 故障。

ISO(国际标准化组织)等汽车标准定义了电气电子设备的测试方法、电压水平、电磁辐射限值,以确保系统安全可靠地运行。与极性反接保护 (RPP) 相关的一种标准是 ISO 7637-2:2011,它复制了实际应用中的各种电压场景,系统需要承受此类电压以展示其能够防范故障的稳健性。这使得极性反接保护成为连接电池的 ECU/系统的一个关键组成部分,所有汽车制造商都需要。

本文将首先介绍 ISO 脉冲,通常使用此类脉冲来复制实际应用中可能出现的电压瞬变。然后将详细说明可以使用的几种保护技术,并指导读者选择外部 N 沟道 MOSFET——它将提供 RPP 并帮助降低系统的功率损耗。最后,将基于电池电流推荐与理想的二极管控制器一起使用的 N 沟道 MOSFET 清单。

ISO 脉冲

为确保配备了 12 V 或 24 V 电气系统的乘用车和商用车上安装的设备与传导电瞬变兼容,国际标准 ISO 7637-2:2011 规定了测试方法和程序。有关详细信息,请参阅 ISO 7637-2:2011。

该标准定义了多种类型的测试脉冲来测试器件。以下是其中的几种测试脉冲。

● 脉冲 1:感性负载的电源断开导致的瞬变。

● 脉冲 2a:因线束的电感导致与 DUT(被测器件)并联的器件中的电流突然中断引起的瞬变。

● 脉冲 3a 和 3b:由于开关过程而发生的瞬变。这些瞬变的特性受线束的分布电容和电感的影响。

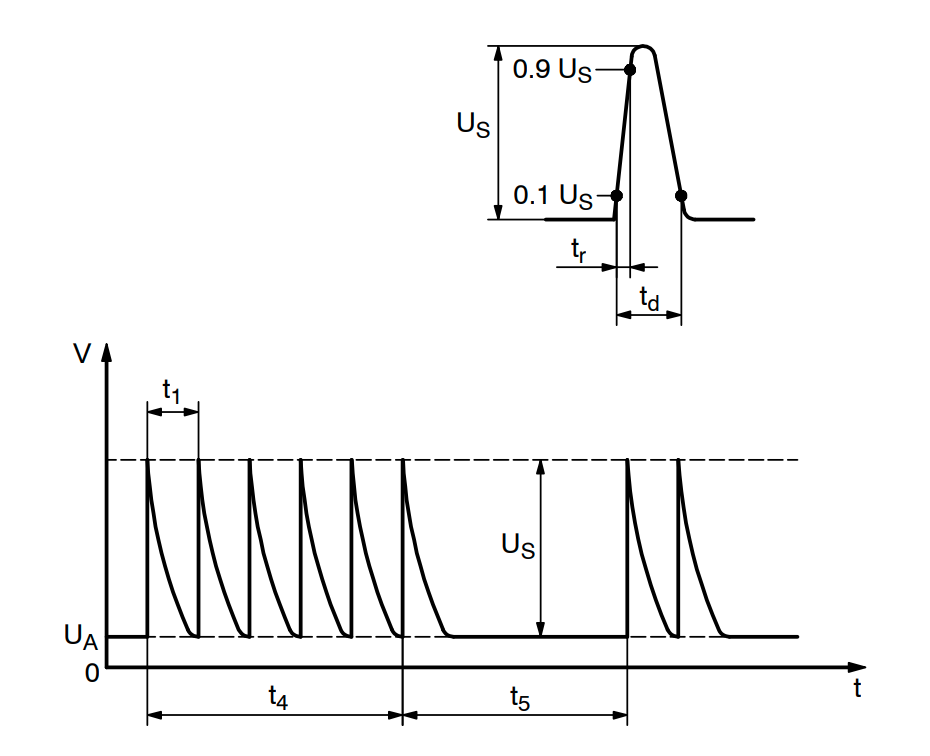

这些测试脉冲具有不同的负电压和正电压电平,从而对 DUT 施加压力,看它能否承受。例如,通过图 1 所示的脉冲 3b 可以大致了解标准中定义的脉冲类型;每种脉冲都有自己的参数,如表 1 所示。脉冲 3b 模拟实际应用中的开关噪声,例如,继电器和开关触点抖动会产生短暂的突发高频脉冲。AND8228/D 详细讨论了电压瞬变和测试方法。

图 1. 测试脉冲 3b

表 1. 测试脉冲 3b 的参数

极性反接保护技术

下面讨论三种最常见的极性反接保护技术。

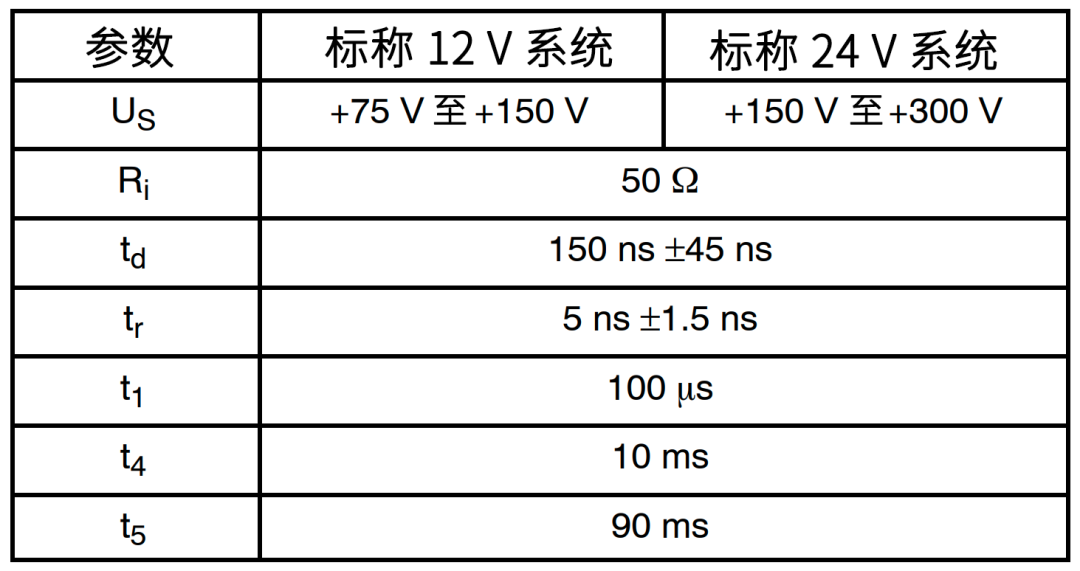

二极管

保护系统免受电池反接影响的最简单方法是使用二极管。如图 2 所示,二极管只有在其端子连接到正确的极性(即正偏)时才会传导电流。标准二极管的正向压降 VF 约为 0.7 V,但肖特基二极管的正向压降可低至 0.3 V。因此,大多数应用使用肖特基二极管以降低系统损耗。

图 2. 使用二极管的极性反接保护

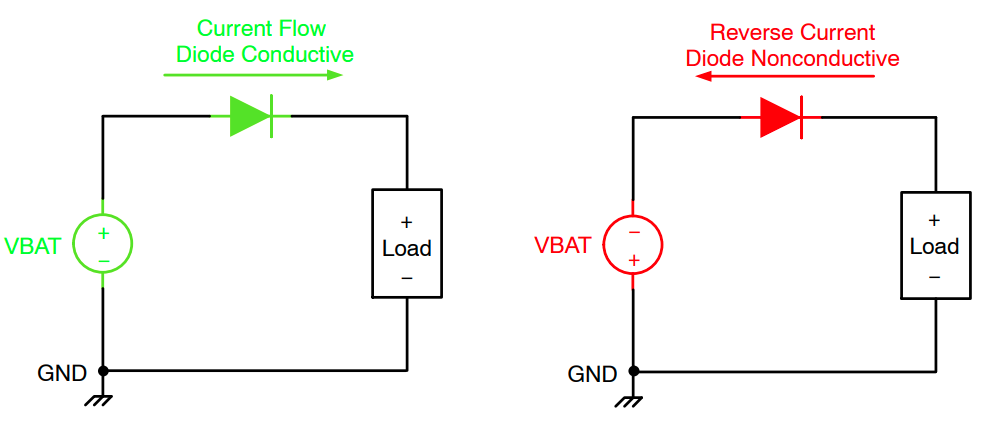

图 3 显示了 NRVBSS24NT3G 肖特基二极管的典型压降。在结温 TJ 为 25°C 时,如果二极管电流 (IDIODE) 从 0.5 A 提高到 1.0 A(100% 增加),VF 将从 0.35 V 提高到 0.40 V(15% 增加)。

图 3. NRVBSS24NT3G 肖特基二极管的典型正向电压

MOSFET

二极管的一种替代方案是 MOSFET。当 MOSFET 导通时,漏源压降 VDS 取决于漏源电阻 RDS,ON 和漏源电流 ID:VDS = RDS,ON * ID。与肖特基二极管相比,该压降一般要低得多。

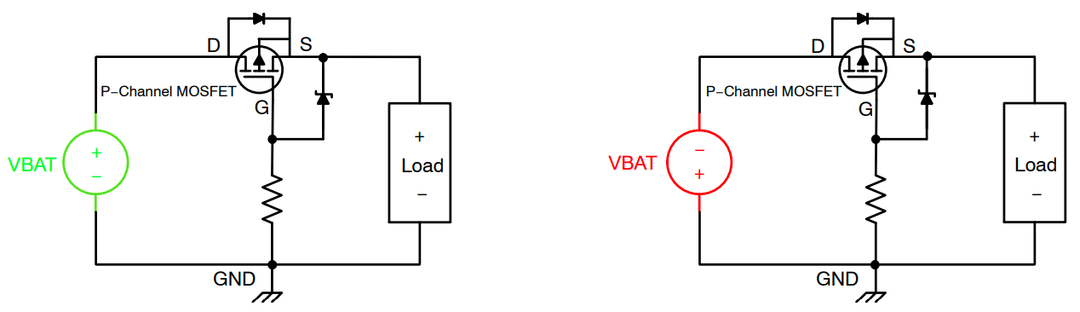

P 沟道 MOSFET

与所有 MOSFET 一样,P 沟道 MOSFET 在源极和漏极之间有一个本征体二极管。当电池正确连接时,本征体二极管导通,直到 MOSFET 的沟道导通。要使 P 沟道 MOSFET 导通,栅极电压需要比源极电压低至少 VT(阈值电压)。当电池反接时,体二极管反偏,栅极和源极电压相同,因此 P 沟道 MOSFET 关断。使用一个额外的齐纳二极管来箝位 P 沟道 MOSFET 的栅极,在电压过高时提供保护。

图 4. 使用 P 沟道 MOSFET 提供极性反接保护

N 沟道 MOSFET

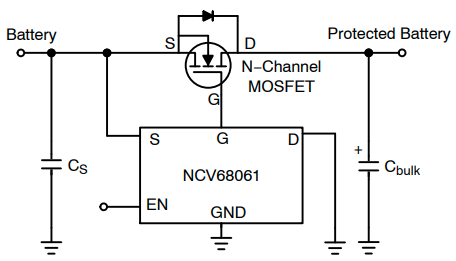

也可以使用 N 沟道 MOSFET 来提供极性反接保护。当电池正确连接时(源极连接到 VBAT),要使 MOSFET 导通,栅源电压必须高于阈值电压 (VGS > VTH)。鉴于源极连接到 VBAT,故栅极电压需要比 VBAT 高至少 VT。因此,使用一个专用驱动器来驱动 N 沟道 MOSFET 的栅极电压,使其高于源极电压,从而使 N 沟道 MOSFET 导通。当电池反接时,体二极管反偏(阳极电压低于阴极电压),驱动器被禁用(源极和栅极短路),N 沟道 MOSFET 关断。

图 5. 使用 N 沟道 MOSFET 提供极性反接保护

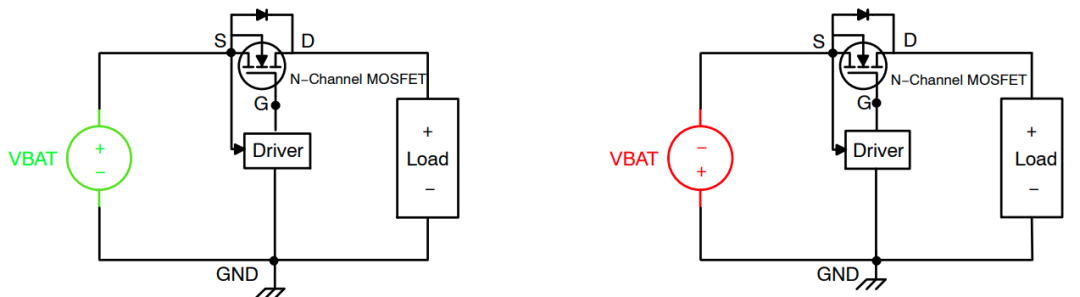

极性反接保护技术比较

表 2 总结了不同极性反接保护技术的优缺点。值得一提的是,P 沟道 MOSFET 的操作取决于空穴的迁移率,而 N 沟道 MOSFET 的操作取决于电子的迁移率。已知对于相同的漏极电流,电子的迁移率比空穴的迁移率高几乎 2.5 倍。因此,为实现相同的导通电阻,P 沟道 MOSFET 的芯片尺寸会比 N 沟道 MOSFET 更大,相应地成本也更高。这使得 N 沟道 MOSFET 比 P 沟道 MOSFET 更适合此类应用。

表 2. 不同保护技术的比较

MOSFET 选择

选择用于极性反接保护的 N 沟道 MOSFET 时,需要考虑多种参数。

● MOSFET 的最大击穿电压 VDS,MAX

▸对于 12 V 板网(汽车),首选 VDS,MAX = 40 V

▸对于 24 V 板网(卡车),首选 VDS,MAX = 60V

● 最大工作结温 TJ,MAX

▸对于汽车和卡车应用,鉴于环境恶劣,建议使用 175°C

● 栅极电平

▸最好使用逻辑电平,而不要使用标准电平,因为对于相同栅源电压 VGS,前者的 RDS,ON 更低

● 封装

▸通常使用带裸露焊盘的3.30×3.30mm(即 LFPAK33/WDFN8/μ8FL)和 5.00×6.00 mm(即 SO8-FL/LFPAK56)封装以优化功耗

● 总栅极电荷 QG,TOT

▸MOSFET 导通分为 3 个阶段

i. 当栅极电压 VGS 上升至平坦区域电压 VGP 时,电荷主要用于为输入电容 CISS 充电。

ii. 当 VGS 处于平坦区域电压 VGP 时,电荷主要用于为反向传输电容(栅漏电容)CRSS 充电。

iii.当 VGS 从 VGP 上升至驱动器电源电压 VGDR 时,电荷用于进一步增强沟道。

▸QG,TOT 越低,MOSFET 导通所需的栅极电压和电流越小(即导通速度越快),反之亦然

● 漏源电阻 RDS,ON

▸RDS,ON 的作用是限制器件的功耗。对于给定负载电流,RDS,ON 越大,功耗越高。更高功耗会导致 MOSFET 的 TJ 升高。因此,为了获得最优性能,正确选择具有所需 RDS,ON 的器件很重要。

▸在以下部分中,选择用于热评估的 MOSFET 的 RDS,ON 将使功耗保持在 500 mW 左右。

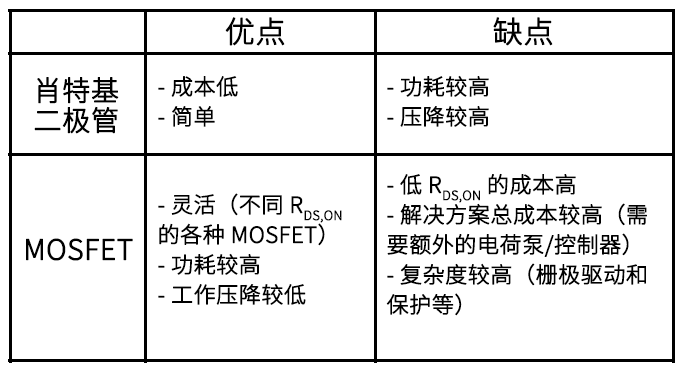

NCV68061 理想二极管控制器

NCV68061 和外部 N 沟道 MOSFET 的组合构成一个理想二极管:当施加正偏电压(阳极电压高于阴极电压)时,它充当一个理想导体;当施加反偏电压(阳极电压低于阴极电压)时,它充当一个理想绝缘体。NCV68061 是一款极性反接保护和理想二极管 N 沟道 MOSFET 控制器,旨在取代二极管,其损耗和正向电压更低。

NCV68061 的主要功能是根据源漏差分电压极性控制外部 N 沟道 MOSFET 的通断状态。根据漏极引脚连接,该器件可以配置为两种不同的应用模式。当漏极引脚连接到负载时,应用处于理想二极管模式,而当漏极引脚接地时,NCV68061 仅处于极性反接保护模式。在这两种模式下,控制器都会为外部 N 沟道 MOSFET 提供 11.4 V 的典型栅极电压。因此,以下部分的所有计算都使用 10 V VGS 时的 RDS,ON。

NCV68061 已通过 ISO 7637-2:2011 测试,结果证明该器件非常稳健,能够承受电压应力。NCV68061 数据表显示了测试结果。

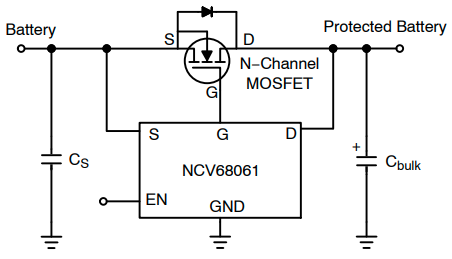

理想二极管应用

图 6 显示了 NCV68061 在理想二极管配置下的使用情况。在此配置中,不允许输入电压对大容量电容 Cbulk 放电。此配置有两种模式:

▸导通模式:在进入导通模式之前,源极电压低于漏极电压,电荷泵和 N 沟道 MOSFET 均被禁用。随着源极电压变得比漏极电压大,正向电流流过 N 沟道 MOSFET 的体二极管。一旦此正向压降超过源漏栅极充电电压阈值电平(典型值 140 mV),电荷泵就会开启,N 沟道 MOSFET 变成完全导通状态。

▸反向电流阻断模式:当源极电压变得比漏极电压小时,反向电流最初流过 N 沟道 MOSFET 的导电沟道。此电流在 N 沟道 MOSFET 的导电沟道上产生一个与其 RDS,ON 成比例的压降。当此电压降至源漏栅极放电电压阈值(典型值 -10 mV)以下时,电荷泵被禁用,外部 N 沟道 MOSFET 由控制器的内部 P 沟道 MOSFET 关断。

图 6. NCV68061 理想二极管应用

图 7. NCV68061 极性反接保护应用

极性反接保护

如图 7 所示,通过将漏极引脚连接到 GND 电位,NCV68061 将不允许下降的输入电压将输出放电到 GND 电位以下,但允许输出跟随任何高于欠压锁定 (UVLO) 阈值的正输入电压。这意味着,下降的输入电压会将大容量电容 Cbulk 放电。

当源极电压高于 UVLO 阈值(典型值 3.3 V)时,源极/漏极和 UVLO 比较器使电荷泵能够向完全导通的外部 N 沟道 MOSFET 提供栅源电压。当源极电压低于 UVLO 阈值(典型值 3.2 V)时,电荷泵和 N 沟道 MOSFET 被禁用,所有负载电流流过 N 沟道 MOSFET 的体二极管。

测试设置

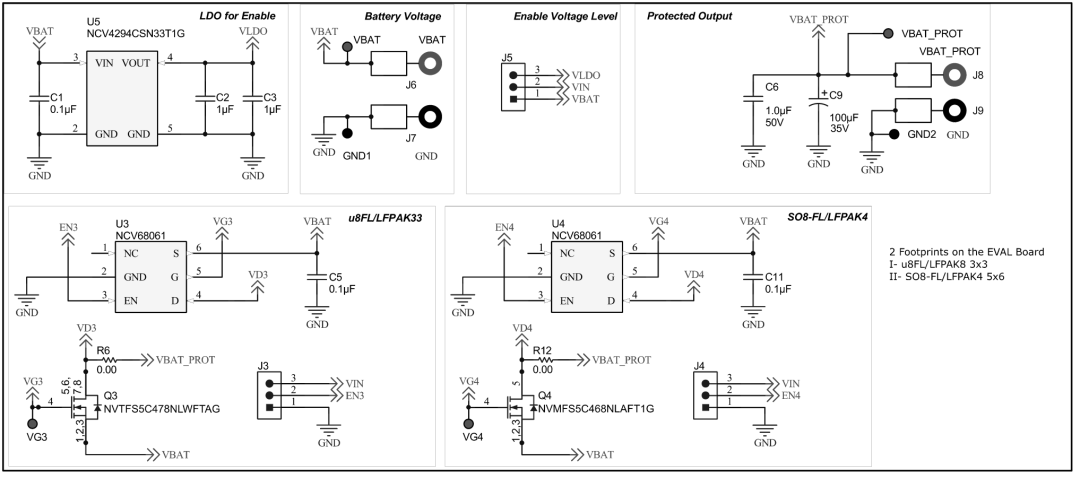

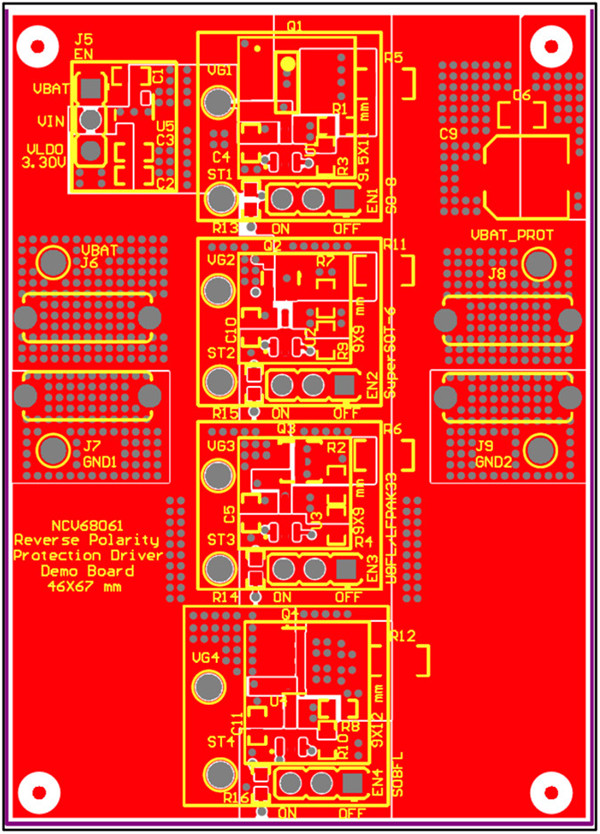

使用 NCV68061 的专用测试板来确定各种采用 3×3 和 5×6 封装且有不同 RDS,ON 的 MOSFET 的功耗和热性能,以帮助理解不同负载电流下用于理想二极管控制器的 MOSFET 选择。

电路图

图 8 显示了测试板的电路图。其设计方式支持测试SO-8FL/LFPAK4和μ8FL/LFPAK33封装的MOSFET。每个MOSFET电路都有一个跳线来使能/禁用NCV68061,以确保一次只有一个控制器处于活动状态。使用 3.3 V LDO NCV4294 为控制器的使能引脚 EN 供电。控制器将控制 N 沟道 MOSFET,使其像理想二极管一样工作,并阻止反向电流。

图 8. NCV68061 测试板的电路图

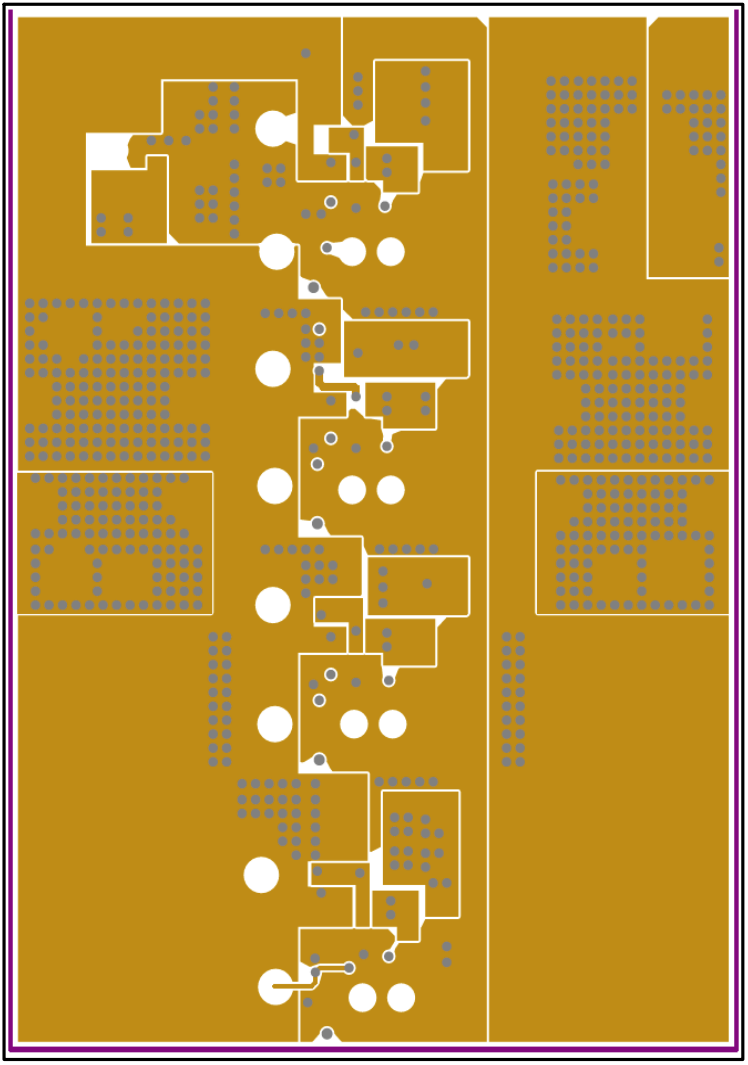

布局

该板是 4 层印刷电路板 (PCB)。输入和输出电流分布在顶层、第一内层和第二内层。跨多个层分布电流有助于减少损耗,并提高电路板的热性能。第二内层具有用于栅极信号和使能信号的走线。底层专用于 GND 平面。

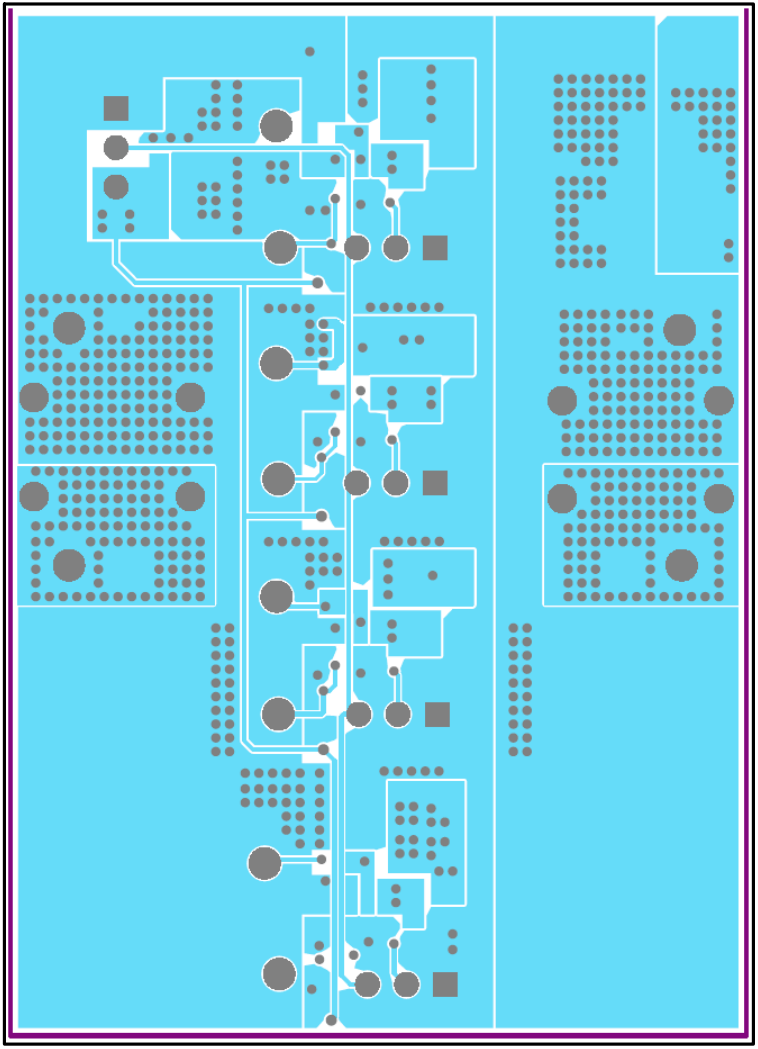

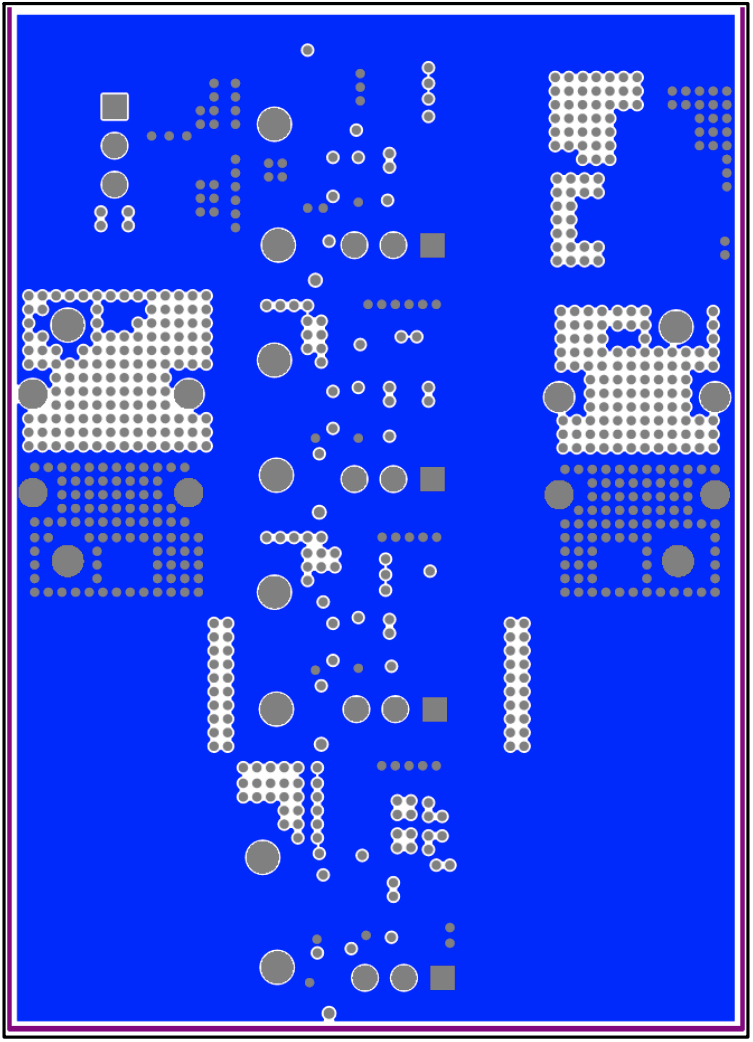

图 9. 顶层

图 10. 第一内层

图 11. 第二内层

图 12. 底层

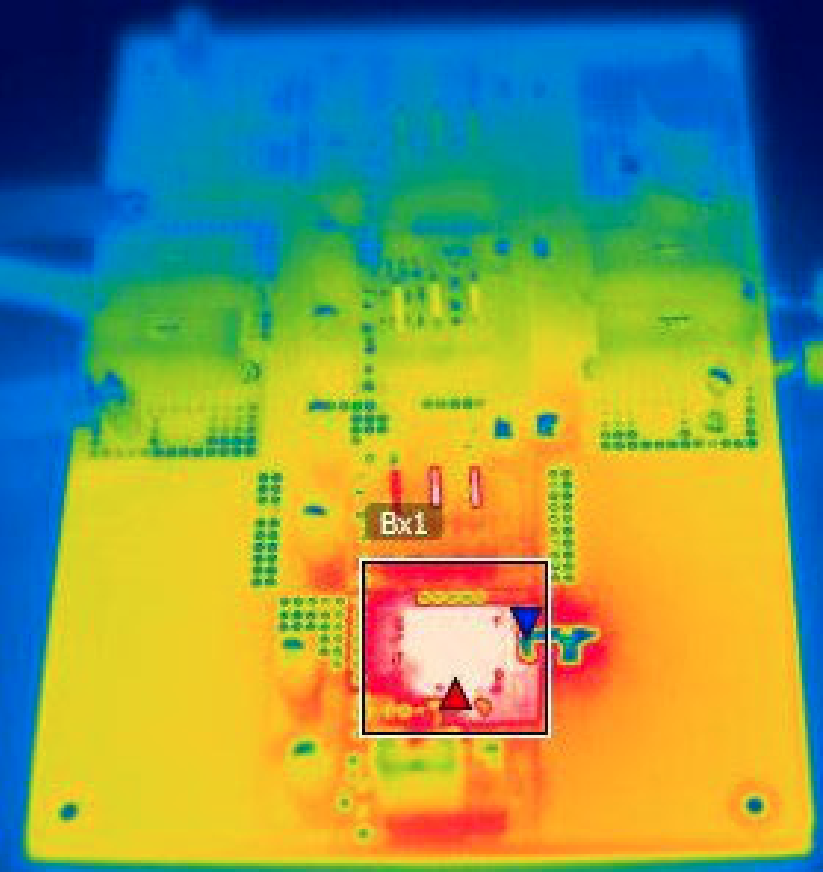

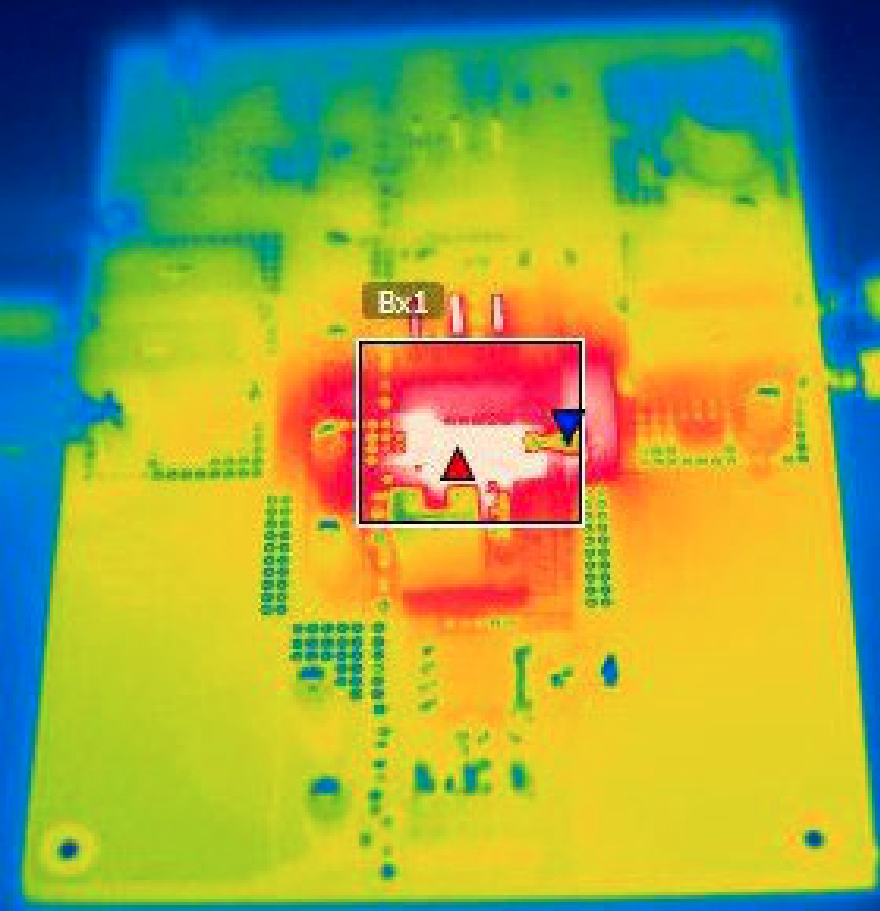

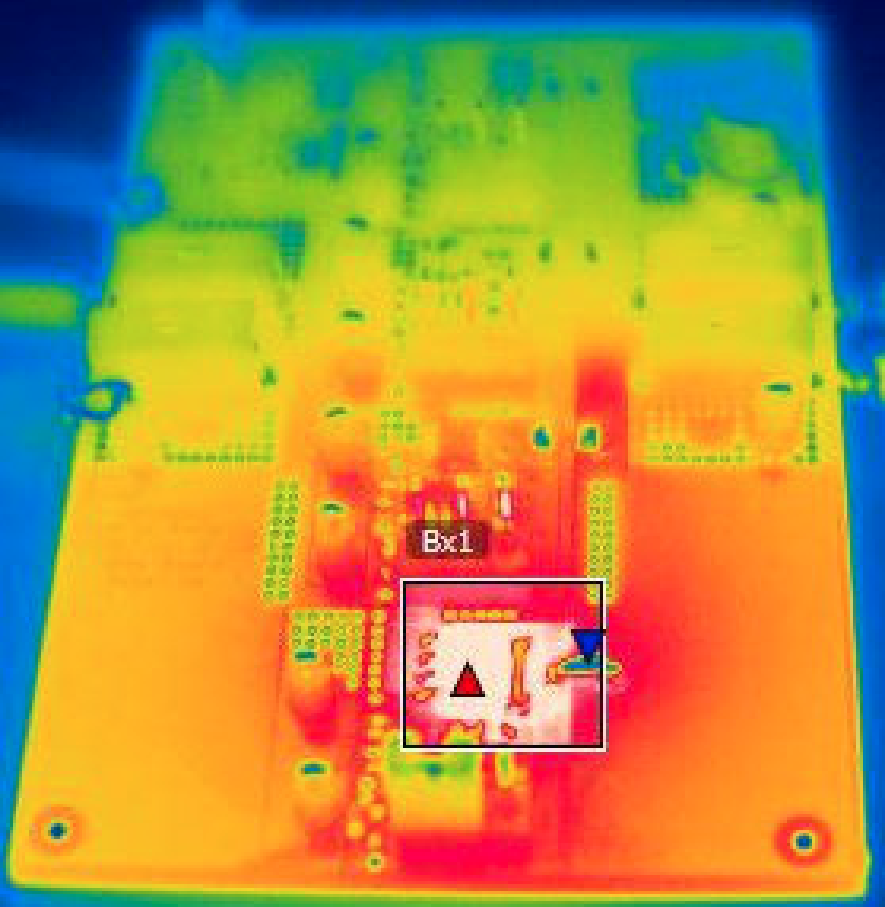

热测量

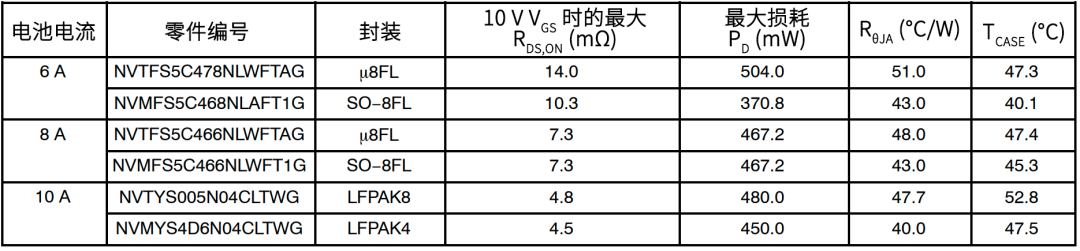

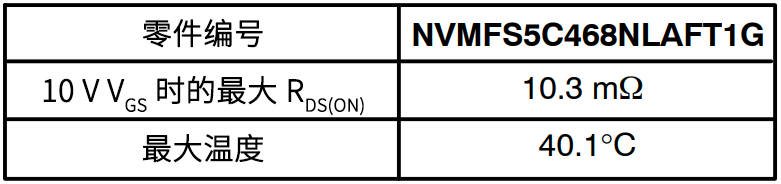

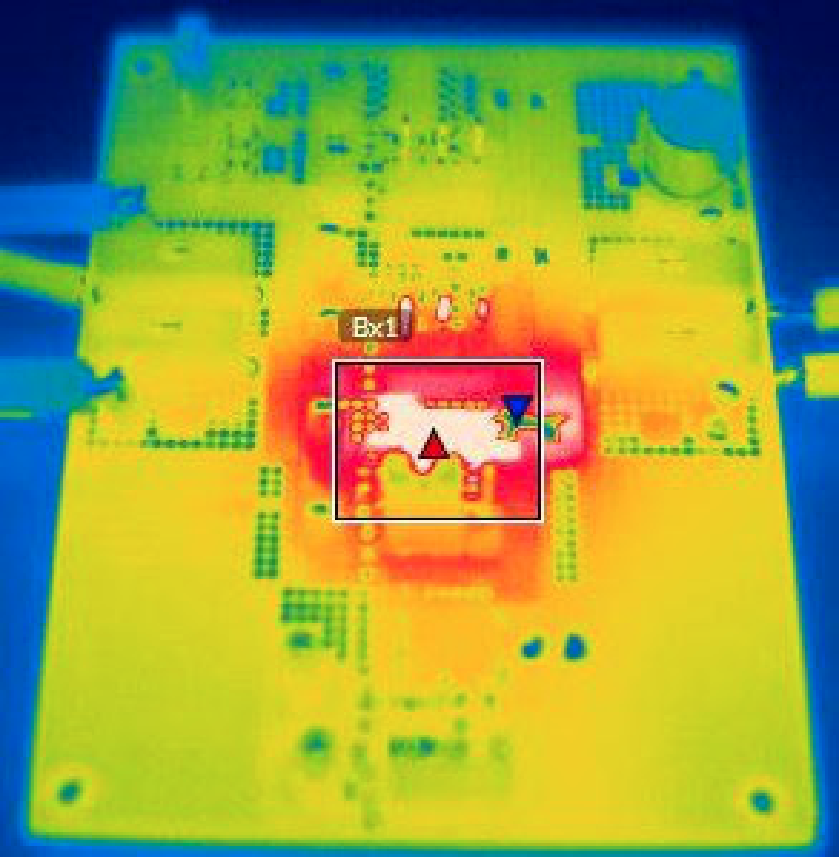

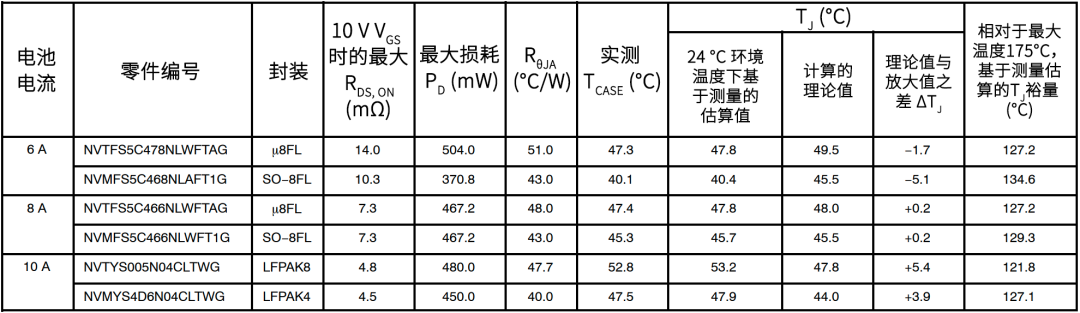

表 3. 接受评估的 MOSFET

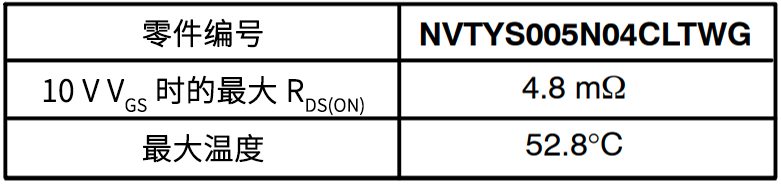

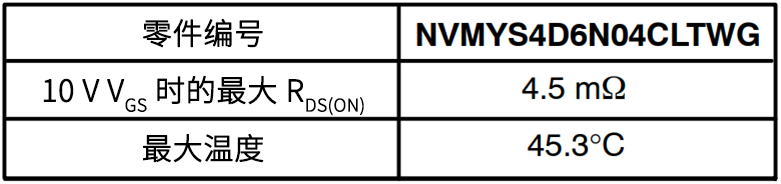

表 3 显示了用于热评估的 N 沟道 MOSFET。选择具有不同 RDS,ON 的 MOSFET,将功耗限制在 500 mW 左右。MOSFET 顶部壳温测量在 24°C 环境温度下进行,以评估不同输出电流(6 A、8 A 和 10 A)下 MOSFET 的热性能。使用 SO-8FL/LFPAK4 (5 x 6) 和 μ8FL/LFPAK8 (3 × 3) 封装的 MOSFET 进行评估。对每个负载电流进行两次测量,一次使用 5 x 6 封装,另一次使用 3 x 3 封装。

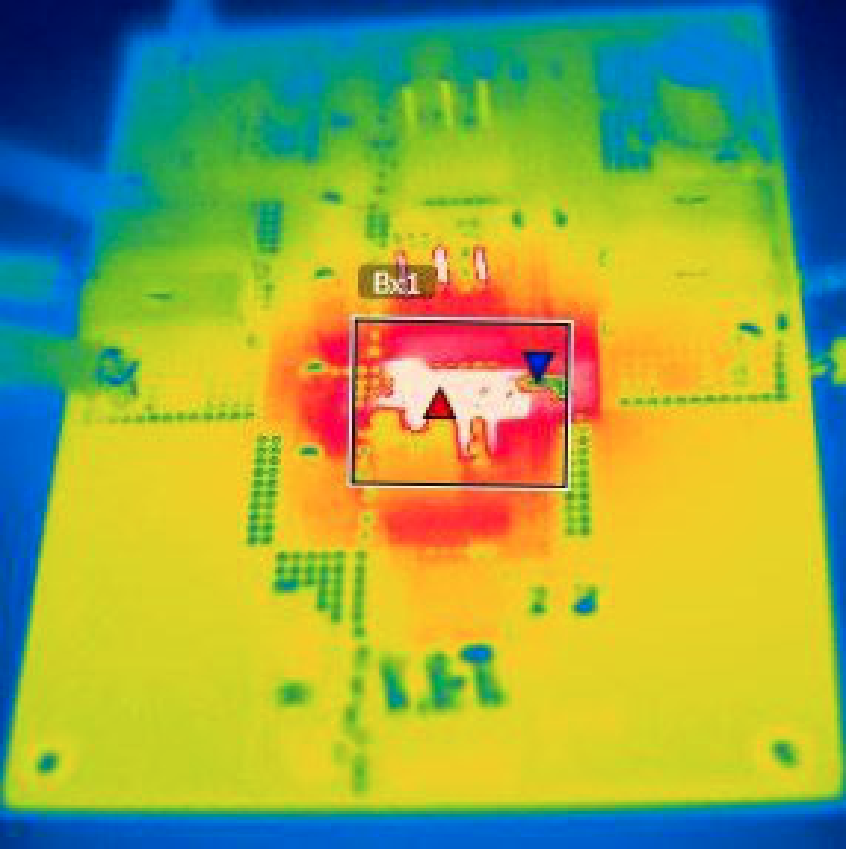

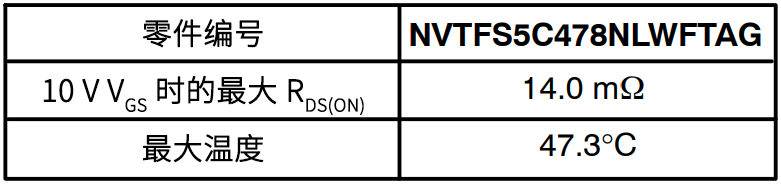

图 13. 6 A、μ8FL

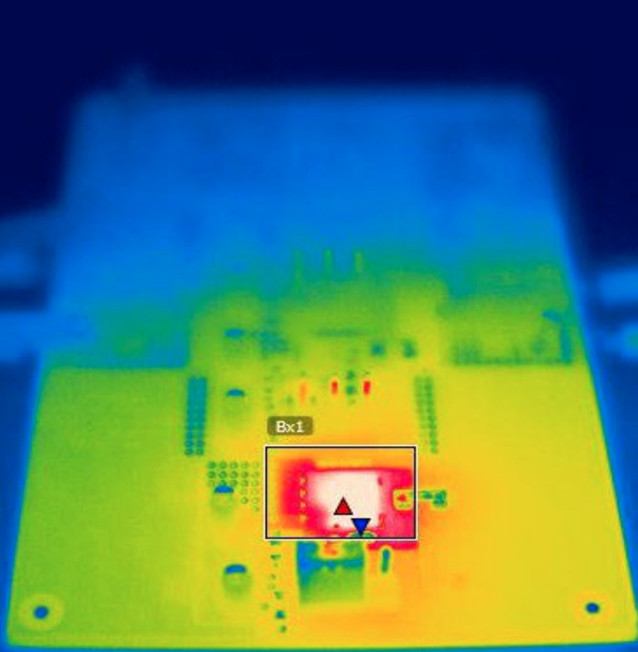

图 14. 6 A、SO-8FL

图 15. 8 A、μ8FL

图 16. 8 A、SO-8FL

图 17. 10 A、LFPAK8

图 18. 10 A、LFPAK4

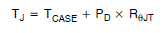

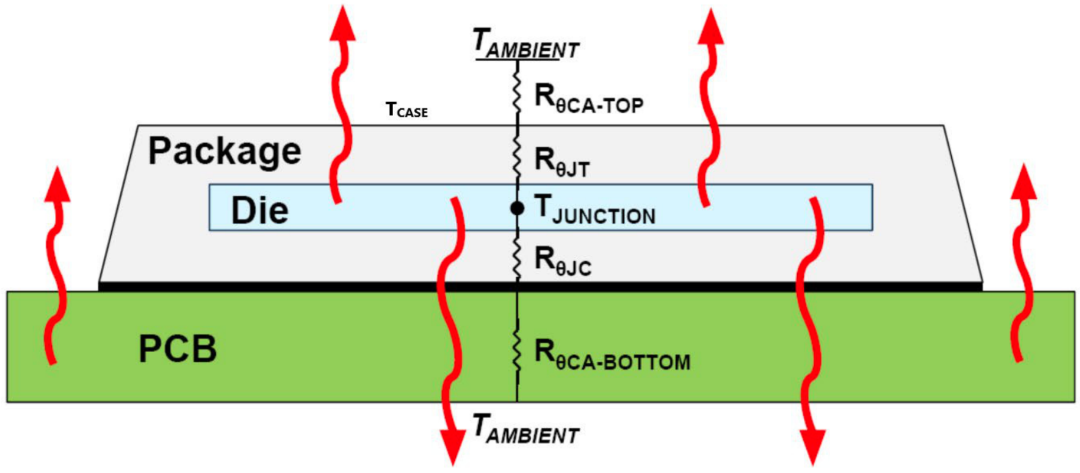

有了从热测量获得的顶部壳温和计算出的功耗,便可使用公式 1 计算结温 TJ。

(公式1)

TJ = MOSFET 的结温

TCASE = 热像仪测得的封装顶部温度

PD = MOSFET 的功耗

RθJT = MOSFET 顶部外壳和结之间的热阻

图 19. MOSFET 的等效热阻

RθJT 的值不是固定的,它取决于热边界条件,如 PCB 布局、MOSFET 的散热系统(裸露焊盘等)和其他参数,因此数据表未提供此值。RθJT 是一个 < 1°C/W 的小数字,因为大部分热量会通过封装底部的裸露焊盘从结流向 PCB。因此,没有多少热量从结流向 MOSFET 顶部,可以认为 TJ 和 TCASE 的温差不大。为了确定 TJ,本应用笔记假设 RθJT 为 1°C/W。

注意:1°C/W 对于 3 × 3 和 5 × 6 封装是一个非常保守的假设。其他封装会有不同的热阻。

估算结温 TJ

下面使用测得的 TCASE 和 MOSFET 的实际功耗来计算 TJ。下一步将根据数据表的规格进行理论计算,并将结果与使用实测数据进行的计算进行比较,以确认 TJ 的理论计算和实际计算是否一致。所有计算均使用 μ8FL (3 × 3) 封装的 MOSFET NVTFS5C478NLWFTAG。

使用实测 TCASE 估算 TJ

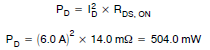

下面的计算使用从测量获得的值来估算 TJ。

● 负载电流 ILOAD = ID = 6.0 A

● 输入电压 Vin = 12.0 V

● 顶部外壳温度 TCASE = 47.3°C(从热测量获得)

● 10.0 V VGS 时的最大导通电阻 RDS,ON = 14.0 mΩ

● RθJT = 1.0°C/W(3 × 3 和 5 × 6 封装的假设值)

(公式2)

使用公式 1,

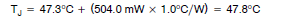

TJ 的理论计算

使用基于数据表规格的理论计算来确定 TJ。假设损耗为 500 mW,使用公式 3 来确定器件的 TJ。

(公式3)

● MOSFET 的结温 TJ

● MOSFET 工作环境温度 TA = 24.0°C

● MOSFET 的功耗 PD = 500.0 mW

● MOSFET 的结和环境之间的热阻 RθJA = 51.0°C/W(值来自数据表)

(公式4)

NVTFS5C478NLWFTAG 的 TJ,MAX 为 175.0°C,因此有 125.5°C 的裕量。

估算的 TJ 与理论计算值之差很小,为 1.7°C(49.5°C - 47.8°C)。在表 4 中,如以上计算所示,使用理论计算的 TJ 和实测的 TCASE、RθJT、PD 来估算不同负载和封装下的 TJ。

表 4. 建议 MOSFET 的 TJ 计算值与负载电流

● 在 6 A 负载电流时,5 × 6 封装的 TJ 裕量比 3 × 3 封装高约 5.8%。

● 在 8 A 负载电流时,5 × 6 封装的裕量比 3 × 3 封装高约 1.6%。两款器件封装不同,但使用相同的芯片,因此 TJ 没有太大区别。

● 在 10 A 时,5 × 6 封装的裕量比 3 × 3 封装高约 4.3%。

● 同样,除了一款 10 A MOSFET 有大约 5.4°C 的差异外,理论 TJ 与估算值的差异并不显著。这表明,对于此特定测试设置,数据表中的 RθJA 是可靠的。 买电子元器件现货上唯样商城

● 从实际应用角度看,数据表中使用 2 oz. 铜焊盘和较大面积电路板测量 RθJA 似乎不太现实,但它与上面估算的 TJ 差异很小,这表明 RθJA 与针对散热优化的 4 层测试板非常匹配。

● 结果显示,由于封装较大 (5 × 6),热量得到有效消散并分布到整个器件上,因此其裕量更好。从散热角度看,较大封装的器件适合负载电流较高的应用以及环境温度较高的应用。

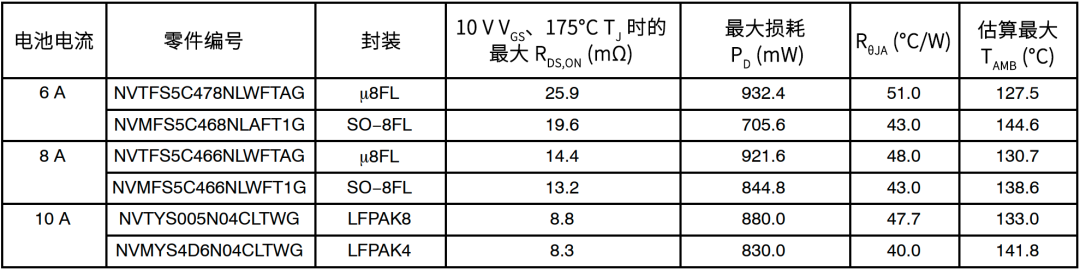

估算最大环境温度 TA

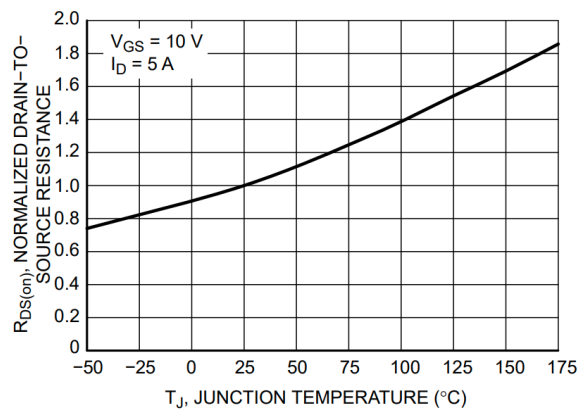

前面的计算表明,数据表的 RθJA 与 NCV68061 测试板非常匹配,因此可以计算 MOSFET 工作的最大环境温度。

图 20 显示了 NVTFS5C478NLWFTAG 的 RDS,ON 相对于 TJ 的变化。在 175°C 结温时,最大 RDS,ON 比 25°C 结温时高大约 1.85 倍。因此,最大 RDS,ON 为 1.85 × 14 mΩ = ~25.9 mΩ。

图 20. NVTFS5C478NLWFTAG 导通电阻随温度的变化

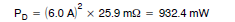

175°C 结温和 6 A 负载电流下的功耗如下:

RθJA = 51.0°C/W,结和环境之间的温差可以计算如下:

温差 ΔT = 51.0°C/W × 932.4 mW = 47.5°C

最大 TA = TJ - ΔT

最大 TA = 175.0°C - 47.5°C = 127.5°C

从上面的例子可知,MOSFET 可以在最大 127.5°C 的环境温度下工作。如果环境温度超出该计算值,则意味着 TJ 已达到 175°C 以上。

MOSFET 芯片本身可以在高于 175°C 的温度下工作,但由于封装塑封料的限制,以及为了确保长期运行可靠性,MOSFET 数据表规定最大 TJ 为 175°C。高于最大 TJ 的温度将导致器件行为无法保证,而且这也意味着器件在规格范围之外运行。

表 5 显示了各种 MOSFET 在不同负载电流下的估算最大环境温度,考虑结温为 175°C。

表 5. 估算最大 TAMB

总结

极性反接保护电路是车辆中任何 ECU 的核心构建模块之一。本文讨论了几种极性反接保护技术,包括二极管、P 沟道 MOSFET 和 N 沟道 MOSFET。本文比较了所有这些技术,并重点指出了每种技术的优缺点。此外,本文提供了 MOSFET 选型指南以支持 MOSFET 选择过程,并且给出了一个推荐器件清单。负载电流从 6 A 到 10 A 的热测量表明,从散热角度看,5×6 封装表现良好,原因是其封装和芯片更大,RDS,ON 和功率损耗比 3×3 封装要低。另外,与较小的芯片相比,较大的芯片有助于更好地散热。尽管如此,表 3 显示 5×6 和 3×3 封装的最大 TJ 的裕量差异并不显著。根据应用需求和所使用的散热系统,5×6 和 3×3 封装的 MOSFET 均可选用。

理论计算的和实际估算的结温 TJ 没有显著差异,数据表中给出的 RθJA 是实际值,可用来在实际应用中执行热分析。使用上文所示的计算,RθJA 有助于计算 MOSFET 可运行的最大环境温度。

审核编辑:汤梓红

-

电源反接保护芯片怎么接2024-09-19 1967

-

常用的电压反接保护电路分享2023-03-08 5319

-

MOSFET选得好,极性反接保护更可靠2023-02-23 1072

-

怎样去设计一种防反接保护电路2021-11-15 1936

-

MOS管型防反接保护电路图2021-10-29 3586

-

MOS管 电源防反接2021-10-22 1800

-

MOS管型防反接保护电路设计2019-12-10 5445

-

NMOS管进行极性反接保护的几个疑问2019-07-13 6273

-

反向极性保护电路设计2018-09-04 3202

-

【转帖】防反接保护电路2017-12-15 4827

-

关于防反接保护电路设计的讨论2015-02-03 11461

-

保护运放电源电压极性反接措施及其电路图2011-06-22 4401

-

输出负载的反极性保护-(LSD)2009-11-21 5946

-

LAS6351极性反接电路图2009-05-12 891

全部0条评论

快来发表一下你的评论吧 !