MOSFET的失效机理

描述

MOSFET等开关器件可能会受各种因素影响而失效。因此,不仅要准确了解产品的额定值和工作条件,还要全面考虑电路工作中的各种导致失效的因素。本系列文章将介绍MOSFET常见的失效机理。

什么是SOA(Safety Operation Area)?

SOA是“Safety Operation Area”的缩写,意为“安全工作区”。要想安全使用MOSFET,就需要在SOA范围内使用MOSFET,超过这个范围就有可能造成损坏。在SOA范围之外工作时造成的损坏称为“SOA失效”。例如,SJ MOSFET(Super Junction MOSFET)R6024KNX的SOA如下所示:

SJ MOSFET R6024KNX的SOA

SOA由纵轴上的漏极电流ID和横轴上的漏源电压VDS来表示。也就是说,VDS、ID及它们的乘积(功率损耗PD)、以及二次击穿区决定了MOSFET的安全工作范围。另外,施加功率的脉冲宽度PW也是决定SOA的重要因素。SOA划分为图中所示的(1)~(5)个区域。

SOA的区域划分、限制以及与失效之间的关系

下面介绍一下图中的区域(1)~(5)。

■区域(1):漏极电流ID受MOSFET的导通电阻RDS(ON)限制的区域

是指即使施加的VDS小于绝对最大额定值,ID也会受到RDS(ON)限制的区域。根据欧姆定律I=V/R,ID只能流到红线位置。 ※图中的区域是VGS=10V时的示例

■区域(2):由施加脉冲时漏极电流的绝对最大额定值IDP决定的区域

(2)的绿线是规格书中规定的IDP的绝对最大额定值。当然,绝对最大额定值是绝对不能超过的,因此当IDP超过该值时是无法使用的。如果在超过该值的范围(电流值)使用,由于超出了保证的工作范围,因此可能会造成损坏。

■区域(3):热限制区域

这是由MOSFET的容许损耗PD决定的区域。受施加功率的脉冲宽度PW和瞬态热阻的限制。只要在该范围内,Tj通常不会超过绝对最大额定值TjMAX,因此可以安全使用。但是请注意,该线会因环境温度、MOSFET的实际安装条件和散热条件等因素而异。此外,作为开关使用MOSFET时,可能会瞬间被施加高电压和大电流,因此即使在开关的瞬态状态下也必须注意不要超过区域(3)的限制。

■区域(4):二次击穿区域

当在施加高电压的状态下流过电流时,元器件内部的局部可能会流过大电流并造成损坏,这称为“二次击穿”。这条线是用来防止造成二次击穿状态的限制线。与区域(3)的热限制区域一样,二次击穿区域也受环境温度等因素的影响。

■区域(5):由MOSFET漏源电压的绝对最大额定值VDSS决定的区域

这是规格书中规定的受VDSS限制的区域,如果超过这个区域,就可能发生击穿并造成损坏。需要注意的是,由反激电压和寄生电感引起的电压变化,可能会瞬间超过该限制。

什么是雪崩击穿

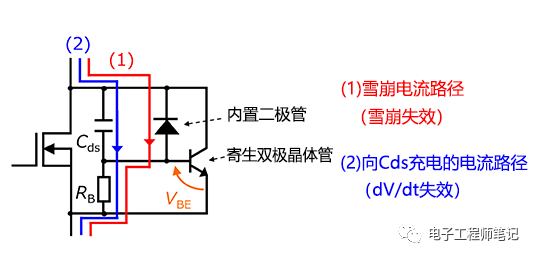

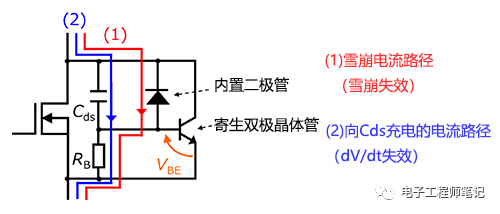

当向MOSFET施加高于绝对最大额定值BVDSS的电压时,就会发生击穿。当施加高于BVDSS的高电场时,自由电子被加速并带有很大的能量。这会导致碰撞电离,从而产生电子-空穴对。这种电子-空穴对呈雪崩式增加的现象称为“雪崩击穿”。在这种雪崩击穿期间,与 MOSFET内部二极管电流呈反方向流动的电流称为“雪崩电流IAS”,参见下图(1)。

MOSFET的雪崩失效电流路径示意图(红色部分)

雪崩失效:短路造成的失效

如上图所示,IAS会流经MOSFET的基极寄生电阻RB。此时,寄生双极型晶体管的基极和发射极之间会产生电位差VBE,如果该电位差较大,则寄生双极晶体管可能会变为导通状态。一旦这个寄生双极晶体管导通,就会流过大电流,MOSFET可能会因短路而失效。

雪崩失效:热量造成的失效

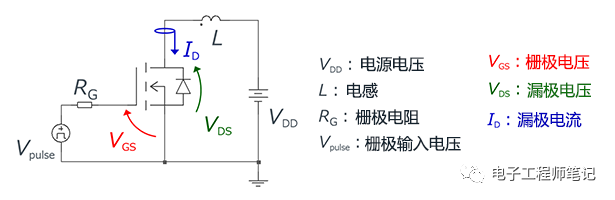

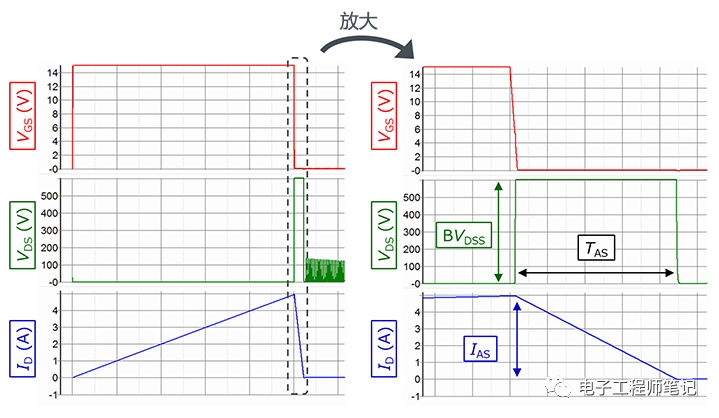

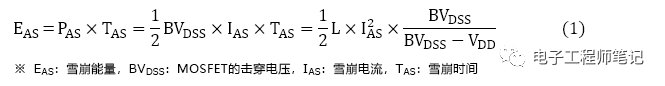

在雪崩击穿期间,不仅会发生由雪崩电流导致寄生双极晶体管误导通而造成的短路和损坏,还会发生由传导损耗带来的热量造成的损坏。如前所述,当MOSFET处于击穿状态时会流过雪崩电流。在这种状态下,BVDSS被施加到MOSFET并且流过雪崩电流,它们的乘积成为功率损耗。这种功率损耗称为“雪崩能量EAS”。雪崩测试电路及其测试结果的波形如下图所示。此外,雪崩能量可以通过公式(1)来表示。

雪崩测试的电路简图

雪崩测试中MOSFET的电压和电流波形

雪崩能量公式

一般情况下,有抗雪崩保证的MOSFET,在其规格书中会规定IAS和EAS的绝对最大额定值,因此可以通过规格书来了解详细的值。在有雪崩电流流动的工作环境中,需要把握IAS和EAS的实际值,并在绝对最大额定值范围内使用。

引发雪崩击穿的例子包括反激式转换器中的MOSFET关断时的反激电压和寄生电感引起的浪涌电压等。针对反激电压引起的雪崩击穿,对策包括在设计电路时采用降低反激电压的设计或使用具有更高耐压性能的MOSFET。而针对寄生电感引起的雪崩击穿,改用引脚更短的封装的MOSFET或改善电路板布局以降低寄生电感等都是比较有效的措施。

什么是dV/dt失效

如下图(2)所示,dV/dt失效是由于MOSFET关断时流经寄生电容Cds的瞬态充电电流流过基极电阻RB,导致寄生双极晶体管的基极和发射极之间产生电位差VBE,使寄生双极晶体管导通,引起短路并造成失效的现象。通常,dV/dt越大(越陡),VBE的电位差就越大,寄生双极晶体管越容易导通,从而越容易发生失效问题。

MOSFET的dV/dt失效电流路径示意图(蓝色部分)

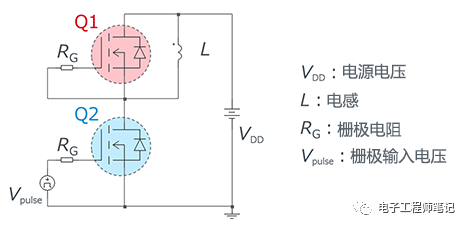

此外,在逆变器电路或Totem-Pole PFC等上下桥结构的电路中,反向恢复电流Irr会流过MOSFET。受该反向恢复电流影响的dV/dt,可能会使寄生双极晶体管误导通,这一点需要注意。dV/dt失效与反向恢复特性之间的关系可以通过双脉冲测试来确认。双脉冲测试的电路简图如下:

双脉冲测试的电路简图

关于在双脉冲测试中的详细情况,请参考R课堂基础知识 评估篇中的“通过双脉冲测试评估MOSFET的反向恢复特性”。

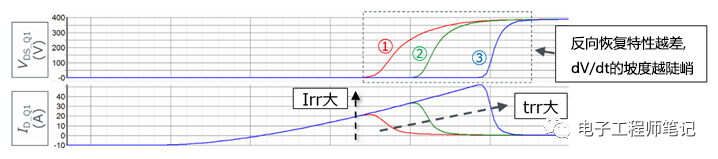

dV/dt和反向恢复电流的仿真结果如下图所示。设MOSFET①~③的栅极电阻RG和电源电压VDD等电路条件相同,仅反向恢复特性不同。图中列出了Q1从续流工作转换到反向恢复工作时的漏源电压VDS和漏极电流(内部二极管电流)ID。

双脉冲测试的仿真结果

一般情况下,与MOSFET①相比,MOSFET③可以说是“反向恢复特性较差(Irr和trr大)”的产品。从这个仿真结果可以看出,反向恢复特性越差,dV/dt的坡度就越陡峭。这一点通过流经电容器的瞬态电流通常用I=C×dV/dt来表示也可以理解。此外,在上述仿真中,Irr的斜率(di/dt)均设置为相同条件,但当di/dt陡峭时,dV/dt也会变陡峭。

综上所述,可以说,在桥式电路中使用MOSFET时,反向恢复特性越差的MOSFET,发生MOSFET的dV/dt失效风险越大。

至此,我们已经介绍了MOSFET的SOA失效、MOSFET的雪崩失效和MOSFET的dV/dt失效。要想安全使用MOSFET,首先不能超过MOSFET规格书中的绝对最大额定值,另外,了解这些MOSFET的失效机理之后再进行电路设计和工作条件设置是非常重要的。

审核编辑:汤梓红

-

详解半导体集成电路的失效机理2025-03-25 2665

-

保护器件过电应力失效机理和失效现象浅析2023-12-14 2301

-

MOSFET的失效机理:dV/dt失效和雪崩失效2023-04-15 3266

-

MOSFET的失效机理:什么是雪崩失效2023-02-13 3431

-

MOSFET的失效机理 —总结—2022-07-26 5755

-

一文详解MOSFET的失效机理2022-05-16 5782

-

MOSFET的失效机理2022-03-19 3592

-

电阻器常见的失效模式与失效机理2022-02-10 1097

-

IGBT传统防失效机理是什么?2021-03-29 2122

-

元器件的长期储存的失效模式和失效机理2017-10-19 1299

-

元器件长期储存的失效模式和失效机理2017-10-17 1350

-

电容的失效模式和失效机理2011-12-03 9303

-

电容器的常见失效模式和失效机理【上】2011-11-18 4312

全部0条评论

快来发表一下你的评论吧 !