FPGA中何时用组合逻辑或时序逻辑

可编程逻辑

描述

本系列将带来FPGA的系统性学习,从最基本的数字电路基础开始,最详细操作步骤,最直白的言语描述,手把手的“傻瓜式”讲解,让电子、信息、通信类专业学生、初入职场小白及打算进阶提升的职业开发者都可以有系统性学习的机会。

系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。后续会陆续更新 Xilinx 的 Vivado、ISE 及相关操作软件的开发的相关内容,学习FPGA设计方法及设计思想的同时,实操结合各类操作软件,会让你在技术学习道路上无比的顺畅,告别技术学习小BUG卡破脑壳,告别目前忽悠性的培训诱导,真正的去学习去实战应用,这种快乐试试你就会懂的。话不多说,上货。

在FPGA中何时用组合逻辑或时序逻辑

在设计FPGA时,大多数采用Verilog HDL或者VHDL语言进行设计(本文重点以verilog来做介绍)。设计的电路都是利用FPGA内部的LUT和触发器等效出来的电路。

数字逻辑电路分为组合逻辑电路和时序逻辑电路。时序逻辑电路是由组合逻辑电路和时序逻辑器件构成(触发器),即数字逻辑电路是由组合逻辑和时序逻辑器件构成。所以FPGA的最小单元往往是由LUT(等效为组合逻辑)和触发器构成。

在进行FPGA设计时,应该采用组合逻辑设计还是时序逻辑?这个问题是很多初学者不可避免的一个问题。

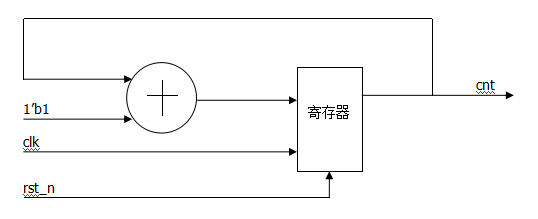

设计两个无符号的8bit数据相加的电路。

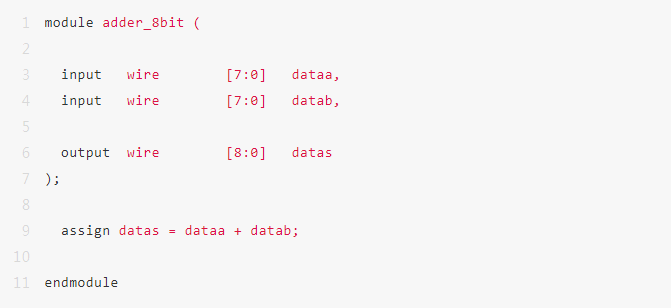

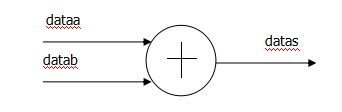

组合逻辑设计代码:

对应的电路为:

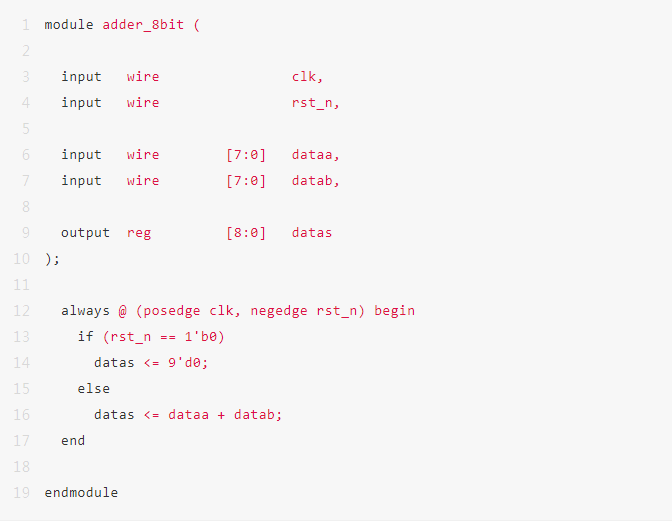

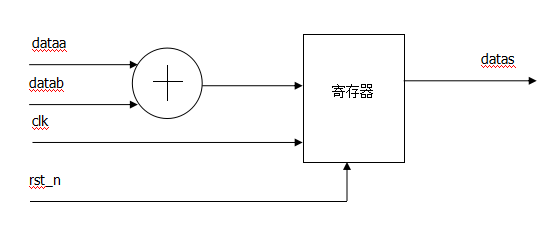

时序逻辑对应代码为:

对应的电路为:

可以思考一下,这个两种设计方法都没有任何错误。那么在设计时应该用哪一种呢?

在设计时,有没有什么规定必须要用组合逻辑或者时序逻辑?例如:在verilog中,在always中被赋值了就必须是reg类型,assign赋值了就必须是wire类型。很遗憾的是,目前没有任何的规定。

下面几点笔者平时自己做设计的经验,在这里分享一下:

带有反馈的必须用时序逻辑

何为带有有反馈?即输出结果拉回到输入。

自加一计数器。

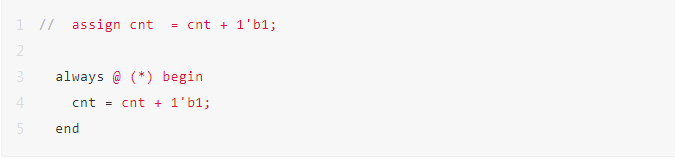

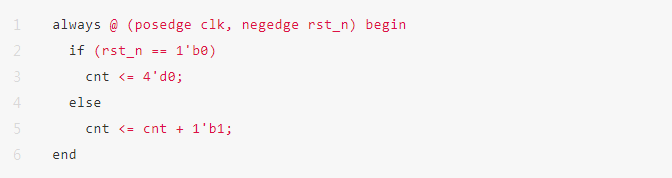

代码为:

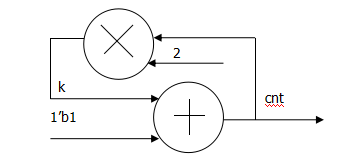

对应的电路为:

这种电路在工作时,就会出现无限反馈,不受任何控制,一般情况下,我们认为结果没有任何意义。

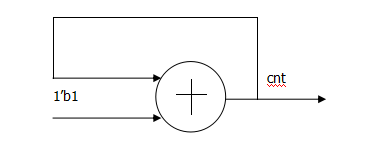

和上面的情况类似的还有取反。

类似情况还有很多就不在一一列举。

上述说的情况都是直接带有反馈,下面说明间接反馈。

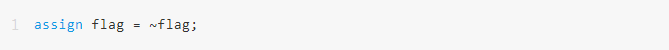

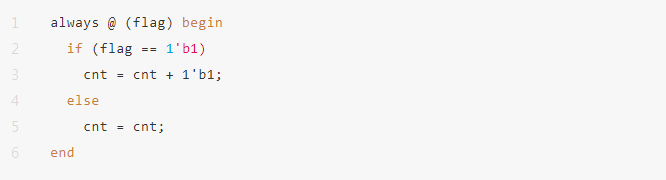

代码为:

从代码上来看,没有什么明确反馈,下面看实际对应的电路。

从实际的电路上来看,一旦运行起来,还是会出现无限反馈,不受任何控制。

还有一种情况是带有控制的反馈。

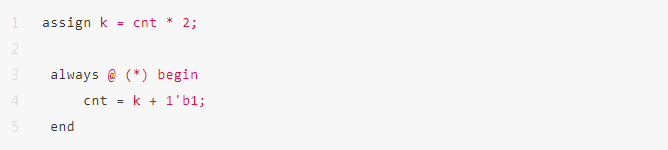

设计代码为:

这个电路可以等效为:

在flag等于1期间,此电路依然会无限制的反馈,无法确定在此期间进行了多少次反馈。

从代码的角度理解是flag变化一次,加一次。可是对应于电路后,和预想的是不相同的。

说了这么多的这么多不对的情况,下面考虑正确的情况。

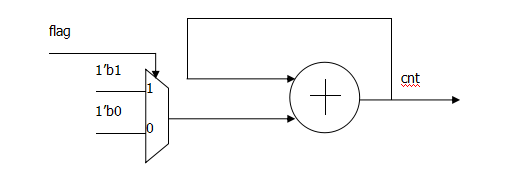

设计代码为:

在上述的电路中,clk每来一个上升沿,cnt的数值增加一。可以用作计时使用。

利用寄存器将反馈路径切换即可。此时的反馈是可控制,并且此时的结果就有了意义。

其他的反馈中,加入寄存器即可。而加入寄存器后,就变为时序逻辑。

根据时序对齐关系进行选择

在很多的设计时,没有反馈,那么应该如何选择呢?

举例说明:输入一个八位的数据(idata),然后将此八位数据进行平方后,扩大2倍,作为输出。要求输出结果(result)时,将原数据同步输出(odata),即数据和结果在时序上是对齐的。

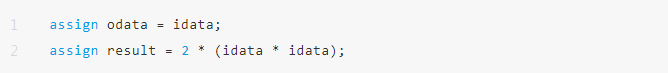

设计代码为:

这种设计方法是可以的,因为都采用组合逻辑设计,odata和result都是和idata同步的,只有逻辑上的延迟,没有任何时钟的延迟。

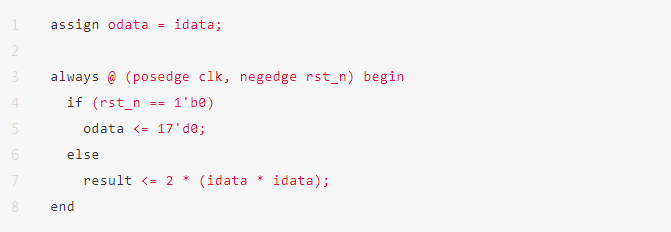

另外一种设计代码为:

这种设计方法为错误,odata的输出是和idata同步的,而result的输出将会比idata晚一拍,最终导致result要比odata晚一拍,此时结果为不同步,设计错误。

修改方案为:将result的寄存器去掉,修改为组合逻辑,那就是第一种设计方案。第二种为将odata也进行时序逻辑输出,那么此时odata也将会比idata延迟一拍,最终结果为result和odata同步输出。

根据运行速度进行选择

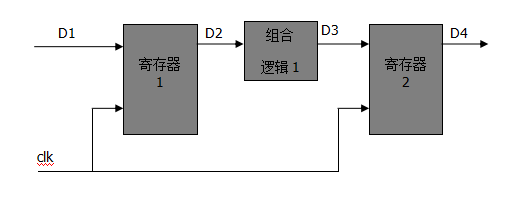

在数字逻辑电路中,中间某一部分为组合逻辑,两侧的输入或者输出也会对延迟或者输入的数据速率有一定的要求。

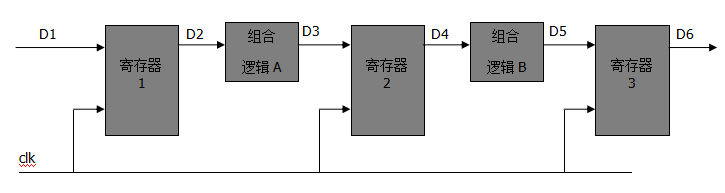

组合逻辑1越复杂延迟越大,而导致的结果就是clk的时钟速率只能降低,进而导致设计结果失败。

当组合逻辑1无法进行优化时,还想要达到自己想要的速度时,我们可以进行逻辑拆分,增加数据的输出潜伏期,增加数据的运行速度。

将组合逻辑1的功能拆分为组合逻辑A和组合逻辑B,此时,输入的数据得到结果虽然会多延迟一拍,但是数据的流速会变快。

那么这个和选用组合逻辑和时序逻辑有什么关系呢?

举例说明:目前要设计模块A,不涉及反馈,不涉及时序对齐等,可以采取组合逻辑设计也可以采用时序逻辑设计。

模块A的输出连接到模块B,经过一些变换(组合逻辑N)连接到某个寄存器K上。如果模块A采用组合逻辑,那么模块A的组合逻辑和模块B到达寄存器K之前的组合逻辑N会合并到一起。那么此时组合逻辑的延迟就会变得很大,导致整体设计的时钟速率上不去。

当运行速率比较快时,建议对于复杂的组合逻辑进行拆分,有利于时序分析的通过。

在上述的三个规则中,第一个和第二个用的是最多的,第三个在设计时,有时不一定能够注意到,当出现时序违例时,知道拆分能够解决问题就可以。

编辑:黄飞

-

一文解析FPGA的片上资源使用情况(组合逻辑及时序逻辑)2018-04-18 18995

-

FPGA之组合逻辑与时序逻辑、同步逻辑与异步逻辑的概念2022-12-01 1590

-

soc中的组合逻辑和时序逻辑应用说明2023-08-30 2088

-

FPGA实战演练逻辑篇47:消除组合逻辑的毛刺2015-07-08 4302

-

勇敢的芯伴你玩转Altera FPGA连载25:组合逻辑与时序逻辑2017-11-17 3752

-

【技巧分享】时序逻辑和组合逻辑的区别和使用2020-03-01 2764

-

在FPGA中何时用组合逻辑或时序逻辑2023-03-06 923

-

为什么FPGA可以用来实现组合逻辑电路和时序逻辑电路呢?2023-04-23 2993

-

FPGA中组合逻辑和时序逻辑的区别2017-11-20 9317

-

组合逻辑电路和时序逻辑电路比较_组合逻辑电路和时序逻辑电路有什么区别2018-01-30 95153

-

数字设计FPGA应用:时序逻辑电路FPGA的实现2019-12-05 3759

-

FPGA时序逻辑和组合逻辑的入门基础教程2020-12-09 1258

-

组合逻辑电路和时序逻辑电路的区别和联系2023-03-14 9332

-

【教程分享】在FPGA中何时用组合逻辑或时序逻辑?2023-03-21 1951

-

什么是组合逻辑电路和时序逻辑电路?它们之间的区别是什么2024-03-26 7163

全部0条评论

快来发表一下你的评论吧 !