一文详解门控时钟

描述

门控时钟

当寄存器组的输出端没有驱动或没有变化时,可以关掉寄存器组的时钟来减少动态功耗,此谓门控时钟 (Clock Gating, CG) 技术。

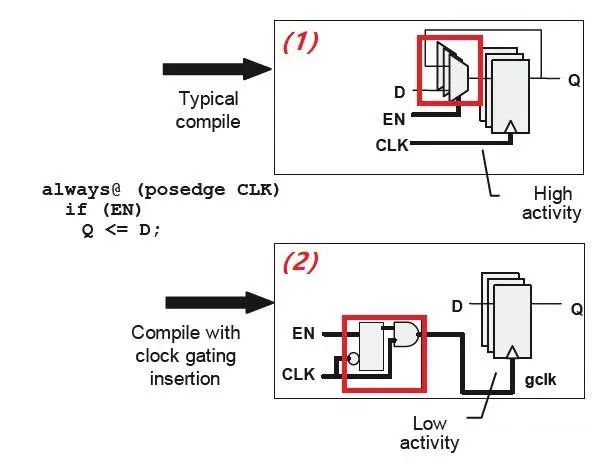

最简单的一个带 EN 端的 D 触发器的 Verilog 逻辑描述如下:

always @(posedge CLK)

if (EN)

Q <= D ;

当不采用门控时钟结构时,DC 综合时会在触发器的输入端增加为带反馈端的多路选择器电路,如下图 (1) 所示。

当采用门控时钟结构时,DC 综合时仅会在触发器的时钟端增加一个时钟门控单元 (CG cell),而没有多路选择器结构,如下图 (2) 所示。

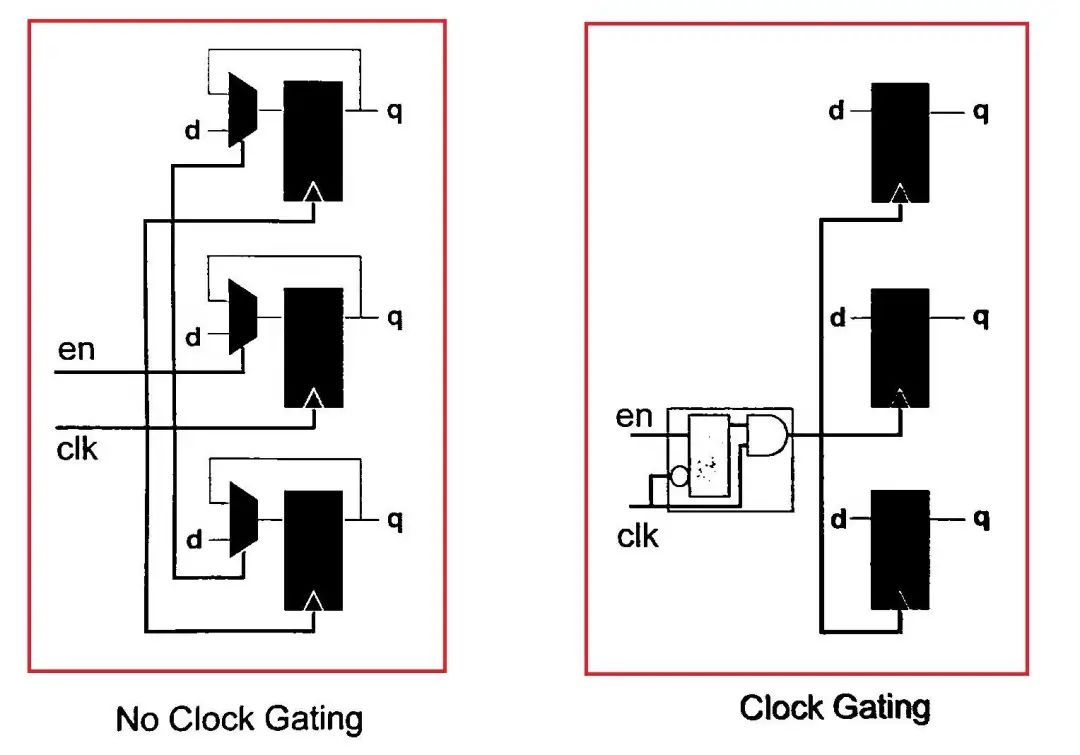

当多个寄存器组共用一个控制端时,结构上的优化尤为明显,如下图所示:

综上所述,门控时钟的优点有:

(1) 寄存器时钟端翻转率降低,动态功耗降低。

(2) 时钟树网络开关率降低,动态功耗降低。

(3) CG 扇出越大,结构上节省的选择器越多,硬件资源消耗越少。

(4) 相比于 PG (Power Gating),CG 结构相对简单,在综合时可自动插入。

产生门控时钟

产生门控时钟的条件为:

寄存器组共用同一个时钟;

寄存器组的控制端都是同步的;

寄存器组都是由同一个变量中推断而来的。

自动插入 CG

DC 综合时,使用以下命令与参数,设计中符合要求的寄存器便会被综合成带 CG 结构的触发器。

compile_ultra -gate_clk

DC 综合时插入的 CG 又分为离散的 CG cell 与集成的 CG cell (ICG)。离散的 CG cell 使用 Latch 与基本逻辑门单元组合而成,集成的 CG cell 是工艺厂家提供的一个带有时钟门控功能的特殊单元。

DC 中插入离散的 CG 命令为:

# 使用带 latch 结构的离散的 CG

set_clock_gating_style -sequential_cell latch

# 离散的 CG 中指定具体的 latch cell "lib_cell"

set_clock_gating_style -sequential_cell latch:lib_cell

DC 中插入没有 Latch 结构的离散 CG 时,命令如下:

# 使用或门逻辑,生成上升沿工作的寄存器的时钟门控

set_clock_gating_style -sequential_cell none -pos {or}

因为使用与门生成 CG 时在时钟上升沿容易出现毛刺,使用或门生成 CG 时在时钟下降沿容易出现毛刺,所以参数 -pos 一般配合 {or} 使用,-neg 一般配合 {and} 使用。

# 使用与门逻辑,生成下升沿工作的寄存器的时钟门控

set_clock_gating_style -sequential_cell none -neg {and}

假如 -sequential_cell 与 -pos/-neg 选项同时使用,那么两个选项指定的 CG 电路结构应该保持一致,例如:

set_clock_gating_style -sequential_cell latch -neg {latch and}

set_clock_gating_style -sequential_cell none -neg {and}

DC 中插入 ICG 时,命令如下:

# 使用集成的 CG cell

set_clock_gating_style -negative_edge_logic {integrated}

# 指定使用具体的集成 CG cell "lib_cell"

set_clock_gating_style -negative_edge_logic {integrated:lib_cell}

手动插入 CG

如果设置了自动产生时钟门控(-gate_clk),DC 综合时会对 RTL 设计中符合要求的寄存器进行时钟门控。但如果在 RTL 设计中,人为的编写时钟门控逻辑,DC 对此不会插入 CG ,如以下 Verilog 描述。

assign gated_clk = clk & en ;

always @(posedge gated_clk or negedge rstn) begin

if (!rstn)

data_out <= 8'b0 ;

else

data_out <= data_out + 1'b1;

end

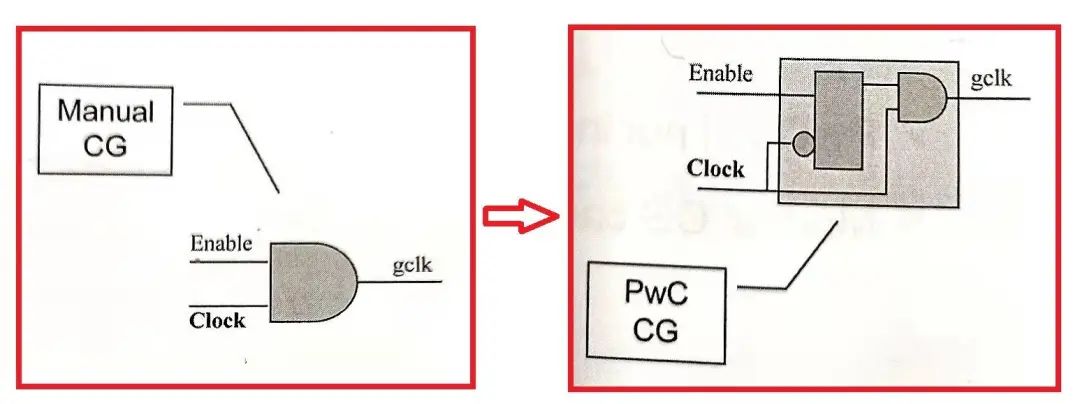

人为编写的时钟门控逻辑中,时钟很容易出现毛刺,增加了设计的不稳定性。

为了消除人为编写时钟门控逻辑带来的隐患,DC 中需要使用以下命令对手动编写的 CG 进行识别与替换。

replace_clock_gates

此命令实现的优化结果示意图如下:

禁止使用 CG

由于面积、时序等原因,需要禁止使用 lib 中的某一种 CG cell 时,可以使用以下命令:

#禁止使用指定的 CG cell:"lib_cell",

set_dont_use -power {lib_cell}

其中,-power 选项不可或缺,否则 ICG cell 的 dont_use 属性会被忽略。

门控时钟报告

可以使用以下命令,查看时钟门控单元的插入情况,以便确认是否需要对电路进行修改。

report_clock_gating

但是如果 RTL 设计中,存在人为例化的 CG cell,命令 report_clock_gating 是不能识别的,需要设置以下命令:

set power_cg_auto_identify true

-

jf_38241028

2023-09-28

0 回复 举报优秀 收起回复

jf_38241028

2023-09-28

0 回复 举报优秀 收起回复

-

XOR自门控与时钟门控的不同之处2024-01-02 3420

-

什么是时钟门控技术?为什么需要控制时钟的通断呢?2023-06-29 4951

-

门控时钟检查(clock gating check)的理解和设计应用2023-06-19 6467

-

FPGA原型平台门控时钟自动转换2023-05-23 2973

-

什么是时钟门控?如何去实线时钟门控的设计呢2022-12-19 1792

-

什么是门控时钟?如何生成门控时钟?2022-12-05 4013

-

门控时钟实现低功耗的原理2022-07-03 3368

-

什么是门控时钟?2021-11-05 1979

-

什么是门控时钟 门控时钟降低功耗的原理2021-09-23 15903

-

通常有两种不同的时钟门控实现技术2021-06-13 3453

-

门控时钟2016-05-10 847

-

fpga门控时钟问题2012-10-28 3717

-

门控时钟与时钟偏移研究2011-09-07 1217

-

基于门控时钟的CMOS电路低功耗设计2009-11-19 864

全部0条评论

快来发表一下你的评论吧 !