为什么在Verilog HDL设计中一定要用同步而不能用异步时序逻辑?

描述

同步时序逻辑是指表示状态的寄存器组的值只可能在唯一确定的触发条件发生时刻改变。只能由时钟的正跳沿或负跳沿触发的状态机就是一例。always @(posedge clock) 就是一个同步时序逻辑的触发条件, 表示由该 always 控制的 begin end 块中寄存器变量重新赋值的情形只有可能在 clock 正跳沿发生。

而异步时序逻辑是指触发条件由多个控制因素组成,任何一个因素的跳变都可以引起触发。记录状态的寄存器组其时钟输入端不是都连结在同一个时钟信号上。例如用一个触发器的输出连结到另一个触发器的时钟端去触发的就是异步时序逻辑。

用 Verilog HDL 设计的可综合模块,必须避免使用异步时序逻辑,这不但是因为许多综合器不支持异步时序逻辑的综合,而且也因为用异步时序逻辑确实很难来控制由组合逻辑和延迟所产生的冒险和竞争。当电路的复杂度增加时,异步时序逻辑无法调试。工艺的细微变化也会造成异步时序逻辑电路的失效。因为异步时序逻辑中触发条件很随意,任何时刻都有可能发生,所以记录状态的寄存器组的输出在任何时刻都有可能发生变化。而同步时序逻辑中的触发输入至少可以维持一个时钟后才会发生第二次触发。这是一个非常重要的差别,因为我们可以利用这一个时钟的时间在下一次触发信号来到前,为电路状态的改变创造一个稳定可靠的条件。

因此我们可以得出结论:同步时序逻辑比异步时序逻辑具有更可靠更简单的逻辑关系。如果我们强行作出规定,用 Verilog 来设计可综合的状态机必须使用同步时序逻辑,有了这个前提条件,实现自动生成电路结构的综合器就有了可能 。因为这样做大大减少了综合工具的复杂度,为这种工具的成熟创造了条件。也为 Verilog 可综合代码在各种工艺和 FPGA 之间移植创造了条件。

Verilog RTL 级的综合就是基于这个规定的。

下面我们将详细说明同步与异步时序逻辑的差异。

在同步逻辑电路中,触发信号是时钟(clock)的正跳沿(或负跳沿);触发器的输入与输出是经由两个时钟来完成的。第一个时钟的正跳沿(或负跳沿)为输入作准备,在第一个时钟正跳沿(或负跳沿)到来后到第二个时钟正跳沿(或负跳沿)到来之前的这一段时间内,有足够的时间使输入稳定。当第二个时钟正跳沿(或负跳沿)到来时刻,由前一个时钟沿创造的条件已经稳定,所以能够使下一个状态正确地输出。

若在同一时钟的正跳沿(或负跳沿)下对寄存器组既进行输入又进行输出,很有可能由于门的延迟使输入条件还未确定时,就输出了下一个状态,这种情况会导致逻辑的紊乱。而利用上一个时钟为下一个时钟创造触发条件的方式是安全可靠的。但这种工作方式需要有一个前提:确定下一个状态所使用的组合电路的延迟与时钟到各触发器的差值必须小于一个时钟周期的宽度。只有满足这一前提才可以避免逻辑紊乱。在实际电路的实现中,采取了许多有效的措施来确保这一条件的成立,其中主要有以下几点:

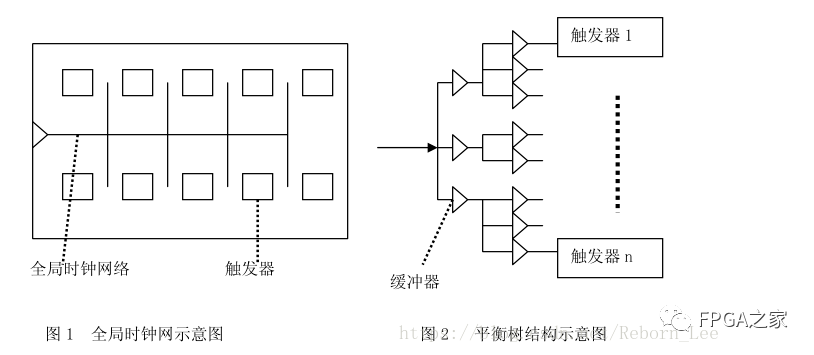

(1)全局时钟网络布线时尽量使各分支的时钟一致;

(2)采用平衡树结构,在每一级加入缓冲器,使到达每个触发器时钟端的时钟同步。(如图 1、2 所示)

通过这些措施基本可以保证时钟的同步,在后仿真时,若逻辑与预期设计的不一样,可降低时钟频率,就有可能消除由于时钟过快引起的触发器输入端由延迟和冒险竞争造成的不稳定从而使逻辑正确。

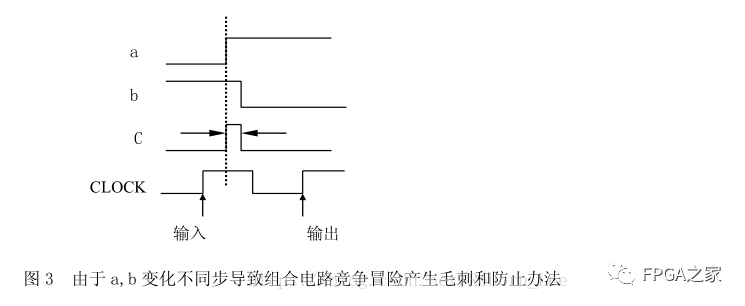

在组合逻辑电路中,多路信号的输入使各信号在同时变化时很容易产生竞争冒险,从而结果难以预料。下面就是一个简单的组合逻辑的例子:C = a & b;

a 和 b 变化不同步使 C 产生了一个脉冲。这个结果也许与当初设计时的想法并不一致,但如果我们能过一段时间,待 C 的值稳定后再来取用组合逻辑的运算结果,就可以避免竞争冒险。同步时序逻辑由于用上一个时钟的跳变沿时刻(置寄存器作为组合逻辑的输入)来为下一个时钟的跳变沿时刻的置数(置下一级寄存器作为该组合逻辑的输出)做准备,只要时钟周期足够长,就可以在下一个时钟的跳变沿时刻得到稳定的置数条件,从而在寄存器组中存入可靠的数据。

而这一点用异步电路是做不到的,因此在实际设计中应尽量避免使用异步时序逻辑。若用弥补的方法来避免竞争冒险,所耗费的人力物力是很巨大的。也无法使所设计的 Verilog HDL代码和已通过仿真测试的电路模块结构有知识产权的可能,因为工艺的细微改变就有可能使电路无法正常工作。显而易见使用异步时序逻辑会带来设计的隐患,无法设计出能严格按同一时间节拍操作控制数据流动方向开关的状态机。而这种能按时钟节拍精确控制数据流动开关的状态机就是同步有限状态机。它是算法计算过程中数据流动控制的核心。计算结构的合理配置和运算效率的提高与算法状态机的设计有着非常密切的关系。我们只有通过阅读有关计算机体系结构的资料和通过大量的设计实践才能熟练地掌握复杂算法系统的设计。

审核编辑:汤梓红

-

Verilog HDL的基础知识2024-10-24 2150

-

什么是同步逻辑和异步逻辑?同步电路与异步电路有何区别?2023-11-17 3835

-

什么是同步逻辑和异步逻辑2021-09-29 2033

-

什么是同步逻辑和异步逻辑?2021-07-26 1497

-

Verilog HDL verilog hdl和vhdl的区别2021-07-23 12318

-

为什么在 Verilog HDL 设计中一定要用同步而不能用异步时序逻辑?2020-03-25 1662

-

Verilog HDL的基础知识详细说明2019-07-03 1759

-

15条FPGA设计经验及同步时序设计注意事项2019-05-04 3383

-

如何使用Verilog-HDL做CPLD设计的时序逻辑电路的实现2018-12-12 2026

-

基本组合逻辑功能双向管脚的Verilog HDL源代码2012-10-15 1862

-

VHDL和Verilog HDL语言对比2010-02-09 10950

-

Verilog HDL程序基本结构与程序入门2010-02-08 2634

-

异步时序逻辑电路2009-09-01 1361

全部0条评论

快来发表一下你的评论吧 !