门延迟类型介绍

描述

门延迟类型

前两节中所介绍的门级电路都是没有延迟的,实际门级电路都是有延迟的。

Verilog 中允许用户使用门延迟,来定义输入到其输出信号的传输延迟。

门延迟类型主要有以下 3 种。

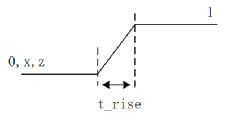

上升延迟

在门的输入发生变化时,门的输出从 0,x,z 变化为 1 所需要的转变时间,称为上升延迟。

下降延迟

在门的输入发生变化时,门的输出从 1,x,z 变化为 0 所需要的转变时间,称为下降延迟。

关断延迟

关断延迟是指门的输出从 0,1,x 变化为高阻态 z 所需要的转变时间。

门输出从 0,1,z 变化到 x 所需要的转变时间并没有被明确的定义,但是它所需要的时间可以由其他延迟类型确定,即为以上 3 种延迟值中最小的那个延迟。

门延迟可以在门单元例化时定义,定义格式如下:

gate_type [delay] [instance_name] (signal_list) ;

其中,delay 的个数可以为 0 个、1 个、2 个或 3个 。

下表为不同延迟个数时,各种类型延迟的取值情况说明。

| 延迟类型 | 无延迟 | 1 个延迟 (d) | 2 个延迟 (d1, d2) | 3 个延迟 (d1, d2, d3) |

|---|---|---|---|---|

| 上升 | 0 | d | D1 | D1 |

| 下降 | 0 | d | D2 | D2 |

| 关断 | 0 | d | 最小(D1, D2) | D3 |

| to_x | 0 | d | 最小(D1, D2) | 最小(D1, D2, D3) |

如果用户没有指定延迟值,则默认延迟为 0 。

如果用户指定了 1 个延迟值,则所有类型的延迟值大小均为此值。

如果用户指定了 2 个延迟值,则他们分别代表上升延迟和下降延迟,关断和“to_x”延迟均为这 2 种延迟值中最小的那个。

如果用户指定了 3 个延迟值,则他们分别代表上升延迟、下降延迟和关断延迟,“to_x”延迟为这 3 种延迟值中最小的那个。

带有延迟值的门级单元例化如下:

//rise, fall and turn-off delay are all 1

and #(1) (OUT1, IN1, IN2) ;

//rise delay = 2.1, fall dalay = 2, trun-off delay = 2

or #(2.1, 2) (OUT2, IN1, IN2) ;

//rise delay = 2, fall dalay = 1, trun-off delay = 1.3

bufif0 #(2, 1, 1.3) (OUT3, IN1, CTRL) ;

需要说明的是,多输入门(如与门)和多输出门(如非门)最多只能定义 2 个延迟,因为输出不会是 z 。

三态门和单向开关单路(MOS 管、CMOS 管等)可以定义 3 个延迟。

上下拉门级电路不会有任何的延迟,因为它表示的是一种硬件属性,上下拉状态不会发生变化,且没有输出值。

双向开关(tran)在传输信号时没有延迟,不允许添加延迟定义。

带有控制端的双向开关(tranif1, tranif0)在开关切换的时候,会有开或关的延迟,可以给此类双向开关指定 0 个、1 个或 2 个的延迟,例如:

//turn-on and turn-off delay are all 1

tranif0 #(1) (inout1, inout2, CTRL);

//turn-on delay = 1, turn-off delay = 1.2

tranif1 #(1, 1.2) (inout3, inout4, CTRL);

最小/典型/最大延迟

由于集成电路制造工艺的差异,实际电路中器件的延迟总会在一定范围内波动。 Verilog 中,用户不仅可以指定 3 种类型的门延迟,还可以对每种类型的门延迟指定其最小值、典型值和最大值。 在编译或仿真阶段,来选择使用哪一种延迟值,为更切实际的仿真提供了支持。

最小值:门单元所具有的最小延迟。

典型值:门单元所具有的典型延迟。

最大值:门单元所具有的最大延迟。

下面通过例化实例,来说明最小、典型、最大延迟的用法。

//所有的延迟类型:最小延迟 1, 典型延迟 2, 最大延迟 3

and #(1:2:3) (OUT1, IN1, IN2) ;

//上升延迟:最小延迟 1, 典型延迟 2, 最大延迟 3

//下降延迟:最小延迟 3, 典型延迟 4, 最大延迟 5

//关断延迟:最小延迟 min(1,3), 典型延迟 min(2,4), 最大延迟 min(3,5)

or #(1:2:3, 3:4:5) (OUT2, IN1, IN2) ;

//上升延迟:最小延迟 1, 典型延迟 2, 最大延迟 3

//下降延迟:最小延迟 3, 典型延迟 4, 最大延迟 5

//关断延迟:最小延迟 2, 典型延迟 3, 最大延迟 4

bufif0 #(1:2:3, 3:4:5, 2:3:4) (OUT3, IN1, CTRL) ;

D 触发器

下面从门级建模的角度,对 D 触发器进行设计。

SR 触发器

SR 触发器结构图及真值表如下所示。

1> 当 S 为低电平,G1 输出端 Q 为高电平,并反馈到 G2 输入端。 如果此时 R 为高电平,则 G2 输出端 Q' 为低电平。

2> R 为低电平 S 为高电平时,分析同理。

3> S 与 R 均为高电平时,如果 Q = 1 (Q' = 0) , 则 Q 反馈到 G2 输入端后输出 Q' 仍然为 0, Q' 反馈到 G1 输入端后输出 Q 仍然是 1,呈现稳态。 如果 Q =0 (Q' = 1) 同理,Q 与 Q' 的值仍然会保持不变。 即 S 与 R 均为高电平时该电路具有保持的功能。

4> 如果 S 与 R 均为低电平,则输出 Q 与 Q' 均为高电平,不再成互补的关系。 所以此种情况是禁止出现的。

SR 锁存器

在基本的 SR 触发器前面增加 2 个与非门,可构成带有控制端 SR 锁存器。

SR 锁存器及其真值表如下所示。

当 EN=0 时,G3、G4 截止,SR 锁存器保持输出状态不变。

当 EN=1 时,与基本的 SR 触发器工作原理完全相同。

D 锁存器

基本的 SR 触发器输入端不能同时为 0, 带有控制端的 SR 锁存器输入端不能同时为 1,否则会导致输出端 Q 与 Q' 的非互补性矛盾。

为消除此种不允许的状态,在带有控制端的 SR 锁存器结构中加入取反模块,保证 2 个输入端均为相反逻辑,则形成了 D 锁存器。

其结构图和真值表如下所示。

1> 当 EN=1 时,输出状态随输入状态的改变而改变。

2> 当 EN=0 时,输出状态保持不变。

D 锁存器是一种电平触发。

如果在 EN=1 的有效时间内,D 端信号发生多次翻转,则输出端 Q 也会发生多次翻转。 这降低了电路的抗干扰能力,不是实际所需求的安全电路。

为提高触发器的可靠性,增强电路抗干扰能力,发明了在特定时刻锁存信号的 D 触发器。

D 触发器

将两个 D 锁存器进行级联,时钟取反,便构成了一种简单的 D 触发器,又名 Flip-flop。

其结构图和真值表如下所示。

第一级 D 锁存器又称为主锁存器,在 CP 为低电平时锁存。 第二级 D 锁存器又称为从锁存器,时钟较主锁存器相反,在 CP 为高电平时锁存。

1> CP=1 时,主锁存器输出端 Qm 会和 D 端信号的变化保持一致,而从锁存器处于保持状态,输出 Qs 保持不变。

2> CP由高电平变为低电平时,主锁存器锁存当前 D 的状态,传递到输出端 Qm 并保持不变。 而从锁存器输出端 Qs 会和 Qm 的变化保持一致。 此时处于锁存状态下的主锁存器输出端 Qm 会保持不变,所以 D 触发器输出端 Qs 端得到新的 Qm 值后, 也会保持不变。

综上所述,D 触发器输出端 Qs 只会在时钟 CP 下降沿对 D 端进行信号的锁存,其余时间输出端信号具有保持的功能。

将双级 D 锁存器展开为门级结构,如下图所示。

对 D 触发进行门级建模,并加入门级延时,verilog 模型如下:

module D_TRI(

input D, CP,

output Q, QR);

parameter RISE_TIME = 0.11 ;

parameter FALL_TIME = 0.07 ;

//part1, not gate

wire CPN, DN ;

not #(RISE_TIME, FALL_TIME) (CPN, CP);

not #(RISE_TIME, FALL_TIME) (DN, D);

//part2, master trigger

wire G3O, G4O ;

nand #(RISE_TIME, FALL_TIME) (G3O, D, CP);

nand #(RISE_TIME, FALL_TIME) (G4O, DN, CP);

wire #(RISE_TIME, FALL_TIME) G1O, G2O ;

nand #(RISE_TIME, FALL_TIME) (G1O, G3O, G2O);

nand #(RISE_TIME, FALL_TIME) (G2O, G4O, G1O);

//part3, slave trigger

wire G7O, G8O ;

nand #(RISE_TIME, FALL_TIME) (G7O, G1O, CPN);

nand #(RISE_TIME, FALL_TIME) (G8O, G2O, CPN);

wire G5O, G6O ;

nand #(RISE_TIME, FALL_TIME) (G5O, G7O, G6O);

nand #(RISE_TIME, FALL_TIME) (G6O, G8O, G5O);

assign Q = G5O ;

assign QR = G6O ;

endmodule

testbench 编写如下:

`timescale 1ns/1ps

module test ;

reg D, CP = 0 ;

wire Q, QR ;

always #5 CP = ~CP ;

initial begin

D = 0 ;

#12 D = 1 ;

#10 D = 0 ;

#14 D = 1 ;

#3 D = 0 ;

#18 D = 0 ;

end

D_TRI u_d_trigger(

.D (D),

.CP (CP),

.Q (Q),

.QR (QR));

initial begin

forever begin

#100;

//$display("---gyc---%d", $time);

if ($time >= 1000) begin

$finish ;

end

end

end

endmodule

仿真结果如下。

由图可知,Q/QR 信号均在时钟 CP 下降沿采集到了 D 端信号,并在单周期内保持不变,且输出有延迟。

对 cap3 时刻进行放大,对延时进行追踪,如下图所示。

CP 端到 CPN 端有上升延迟,时间为 110ps;

CPN 端到 G8O 端有下降延迟,时间为 70ps;

G8O 端到 G6O 端有上升延迟,时间为 110ps;

G6O 端到 Q 端有下降延迟,时间为 70ps;

共 360ps,符合设置的门延迟。

-

如何有效评估SAN网络延迟(latency)?2013-01-07 2159

-

PlanAhead报告时间:路径延迟类型代表什么?2019-02-25 2314

-

智能锁厂家诺托告诉你不同类型的门如何搭配智能锁2019-01-11 4926

-

Xilinx Vivado I/O延迟约束介绍2020-11-29 6569

-

Verilog HDL提供了哪两种类型的显式时序控制2021-07-02 2536

-

MOSFET门级电路的深入介绍2022-10-24 674

-

SystemVerilog/Verilog中的各种延迟模型2023-04-09 7720

-

基本逻辑门的类型及其用途2023-07-04 8840

-

python变量与基本数据类型介绍2023-07-05 1581

-

磁通门高精度电流传感器介绍及应用2022-08-11 1595

-

孔径时间、孔径抖动、孔径延迟时间介绍2023-11-27 827

-

电阻的封装类型介绍2023-12-29 5948

全部0条评论

快来发表一下你的评论吧 !