ASIC和FPGA的RTL编码样式

电子说

描述

SystemVerilog的RTL综合子集

SystemVerilog既是一种硬件设计语言,也是一种硬件验证语言。IEEE SystemVerilog官方标准没有区分这两个目标,也没有指定完整SystemVerilog语言的可综合子集。相反,IEEE让提供RTL综合编译器的公司来定义特定产品支持哪些SystemVerilog语言结构。

由于缺乏SystemVerilog综合标准,每个综合编译器可能支持SystemVerilog标准的不同子集。这意味着设计工程师在编写用于综合的SV模型时需要小心。必须参考要使用的综合编译器的文档,并遵循为一个综合编译器编写的编译器模型的语言子集,使用不同的综合编译器可能需要根据综合器特性进行修改。

接下来看下今天的主角-FPGA建模概念

FPGA的建模

本文的目的是了解SystemVerilog建模风格如何受到ASIC和FPGA技术的影响。有关ASIC和FPGA实现的详细信息以及这些技术的适当应用留给其他工程书籍讨论。然而,为了实现RTL建模最佳实践的目标,理解ASIC和FPGA的基本概念非常重要。

标准单元ASIC

ASIC是专用集成电路的缩写。与可执行多种功能(如微处理器)的通用IC不同,ASIC设计用于执行特定任务(因此得名为“application specific”)。控制器、音频格式转换和视频处理是适用于ASIC的示例。ASIC还可以包括一个或多个嵌入式处理器,以便执行特定任务同时可以进行通用操作。带有嵌入式处理器的ASIC通常被称为片上系统(SoC,主流设计)。

提供ASIC的公司称为ASIC供应商(ASIC vendors)。其中一些供应商提供ASIC技术并进行ICs实际制造和生产的一部分。其他ASIC供应商为ASIC提供技术,但将制造和生产留给其他公司。

大多数ASIC技术使用标准单元(standard cells),这些单元是预先设计的逻辑块,由一到几个逻辑门组成。ASIC单元库可能有几百个标准单元,如AND、NAND、OR、NOR、Exclusive-OR, Exclusive-NOR,2-to-l MUX- 2选1 MUX、D型触发器、锁存器等。每个单元都有明确的电气特性,如传播延迟、建立和保持时间以及寄生电容。

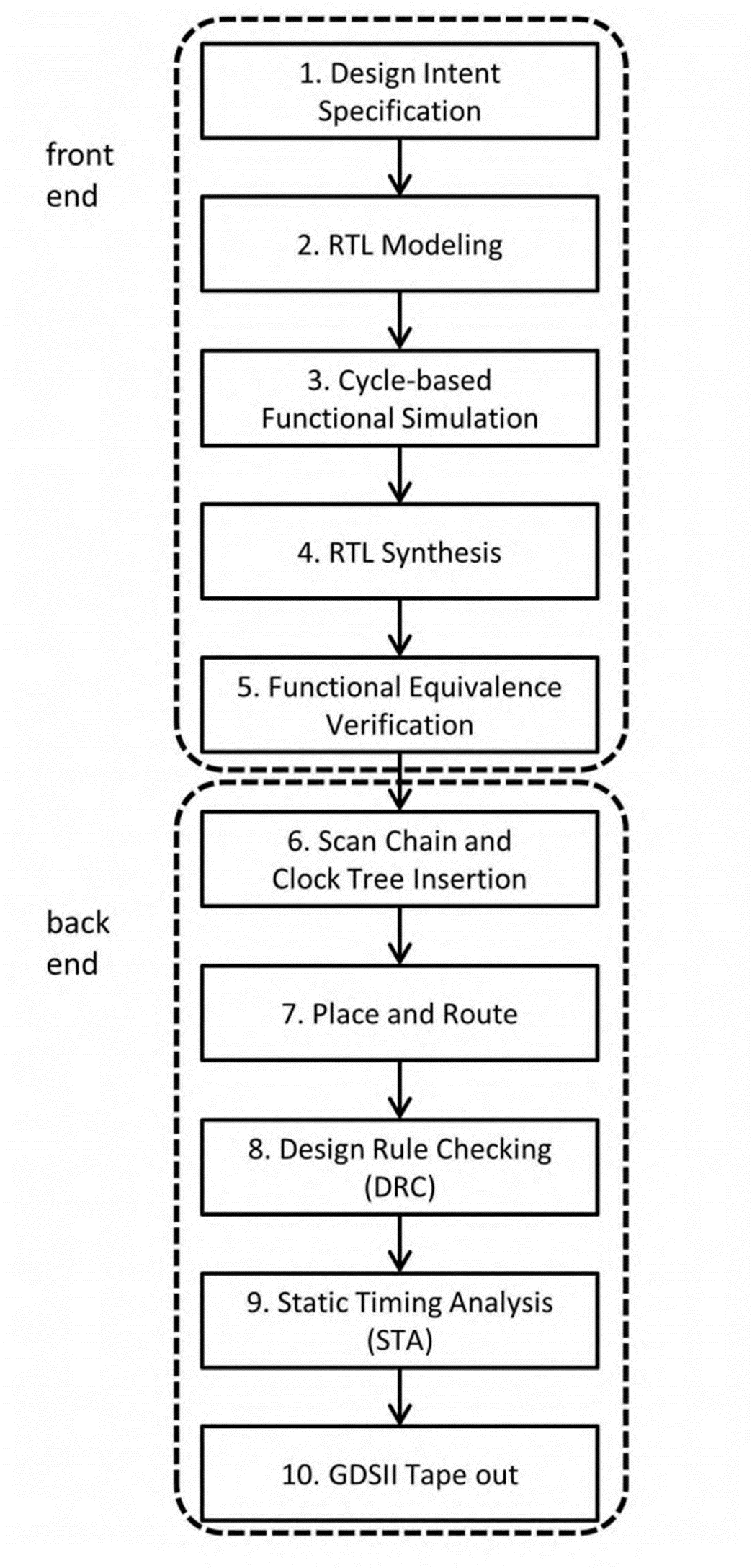

设计ASIC涉及从库中选择合适的单元,并将它们连接在一起以执行所需的功能。在整个过程中使用EDA软件工具进行设计。ASIC设计的典型流程如图1-5所示:

图1-5:典型的基于RTL的ASIC设计流程图1-5所示的步骤是:

- 1、当然,第一步是说明设计的意图。

- 2、所需的功能在抽象的RTL建模级别进行建模。在这个阶段,重点是功能,而不是物理实现。

- 3、仿真并验证功能。

- 4、综合,将RTL功能映射到适合目标ASIC类型的标准单元。综合的输出称为门级网表(gate-level netlist),该综合过程在后面有更详细的描述。

- 5、仿真或逻辑等价检查器(Logic Equivalence Checkers)(形式验证的一种形式)用于验证门级实现在功能上等同于RTL功能。

- 6、时钟树合成用于在整个设计中均匀分布时钟驱动。通常,扫描链插入到工具中以增加设计的可测试性。

- 7、Place and route(放置和布线)软件计算如何在实际硅中布局,以及如何布线。place and route软件的输出是一个图形数据系统文件(GDSII,发音为gee dee ess two)。GDSII是一种二进制格式,其中包含有关实际在硅中构建IC所需的几何形状(多边形polygons)和其他数据的信息。

- 8、进行设计规则检查(DRC),以确保ASIC制造厂定义的所有规则均得到遵守,如加载门扇出,

- 9、在考虑互连网络和时钟树倾斜的延迟效应后,执行静态时序分析(STA)以确保满足建立/保持时间。

- 10、最后一步是将GDSII文件和其他数据发送给制造厂,用于制造ASIC。将这些文件传递给制造厂被称为“taping out”ASIC,因为在ASIC设计的早期,是使用磁带将这些文件发送给铸造厂:

在本文中,ASIC设计流程中的这些步骤已被概括。有许多细节被遗漏了,并不是所有的公司都遵循这个确切的流程。有时,步骤9(静态时序分析)在设计流程的早期执行,并且可能在流程中执行多次。

本文的重点是用于仿真和合成的RTL建模,图1-5中的步骤2和步骤3。此级别的建模处于设计过程的前端。时钟树、扫描链和时序分析等设计细节将在设计流程的后面介绍,不在本文的范围之内。在RTL级别,设计工程师专注于实现所需的功能;而不是实施细节。然而,理解在建模、仿真和合成的前端步骤之后会发生什么仍然很重要。RTL编码风格会影响设计流程中后期使用的工具的有效性。

还有其他类型的ASIC技术不使用标准单元,如全定制、门阵列和结构化ASIC。SystemVerilog可以以类似的方式用于设计这些其他类型的ASIC,尽管所涉及的软件工具可能有所不同。所使用的综合编译器——以及这些编译器支持的SystemVerilog语言结构——可能与这些其他技术非常不同。

FPGA

FPGA是现场可编程门阵列(Field Programmable Gate Array)的缩写。FPGA是一种集成电路,包含固定数量的逻辑块,可在IC制造后进行重新配置(而ASIC的内容和布局必须在制造前确定)。从历史上看,FPGA不能包含ASIC那么多的功能,只能以较慢的时钟速度运行,这是RTL级设计时的重要考虑因素。FPGA技术的最新进展显著缩小了FPGA和ASIC之间的差异。通常,FPGA可用于实现与ASIC相同的功能。

FPGA包含一系列称为可配置逻辑块(CLB)的小型逻辑元件。一些FPGA供应商将这些块称为逻辑阵列块(LABs)。典型的CLB可能包含一个或多个查找表(LUT)、一些多路复用器(MUX)和存储元件(如D型触发器)。大多数FPGA中的查找表都是用逻辑运算(如AND、OR和XOR)编程的小型RAM。从LUT中选择所需的操作允许以多种方式使用CLB,从简单的AND或XOR门到更复杂的组合功能。某些FPGA中的CLB还可能具有其他功能,例如加法器。MUX允许组合结果直接从CLB输出(异步输出),或在存储单元中输出(同步输出)。

FPGA使用包含数百或数千个CLB的阵列进行制造,以及可“编程”到所需CLB配置的可配置互连-FPGA还包含I/O焊盘,可配置为连接到CLB阵列的一列或一行。

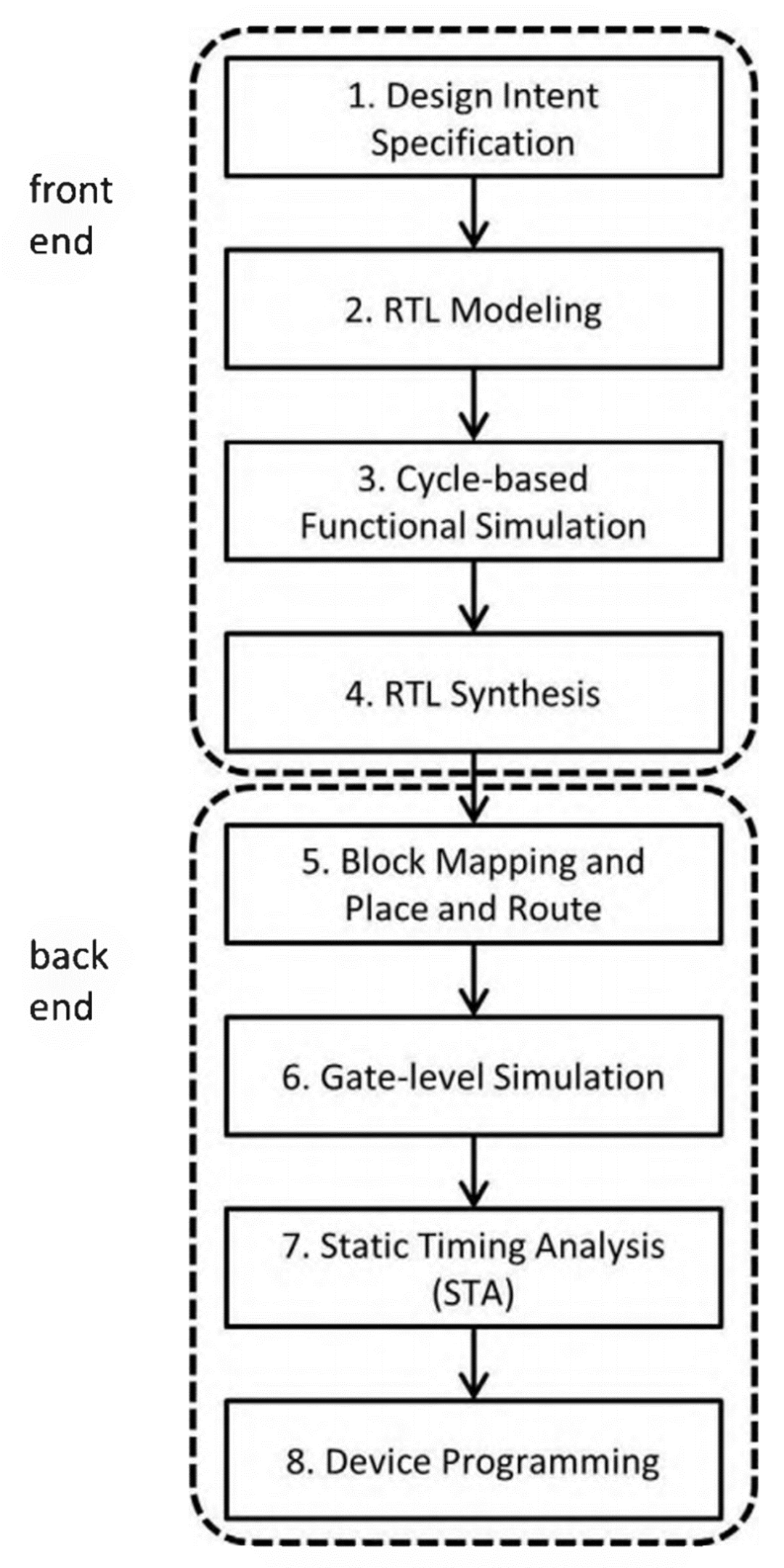

复杂FPGA的典型设计流程如图1-6所示。

图1-6:典型的基于RTL的FPGA设计FPGA的前端设计流程类似于ASIC,但后端不同。FPGA的后端部分与ASIC的主要区别在于FPGA的布局和布线。对于ASIC,place and route软件决定IC的制造方式。对于FPGA,综合和布局布线软件详细说明了如何对FPGA进行编程。本文重点介绍前端步骤2和3,RTL建模和仿真,其中ASIC和FPGA设计之间几乎没有区别。

ASIC和FPGA的RTL编码样式

理想情况下,相同的RTL代码可以同时用于ASIC或FPGA。在“RTL级别”工作时,工程重点是设计和验证功能,而不必关心实施细节。综合编译器的作用是将RTL功能映射到特定的ASIC或FPGA技术。

对于ASIC和FPGA来说,大多数(但不是全部)RTL代码都能很好地综合。然而,这种普遍性也有例外。RTL模型的一些方面需要考虑设计是在ASIC还是FPGA中进行综合,这些方面包括:

- 复位。大多数ASIC单元库包括同步和异步复位触发器。设计工程师可以使用被认为最适合设计的复位类型来编写RTL模型,一些FPGA没有那么灵活,只有一种复位类型的触发器(通常是同步的)。虽然综合编译器可以将带有异步复位的RTL模型映射到门级同步复位中,或者反之亦然,但需要额外的逻辑门。许多FPGA还支持ASIC不具备的全局复位功能和预置上电上电触发器的状态。后面会更详细地讨论复位建模。

- 向量/矢量大小。ASIC在最大矢量宽度和矢量运算方面基本不受限制。在大向量上进行复杂操作需要大量逻辑门,但大多数ASIC中使用的标准单元架构可以适应这些操作。FPGA在这方面比较严格。由于可用CLB的数量或CLB之间互连路由的复杂性,预定义的CLB数量及其在FPGA中的位置可能会限制在非常大的向量上实现复杂操作的能力。ASIC和FPGA之间的这种差异意味着,即使在RTL抽象级别,设计工程师也必须牢记设计的功能会受到设备的限制。

-

RTL级机器人电机控制器的FPGA设计2025-07-07 3087

-

到底什么是ASIC和FPGA?2024-01-23 1691

-

SRRC证书样式和代码编码规则即将施行2023-10-14 1658

-

FPGA和ASIC的区别与联系2023-08-14 4804

-

什么是FPGA原型验证?如何用FPGA对ASIC进行原型验证2023-04-10 2870

-

FPGA、ASIC技术对比2023-03-31 2832

-

从FPGA到ASIC,异曲同工还是南辕北辙?2023-03-28 1964

-

H.265/HEVC超低延迟编码/解码FPGA/ASIC IP2023-02-24 2249

-

FPGA vs ASIC2022-11-28 2851

-

典型的基于RTL的ASIC设计流程分析2022-06-20 6736

-

怎么利用Synphony HLS为ASIC和FPGA架构生成最优化RTL代码?2019-08-13 2660

-

探析FPGA和ASIC的原理和区别2018-12-15 6464

-

cogoask讲解fpga和ASIC是什么意思2012-02-27 2538

-

ASIC和FPGA的优势与劣势2011-03-31 6061

全部0条评论

快来发表一下你的评论吧 !