沟槽结构SiC MOSFET常见的类型

描述

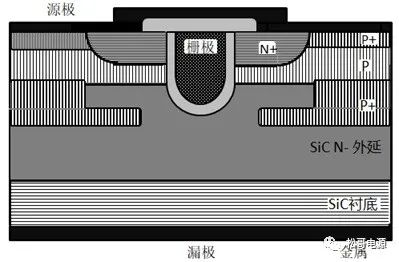

SiC MOSFET沟槽结构将栅极埋入基体中形成垂直沟道,尽管其工艺复杂,单元一致性比平面结构差。但是,沟槽结构可以增加单元密度,没有JFET效应,寄生电容更小,开关速度快,开关损耗非常低;而且,通过选取合适沟道晶面以及优化设计的结构,可以实现最佳的沟道迁移率,明显降低导通电阻,因此,新一代SiC MOSFET主要研究和采用这种结构。

这种结构栅极沟槽底部氧化层的工作电场强度高,在高的反向偏置电压下,此处成为器件最薄弱的环节。沟槽结构SiC MOSFET的技术演进方向,就是采用优化的内部结构,减小沟槽底部氧化层工作电场强度,本文列出了一些常见结构。

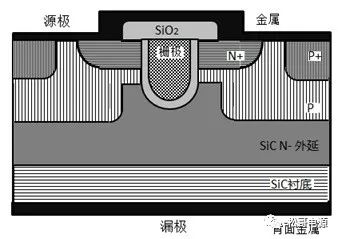

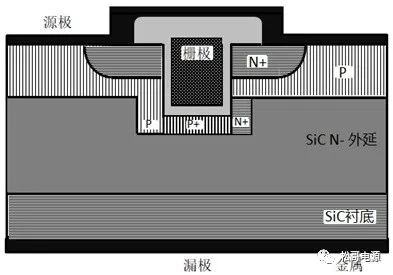

1、Rohm的双沟槽结构

栅极沟槽底部氧化层外二侧P-体区下移,下移P-体区和沟槽底部附近的N-区漂移层的PN结,形成耗尽层,也就是空间电荷区,降低栅极沟槽底部氧化层内的工作电场强度,这是一种最为经典、实用的专利结构。

a) Rohm双沟槽结构

b) 电场分布

图1 Rohm双沟槽结构及电场分布

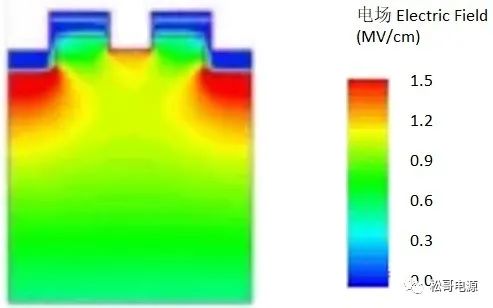

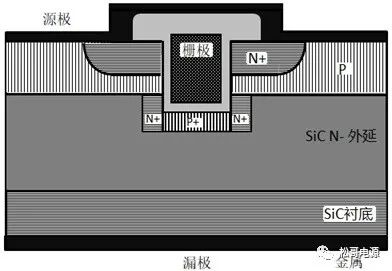

2、Infineon非对称沟槽结构

栅极沟槽底部氧化层外P-体区单侧下移,半包裹栅极沟槽底部区域,下移P-体区和沟槽底部附近N-区漂移层的PN结,形成耗尽层、也就是空间电荷区,降低栅极沟槽底部氧化层内的工作电场强度。

图2 Infineon非对称沟槽结构

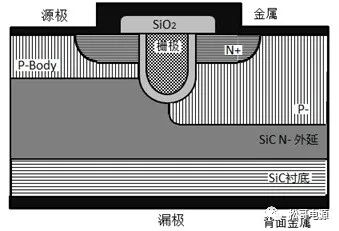

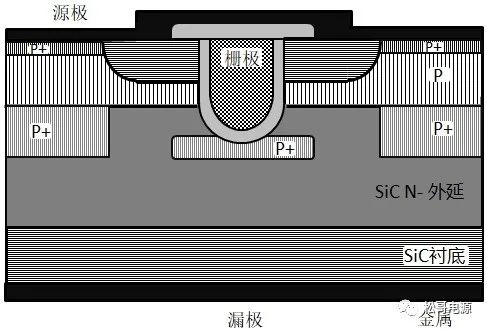

3、普渡大学Integral Oxide Protection综合氧化保护结构

综合氧化保护结构IOP改进地方有3部分:整个栅极沟槽氧化层外,包括底部和侧壁,使用低掺杂薄层N-型SiC,把栅极氧化层隔开;栅极沟槽下部,再增加一层P+型SiC;P-体区和N-漂移层之间增加一层高掺杂N+型SiC。

图3 普渡大学IOP沟槽结构

器件处于反向偏置时,栅极沟槽下面新增PN结形成空间电荷区,也就是耗尽层,可以对栅极氧化层起到屏蔽电场作用,将栅极氧化层内最大电场转移到PN结,减小栅极氧化层内的工作电场,甚至让栅极氧化层电场减少到0,有效消除栅极氧化层被电场击穿可能性。

栅极沟槽侧壁薄层低掺杂N-型SiC,可以降低SiC-SiO 界面态对沟道电子散射作用,提高电子迁移率,降低器件导通电阻。器件导通时,P-体区和N-漂移层之间新增高掺杂N+型层,促进沟道电子进入漂移区后立即扩展,进一步降低导通电阻。

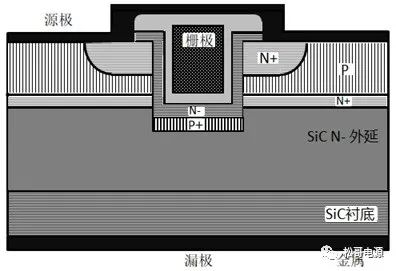

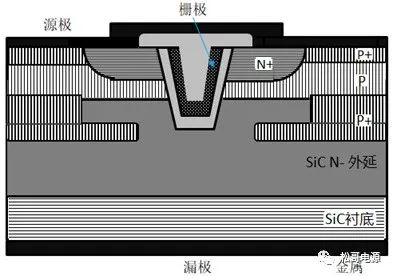

4、Mitsubishi沟槽结构

采用非对称沟槽结构,栅极沟槽底部区域有3个结构:底部P+电场限制结构,侧接地电场限制层(图4中沟槽底部左侧P区)、高浓度N+掺杂导电区(图4中沟槽底部右侧N+区)。栅极沟槽底部的P+电场限制结构和N-漂移层形成PN结,PN结的耗尽层、也就是空间电荷区,将加在栅极氧化层的电场强度降低到普通平面结构的水平,侧接地电场限制层将电场限制层连接到源极,形成侧接地,实现高速开关。高浓度掺杂导电区,降低电流通路的导通电阻。

图4 Mitsubishi沟槽结构

其改进结构如图5所示,沟槽底部区域变为2个结构:沟槽底部的P+电场限制结构和沟槽底部周围的高浓度掺杂N+导电区(图5中沟槽底部二侧N+)。P+电场限制结构将加在栅极沟槽氧化层的电场强度降低,高浓度掺杂N+导电区降低电流通路的导通电阻。

图5 Mitsubishi改进沟槽结构

5、Fuji Electric

栅极沟槽二侧的P-体区部分下移,使用高掺杂P+;栅极沟槽底部氧化层外,增加掩埋的P+浮岛结构,和N-漂移层形成PN结,PN结的耗尽层、也就是空间电荷区,降低栅极沟槽底部氧化层内的工作电场强度。

图6 Fuji沟槽结构

6、日本住友/丰田

栅极沟槽二侧P-体区部分下移,使用高掺杂P+,在沟槽底部氧化层外附近区域,下移P+区截面积变宽,延伸到栅极沟槽底部氧化层外附近区域,让下移的P+区和栅极沟槽底部附近的N-漂移层形成PN结,PN结的耗尽层,降低栅极沟槽底部氧化层内的电场强度,沟槽采用V形结构。

图7 日本住友/丰田沟槽结构

7、日本Denso电装

类似于住友的沟槽结构,只是改为U形沟槽。

图8 日本Denso沟槽结构

总结:这些结构核心就是在栅极沟槽底部或栅极沟槽底部附近区域,增加P型结构,形成耗尽层(空间电荷区),从而,把栅极沟槽底部氧化层电场,部分转移到耗尽层中,减小栅极沟槽底部的电场。

审核编辑:刘清

-

沟槽型SiC MOSFET的结构和应用2025-02-02 2664

-

新型沟槽SiC基MOSFET器件研究2023-12-27 2792

-

SiC MOSFET学习笔记:各家SiC厂商的MOSFET结构2023-06-07 21324

-

SiC MOSFET:是平面栅还是沟槽栅?2023-04-27 10000

-

SiC MOSFET的结构及特性2023-02-16 5869

-

SiC-MOSFET和功率晶体管的结构与特征比较2023-02-08 1411

-

SiC-MOSFET器件结构和特征2023-02-07 1574

-

浅析SiC-MOSFET2019-09-17 6420

-

沟槽结构SiC-MOSFET与实际产品2018-12-05 4847

-

SiC-MOSFET功率晶体管的结构与特征比较2018-11-30 5549

-

SiC-MOSFET的应用实例2018-11-27 6069

-

世界首家!ROHM开始量产采用沟槽结构的SiC-MOSFET2015-06-25 2755

全部0条评论

快来发表一下你的评论吧 !