多晶硅蚀刻工艺讲解

描述

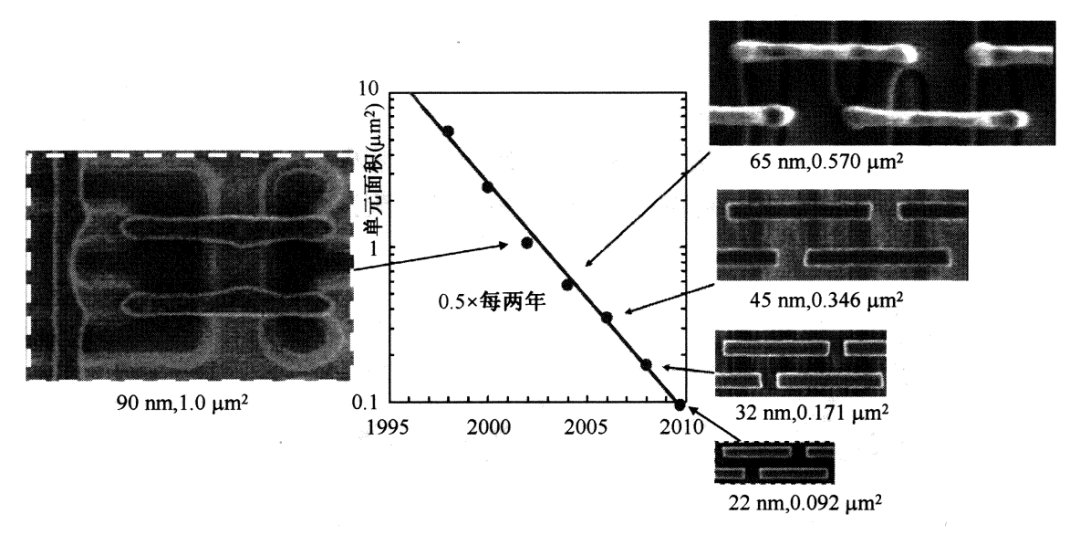

下图显示了Intel的第6代晶体管(6T)SRAM尺寸缩小时间表,以及多晶硅栅刻蚀技术后从90nm到22nm技术节点6TSRAM单元的SEM图像俯视视图。可以看出,SRAM的布局从65nm节点已发生了革命性的变化,这种布局完全不同于90nm节点。从45nm节点后,双重图形化技术已经应用在栅图形化工艺中。随着技术节点的继续缩小,MOSFET栅极关键尺寸CD继续缩小遇到了困难,IC设计人员开始减少栅极之间的间距。

多晶硅栅MOSFET需要多晶硅刻蚀形成栅极图形。具有高k和金属栅极(HKMG)MOSFET需要刻蚀多晶硅。事实上,采用45nm、32nm和22nm技术节点的IntelSRAM多晶硅栅在ILDOCMP后被刻蚀(见下图),并且被金属层取代形成金属栅极。因为栅极之间的间距对32nm和22nmSRAM很小,具有刻蚀工艺的沟槽式接触与DRAM的自对准接触(SAC)类似,并且已经被开发应用于形成接触栓塞。

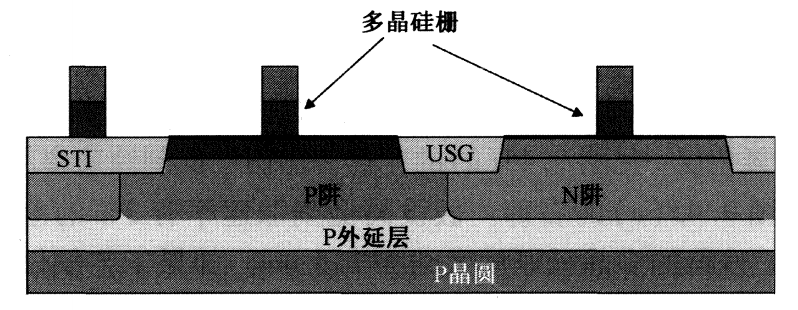

图9.44显示了一个多晶硅蚀刻工艺用于形成CMOS栅和局部互连。可以看出,它使用栅氧化层和STI氧化物上的光刻胶作为刻蚀掩膜和刻蚀停止层。

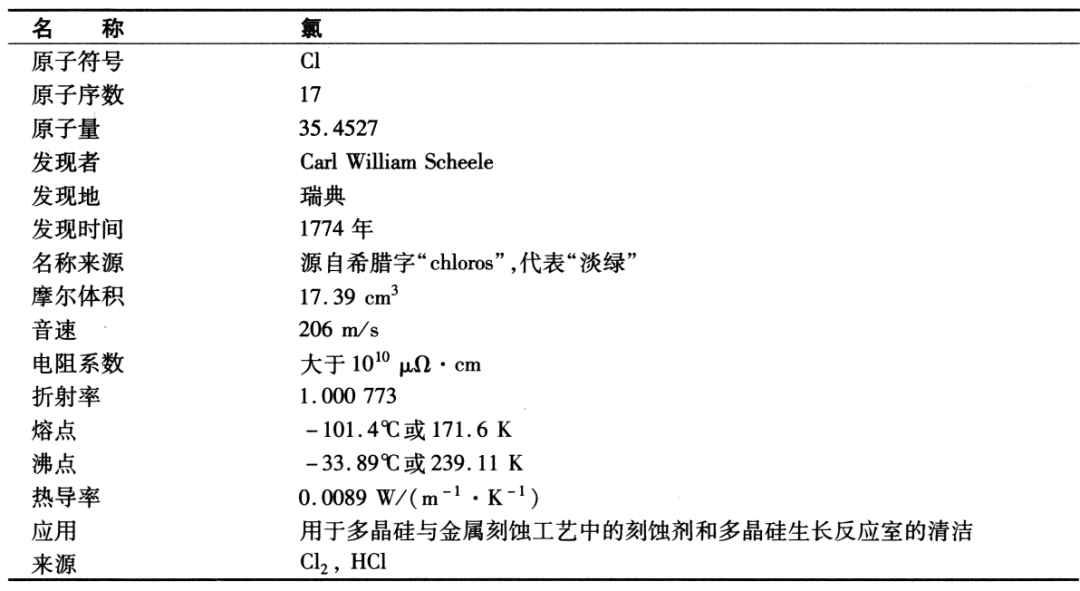

Cl2是多晶硅刻蚀的主要刻蚀剂。等离子体中,Cl2分子分解产生容易反应的氯元素自由基,氯自由基能与硅形成气态四氯化硅。下表列出了部分氯元素的相关参数。

Cl2很容易和光刻胶材料结合并在侧壁上沉积一层聚合物薄膜,从而有助于形成非等向性的刻蚀轮廓和较小的关键尺寸损失(或增加)。HBr也可作为第二种刻蚀剂及侧壁钝化作用的催化剂。能用来改善对氧化物的选择性。

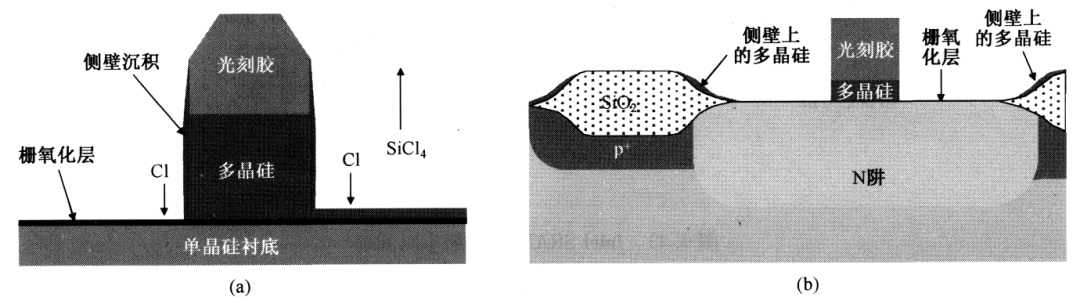

多晶硅栅刻蚀最大的挑战之一是对二氧化硅的高选择性,因为多晶硅下方是一个超薄的栅氧化层。对于45nm器件,栅氧化层的厚度大约只有12A,相当于两层二氧化硅分子的厚度。由于刻蚀速率和多晶硅薄膜厚度不均匀,所以部分的多晶硅可能已被刻蚀而其他部分仍在进行刻蚀(见下图)。由于不能刻蚀掉薄的栅氧化层薄膜,况且刻蚀多晶硅的刻蚀剂也将刻蚀掉栅氧化层下的单晶硅而形成缺陷,所以在多晶硅过刻蚀中,对氧化物的选择性一定要足够高。

下图显示了多晶硅过刻蚀的要求。如果刻蚀工艺在高的刻蚀率下进行,晶圆的一部分就已经被刻蚀到了栅氧化层,见下图(a)的左部。然而在低刻蚀速率部分,仍有薄的多晶硅残留需要刻蚀掉,见下图(a)的右部。假设高低刻蚀速率有3%的差异,对于均匀厚度为50nm的多晶硅薄膜,残留的多晶硅厚度大约为1.5nm。如果工艺仅仅允许约0.5A的栅氧化层损失,过刻蚀的选择性必须高于30:1。对于下图(b)所示的LOCOS情况,当器件工作区的多晶硅被刻蚀的同时,场氧化层侧壁上残留的多晶硅仍然需要刻蚀。这个选择性取决于侧壁残留物的厚度与可容许的栅氧化层损失比例。如果侧壁残留物厚度为1500A,而最大栅氧化层损失为30A,则在过刻蚀中多晶硅对二氧化硅的选择性至少为1500:30=50:1。

审核编辑:汤梓红

-

多晶硅蚀刻残留物的的形成机理2022-05-06 1909

-

温度对KOH溶液中多晶硅电化学纹理化的影响2022-01-13 1325

-

多晶硅是什么东西_多晶硅属于什么行业2021-02-24 18937

-

FZ多晶硅24吨2020-01-20 1252

-

低温多晶硅的工作原理是什么?2019-09-18 3161

-

多晶硅生产工艺流程2019-04-11 89014

-

多晶硅上市公司有哪些_国内多晶硅上市公司排名2017-12-18 67136

-

低温多晶硅,低温多晶硅是什么意思2010-03-27 1035

-

我国光伏多晶硅生产工艺有了革命性进步2009-11-25 1108

-

多晶硅提纯技术2009-11-20 2422

-

什么是多晶硅2009-04-08 2867

-

多晶硅生产工艺流程图2009-03-30 12185

-

单晶硅与多晶硅的区别2009-03-04 4889

全部0条评论

快来发表一下你的评论吧 !