IR Drop对芯片性能及功能的影响

电子说

描述

1.前言

之前做过一个项目,有个模块例化了10次,流片回来测试,有9个正常工作,另外一个工作不起来。这时这个模块的负责人就来找我,问到:IR仿真时这10个模块结果是怎样的?测试有问题那个是IR最差的那个吗?后来把仿真结果拿出来,发现工作不起来这个模块IR不是最差的,结果和我就没关系了。不过后来这个模块又可以工作了(具体原因不知道)。

另一个项目(不是我参与的),工艺不同,还是这个模块,不过只例化只有一次,但是流片回来测试,这个模块在func模式下可以正常工作,在scan模式下工作不起来,项目组怀疑是IR问题。结果后端负责人整天到处出差开会(和foundary厂、项目经理、DFT负责人等等),虽然已经做了很多工作,但是目前还没有定论。

从以上项目情况可知,芯片流片回来后,测试有问题,如果定位不到原因,首先会怀疑IR问题导致的,做IR分析的人就很无辜了,因为IR的实际情况无法测量(据某司后端负责人讲,他们已经可以测出来)。

为啥测试有问题首先会怀疑IR结果?随着半导体工艺的演进,金属线越做越窄(电阻越来越大)、电压越来越低(噪声容限越来越小)、电路频率越来越高(cell 翻转率越来越高)等一些列因素对IR都不太友好,也导致在先进工艺IR分析越来越重要。加之IR没法实测,导致有问题不好定位,所以大家也称IR分析为“玄学”。

最初想写这篇文章是在做上一个项目的时候。由于项目中有一些加速器设计(累加累乘功能),导致这些模块在die+封装仿真时,模块局部IR Drop特别大。当时在冲刺signoff节点,项目经理和开发的人就问这个IR Drop不满足标准到底有啥影响?可以waive不?哈哈,我就想说你不想让流片回来芯片测试时正常工作你就waive吧。不过言归正传,IR Drop对芯片性能(timing)到底有什么影响?

2.IR Drop定义

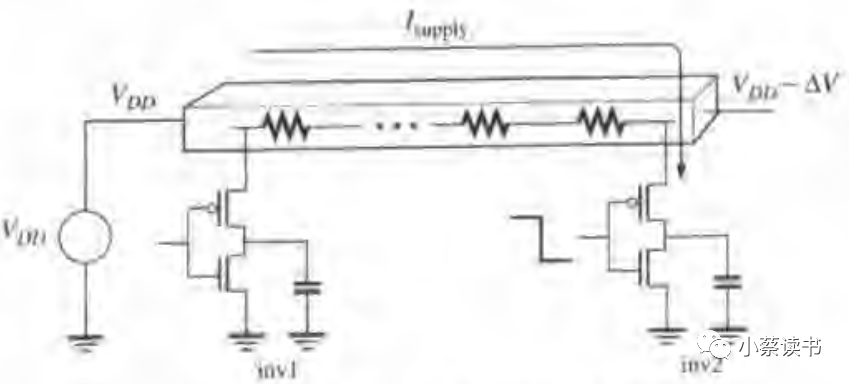

如下图所示,描述了连接在一个有阻抗的电源上的两个大缓冲器。最初,所有电源网格中的电平处于VDD。当大驱动器inv2开始变化时,对电流的需求降低了电源网格的电压。特别是导线电阻产生的电压降会随着电流从外部电源向inv2的流动而增加。在芯片外围的VDD连接点附近的电压保持相当高的水平,在连接到inv2时有V的压降。实际上,IR压降是由于时钟缓冲器、总线驱动器、存储器译码驱动器等的同时变化引起的。这些同时变化事件可以在芯片上的任何地方发生,因此,所有区域都可能受到IR压降问题的影响。当输出电平变到低时地线网格也会受同样类型问题的影响,只是这时的电压值会增加,这有时称为地线反跳(gound bounce)。

3. IR Drop对性能(timing)的影响

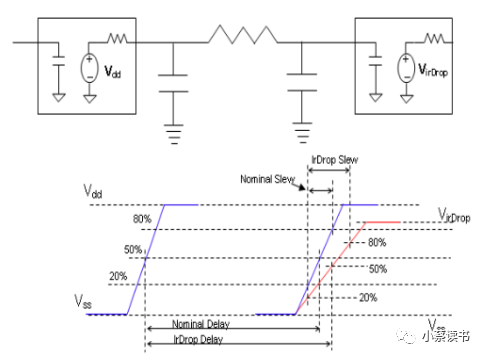

IR Drop可以影响net delay和cell delay。由于峰值电压的减小,有IR Drop的instance的电压摆幅会小于标准电压。这会影响接收器的net delay和input slew(如下图)。

假设driver工作在正常电压Vdd,receiver工作在Virdrop电压。由于cell delay是input slew和outputload的函数,所以IR drop也会影响cell delay。除此之外,电压的降低也会影响cell delay。

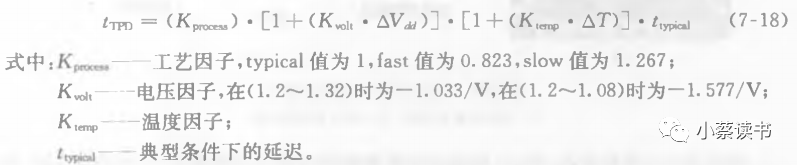

以SIMIC 0.13um工艺为例,总延迟的计算公式如下:

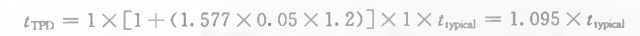

从公式中可以看出,当电压降为5%时,延迟值如下所示,也即延迟增加9.5%。

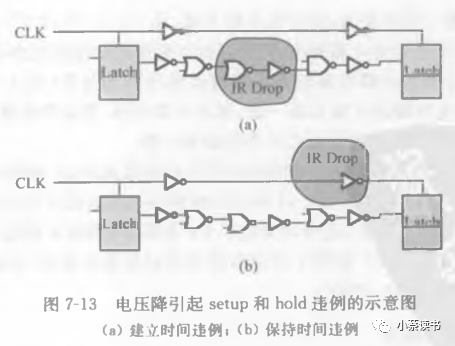

net delay和cell delay的增加会造成时序违例的产生,它可以引起setup和hold违例。如果电压降或延迟位于数据路径,他可能产生setup违例;如果电压降或延迟是位于时钟路径,它可能会产生hold的违例。

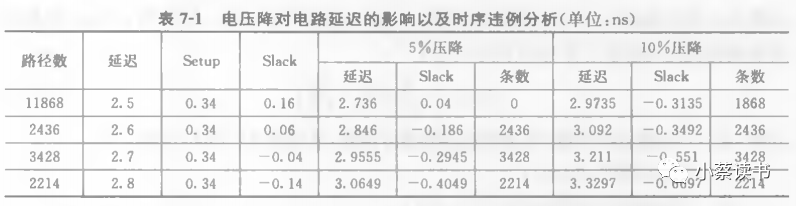

如下面某个设计,其时钟周期为3ns,则电压降产生的时序违例分析如下表所示:

这个设计在没有电压降时,其工作主频可以达到318MHz,在5%电压降时主频为294MHz,如果有10%的电压降,则主频只有272MHz.可见在高频数字电路中,降低电压降对于提高芯片的性能有着至关重要的作用。

4.IR Drop对芯片功能的影响

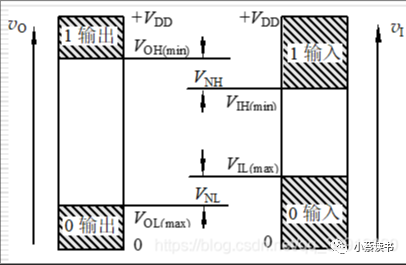

小编是不是搞错了?这玩意还能影响到功能。应该没有搞错,IR Drop损害了逻辑门的噪声容限,这不仅是因为电源网格的电压降低,而且也因为地线网格的电压升高。一旦噪声容限降到预算值(典型值为10%)之下,设计就不保证正确工作了。近年来,电源电压一直降低,以避免晶体管的穿通条件、热电子效应和器件击穿。更近年来的情况是,VDD的降低主要是为了减小功耗而不是其他问题。无论那种情况都导致了越来越小的噪声容限。由于有IR压降,噪声容限更进一步降低,使得在百万晶体管级的设计中处理连线耦合噪声效应变得更加困难。

审核编辑:汤梓红

-

缓解高性能存算一体芯片IR-drop问题的软硬件协同设计2025-07-11 1724

-

芯片的IR drop是什么意思呢?2023-12-06 3972

-

什么是DC IR Drop?DC IR Drop仿真有何意义?2023-09-28 7653

-

谈谈芯片设计中的IR-drop2023-06-16 10440

-

Sigrity PowerDC是如何计算IR Drop Margin?2023-05-12 3623

-

IR Drop与封装分析2023-04-21 4791

-

AD620芯片具有哪些特点引脚功能及应用?2021-11-04 2465

-

MG42630芯片具有哪些引脚功能及特性?2021-10-28 3006

-

独立看门狗与窗口看门狗的主要性能及功能有哪些?2021-08-13 2445

-

LNK564电源管理芯片引脚功能及应用2021-03-24 5544

-

驱动芯片IR2110的数据和功能及应用简介2019-01-28 7544

-

主板芯片的功能及名词解释2010-09-04 1122

全部0条评论

快来发表一下你的评论吧 !