RTL顶层自动连线的秘密武器:Emacs verilog-mode介绍

电子说

描述

RTL顶层自动连线听说过吗?想学吗?我们今天就来介绍自动连线的神器——emacs verilog-mode。

emacs是什么?

江湖流传版:传说中神的编辑器。

维基百科版:Emacs(Editor MACroS,宏编辑器),最初由Richard Stallman于1975年在MIT协同Guy Lewis Steele Jr.共同完成。

verilog-mode是什么

官网的介绍

简单点说就是支持Verilog、SystemVerilog(包括UVM)的emacs语法高亮文件。其中提到Verilog-mode支持Autos——这就是今天的重点。

Verilog-mode是由Michael McNamara

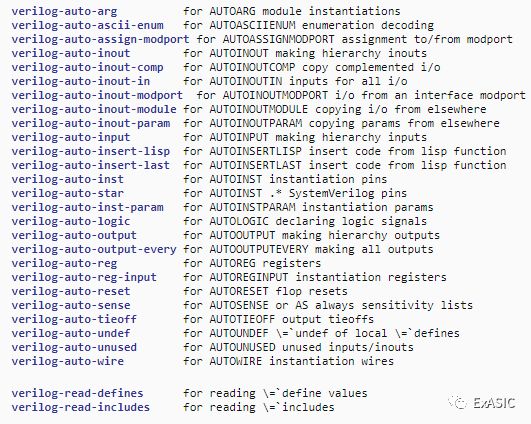

verilog-mode Autos有哪些功能

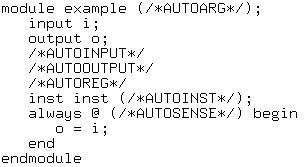

我们来一起看一个官网的例子。

手动编写的verilog代码:

由Autos处理后的verilog代码:

大家可以看到,verilog-mode自动分析出:

模块的端口输入和输出

内部变量

敏感信号列表

提取子模块的端口定义

自动提取子模块的端口定义来连线是今天的重点中的重点。一般来讲,我们实例化模块时大部分的信号名与子模块定义的名字一致即可。如上面代码中的:

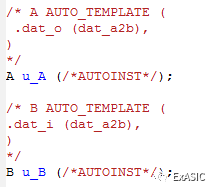

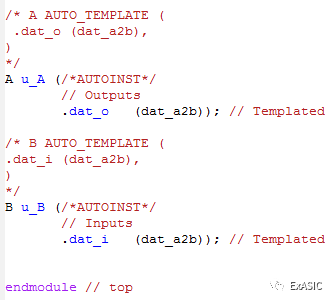

特殊连接关系的处理

但常常我们顶层连接时会换一个名字。比如module A有一个输出端口dat_o,module B有一个输入端口dat_i,这两者怎么连?定义模版AUTO_TEMPLATE,如下:

手动编写的verilog代码:

由Autos处理后的verilog代码:

在哪里找子模块定义?

默认规则:

当前文件夹下找

当前找不到怎么办,指定搜索路径(与仿真器的-y一样)

使用方法:在顶层endmodule后面指定verilog-library-directories,如下:

除了写模版还需要做什么?

只需要Ctrl-C Ctrl-A,仅此而已。

如果修改了子模块或者模版,再按一次Ctrl-C Ctrl-A。

更多功能

verilog-mode下载、安装

新版的GNU Emacs自带verilog-mode

VIM用户咋办?

可以用VIM调动shell命令执行(emacs批处理模式),例如:

:!emacs --batch-f verilog-batch-auto

是不是很简单!

审核编辑:刘清

-

怎么用emac实现Verilog自动连线呢?2024-01-24 3355

-

亚马逊秘密武器明年传将登场 串联智慧语音、IoT、AI、5G及云端2018-10-16 1415

-

图书馆WiFi总掉线?我的秘密武器居然是它.2025-06-10 1691

-

耐达讯RS232转Ethercat网关:建筑驱动连接的“秘密武器”2025-07-21 584

-

科技奥运:小小瓷珠或成中国奥运代表队秘密武器2008-08-08 4084

-

揭秘奥运安防秘密武器之首“全球眼”2008-08-15 4385

-

【电子发烧友】win xp SP2系统秘密武器大曝光2013-03-12 2687

-

云计算为什么能成为物联网的秘密武器?2021-06-18 2318

-

FFT Verilog RTL2010-07-08 988

-

两亿美金回购手机业务 联想还有秘密武器2009-11-30 636

-

自动连线的神器——emacs verilog mode2022-03-29 7296

-

Emacs的verilog-mode介绍2023-01-24 4214

-

GPU的张量核心: 深度学习的秘密武器2023-09-26 2010

-

大屏拼接器在会议室的应用:提升团队协作效率的秘密武器2024-02-26 6268

-

淘宝京东拼多多API:电商营销的秘密武器2025-11-27 643

全部0条评论

快来发表一下你的评论吧 !