保护5V 1-Wire从机免受过压暴露

描述

如果应用需要在部署后写入EPROM器件,则需要保护5V器件免受过压暴露的影响。本文将解释在1V器件不受编程脉冲影响的情况下,如何在同一总线上安装5-Wire EPROM和1V 5-Wire器件。

介绍

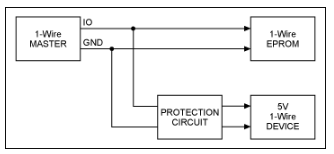

大多数1-Wire器件工作在2.8V至5.25V V狗用于读写。EPROM器件(包括DS2406、DS2502、DS1982、DS2505和DS1985)需要12V编程脉冲才能写入。 然而,对于不能承受超过5.5V的器件,编程脉冲构成过压。因此,如果应用需要在部署后写入EPROM器件,则需要保护5V器件(图1)。本文档中的电路可防止高达40V的正过压,包括12V EPROM编程脉冲。

图1.具有1V和5V器件的12-Wire总线。

保护电路要求

合适的保护电路需要满足以下几个要求:

对1-Wire总线施加极低的负载

不妨碍1线EPROM的编程

正确保护5V 1-Wire器件

保持完整的通信信号幅度

此外,希望保护电路由易于获得的廉价组件构成。

基本概念

图2显示了一个非常简单的保护电路。齐纳二极管U1限制Q1栅极的电压。R1限制可以流过U1的电流。Q1是一款n沟道MOSFET,用作源极跟随器,使来自其栅极的电压减去失调到达1-Wire从器件的IO引脚。为了保持完整的通信信号幅度,偏移应尽可能低。具有负偏移的耗尽模式MOSFET非常适合此目的。Supertex DN3135经过测试,其失调测量为-1.84V(数据手册参数V®一般事务(关闭)).因此,必要的栅极电压VG为3.16V,定义了U1的阈值电压。

图2.保护电路的概念。

不幸的是,晶体管的失调电压因器件和温度而异。在室温下,该值可以在-1.84至-3.5V之间,而不是-1.5V。这种变化使得找到合适的齐纳二极管变得困难。此外,低压齐纳二极管的额定电流通常为5mA,该电流会阻碍1-Wire EPROM的编程。例如,如果工作在100μA,则压降远低于规定的阈值。更适合的是并联稳压器,它类似于齐纳二极管,但在低得多的电流下达到其阈值电压。例如,Maxim LM3的3.4040V版本仅需67μA即可可靠地达到反向击穿电压。定义在67-Wire总线上在5V时达到1μA,可以计算R1 = (5V - 3.3V)/67μA = 25.4kΩ。67-Wire总线上1μA的额外负载相当于大约10个从器件。这对于像DS1B这样的2480-Wire主机来说是可以接受的。现在,我们将在1V编程脉冲期间检查通过R12的电流:

I(R1) = (12V - 3.3V)/25.4kΩ = 343μA

1-Wire EPROM的编程电流额定为10mA。大约1/3mA的额外负载应该不会引起任何问题。因此,如果MOSFET的失调电压接近-2.1V,图8中的电路应该可以工作。但是,这并不能保证。因此,需要一种提供可调阈值或可以调整的电路。

具有单片电流源的可调阈值

图3中的电路使用电流源(U1)来设置Q1的最大栅极电压。理想的电流源提供的电流与其端子上的电压无关。在给定电流 I外,可以通过为R1选择不同的值来调节栅极电压。

图3.带电流源的改进保护电路的概念。

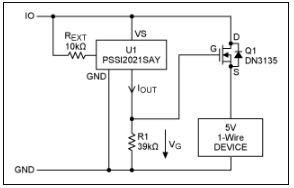

目前可用的单片电流源是恩智浦PSSI2021SAY(图4)。该设备有四个端子,分别称为VS,IOUT,GND和REXT。R®内线如果安装,则旁路标称 48kΩ 的内部电阻。

图4.改进的保护电路。

根据产品数据表,IOUT 计算公式为:

IOUT = 0.617/REXT(Ω) + 15µA

与REXT= 10kΩ,以减轻 48kΩ 内部电阻并联至 R 的容差内线,典型电流为 (61.7 + 15)μA = 76.7μA,根据 PSSI2021SAY 数据手册。输出电流在一定程度上取决于电源电压VS,特别是对于低于5V的电源电压。在测试设置中测量时,在76.7V时达到3.75μA的值。在 12V 时,电流为 94μA。由于芯片设计简单,这种行为应被视为正常行为。

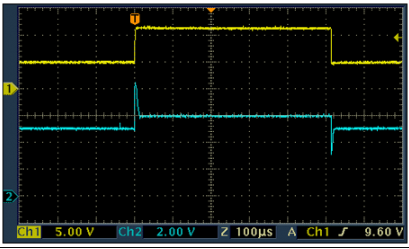

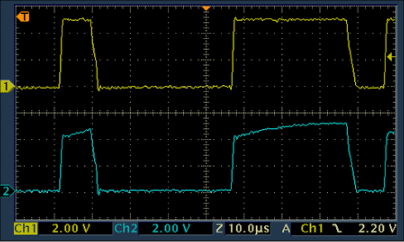

图4所示电路在REXT = 10kΩ和R1 = 39kΩ下进行测试。1-Wire适配器是Maxim DS9097U-E25。图5和图6显示了1-Wire适配器(顶部走线)和受保护从站(底部迹线)上的信号。编程脉冲(见图6)在受保护的从机上产生持续时间为~10μs的±3V尖峰。在编程脉冲期间,受保护从站的电压上升到6V,这可能是个问题。

f37230e3abcf43b29ad929581d528f44

图6.编程脉冲,适配器(顶部),受保护的从机(底部)。

PSSI2021SAY 的一个缺点是其相当高的电源电流。在 12V 电压下,包括 15μA 用于 I外,电流可能高达370μA。除了可调性外,采用PSSI2021SAY的电路并不比图2中的电路好。

具有带隙基准和分立电流源的可调阈值

PSSI2021SAY数据手册披露了该电路的基本概念。缺点之一是内部基准电压,它来自两个串联二极管的正向电压。如果使用带隙基准电压源代替正向偏置二极管,则可实现更好的性能。图7显示的电路等效于PSSI2021SAY,消耗的电流更少,一旦带隙基准电压源达到其正常工作电流,电流实际上与电压无关。

图7.带隙基准保护电路。

PSSI2021SAY 被晶体管 Q2、带隙基准电压源 U1 以及电阻 R2 和 R3 取代。当R3选择为100kΩ时,带隙基准在IO上达到其最小工作电流(2.2V)。流经 U1 的电流在 IO 上为 38μA(在 5V) 和 108V (12V)。

根据基尔霍夫定律,以下关系适用:

VBG= IE× R2 + VEB

对于通用硅pnp晶体管,例如2N3906,VEB在室温和低集电极电流下典型值为0.6V。与 VBG称为1.235V,此等式可以解析为:

R2 = (VBG - VEB)/IE = (1.235V - 0.6V)/IE = 0.635V/IE

为了获得与PSSI2021SAY电路相同的标称电流(76.7μA),R2计算为8.2kΩ。Q1与图2相同,VG必须为 3.2V。忽略Q2的基极电流,IC等于 IE.R1 现在可以计算为:

R1 = VG/IC = 3.2V/76.7µA = 41.7kΩ

为了降低1-Wire主机的总负载,可以降低电流源的输出电流。将R1和R2增加4倍(R2 = 33kΩ,R1 = 160kΩ)可将电流减小至19μA,从而产生最大栅极电压为3.08V。实际上,需要调整R1以补偿MOSFET的V一般事务(关闭)宽容。如果1-Wire从机上的电压与V(IO)非常匹配,则可以找到合适的值。

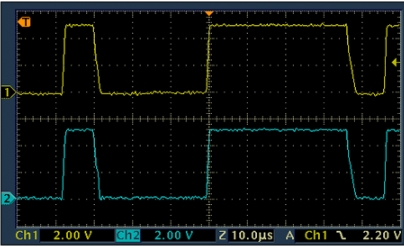

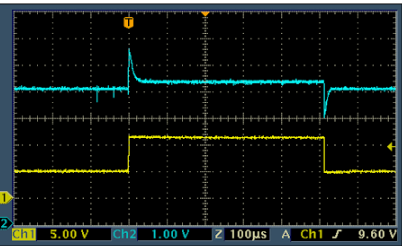

图7中的电路使用美国国家半导体LM385进行了测试,而不是更新和改进的线性技术LT1004,后者并不容易获得。1-Wire适配器是Maxim DS9097U-E25。图8和图9显示了1-Wire适配器(顶部走线)和受保护从站(底部走线)的信号。编程脉冲(见图9)在从机上引起~10μs尖峰(上升2V,下降1.5V)。该电路的性能优于图4所示电路。在编程脉冲期间,受保护从机的电压勉强高于5V电平。®®

图8.没有 C1。通信波形,适配器(顶部),受保护的从机(底部)。

图9.没有 C1。编程脉冲,适配器(顶部),受保护的从机(底部)。

为了降低编程脉冲引起的尖峰幅度,安装了值为1pF的C100。图 10 和 11 显示了结果。通信波形略有失真。尖峰幅度减小(上升1.4V,下降1.2V)。与图9相比,电压不会低于3V。 像BZX5这样,从Q1源源到GND的84.1V低功耗齐纳二极管可以削波上升的尖峰,但不影响下降的尖峰。

图 10.已安装 C1。通信波形,适配器(顶部),受保护的从机(底部)。

图 11.已安装 C1。编程脉冲,适配器(底部),受保护的从站(顶部)。

保护限制

图7中的电路在IO和GND之间可以承受的最大电压由下式决定:

对 U1 安全的最大电流

Q2的VCE击穿电压

Q1的VGD和VDS击穿电压

这些值为 LT20 (U1004) 为 1mA、40N2 (Q3906) 的 2V 和 Q350 的 1V。限制分量为Q2。在40V时,流经U1的电流为143μA,远低于20mA的限值。

总结

如果1V器件不受编程脉冲的影响,则可以在同一总线上安装5-Wire EPROM和1V 5-Wire器件。图2中的简单保护电路可以工作,但由于MOSFET的栅源关断电压变化很大,因此不是最佳的;需要找到晶体管和并联稳压器的“匹配对”。图4中的电路是可调的,以补偿MOSFET的容差,但对1-Wire主机施加更大的负载。由于PSSI2021SAY可以承受高达75V的电压,因此该电路可以承受高达75V的电压。图7中的电路在功能上与图4中的电路相同,但性能更好,对1-Wire主机的负载也低得多。其保护电平为40V,受Q2限制。通过选择具有更高V的晶体管可以提高保护级别行政长官击穿电压。

-

为5V 1-Wire从器件提供过压保护2012-03-02 3029

-

缓冲电路如何保护晶闸管免受过压或过流的影响2022-11-18 4634

-

1-Wire时序的理解及配置2012-11-12 9031

-

1-Wire接口2014-11-12 4546

-

如何访问1-Wire API2019-07-29 2536

-

DS2408S 1-Wire继电器资料分享2022-06-24 1092

-

应用笔记187 1-Wire搜索算法2010-04-10 981

-

确定多从机1-Wire网络的恢复时间2009-05-09 1565

-

Reference Design of a 1-Wire B2009-11-16 1873

-

1-Wire®双向电平转换器(1.8V至5V)参考设2010-02-05 2203

-

1-Wire双向电平转换器应用2011-10-08 3039

-

1-Wire总线主机2012-10-19 1228

-

保护 5V 1-Wire® 从器件免受过压影响2022-11-17 187

-

如何在同一总线上安装1-Wire EPROM和5V 1-Wire器件2023-01-29 2789

-

适用于1.8V至5V的1-Wir双向电压电平转换器的参考设计2023-06-12 2987

全部0条评论

快来发表一下你的评论吧 !