SystemVerilog/Verilog中的各种延迟模型

电子说

描述

为了在仿真阶段能够模拟物理器件的延迟,进行结构模型建模,SystemVerilog/Verilog中提供了两种类型的延迟用以模拟信号经过模型时的传输延迟,这两种延迟分别是:分布延迟(Distributed Delay)和模块路径延迟(Module Path Delay).本文及下面一篇将针对这两种延迟分别进行示例说明.

1 分布延迟(Distributed Delay)

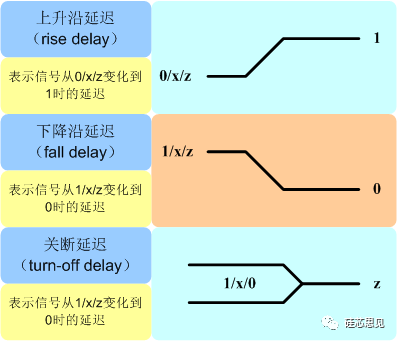

分布延迟指模块内信号从逻辑门的输入到输出或者线网的延迟,这里我们仅以逻辑门延迟为例进行说明.常见的门延迟主要有三种,如下图:

【注意】如果信号从0/1/z变化到x,那么此时的门传输延迟为上述三种延迟最小的.另外,在进行仿真时,有些逻辑门的输出不可能会出现高阻态z,所以对于这些逻辑门实际上就不存在关断延迟了,类似的逻辑门有:and、nand、or、nor、xor、xnor、buf和not等.

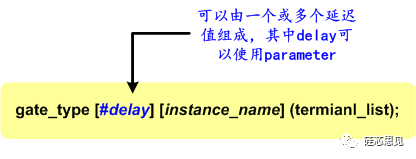

1.1 门级延迟的格式

其中delay用于指定延迟,如果不指定,则所有延迟的默认值为0.如果指定,主要有两种形式:

Ø基本延迟表达式;

Ø"最小值:典型值:最大值"形式;

并且这两种形式结合不同的延迟类型经常会混合使用,下面我们针对两种形式进行说明:

1.2 基本延迟表达式

针对延迟的类型,基本延迟一般不指定"最小值:典型值:最大值",可以简单粗暴的认为在简单延迟中,最小值、典型值和最大值可以认为是相同的,常见的简单延迟使用格式如下表示例.

| 延迟类型 | 无延迟 | 1个延迟值(d) | 2个延迟值(d1,d2) | 3个延迟值(d1,d2,d3) |

| 上升延迟(Rise) | 0 | d | d1 | d1 |

| 下降延迟(Fall) | 0 | d | d2 | d2 |

| 输出为x(To_x) | 0 | d | min(d1,d2) | min(d1,d2,d3) |

| 关断延迟(Turn_off) | 0 | d | min(d1,d2) | d3 |

| 示例 | and u(out,d1,d2) | and #d u(out,d1,d2) | and #(d1,d2) u(out,d1,d2) | and #(d1,d2,d3) u(out,d1,d2) |

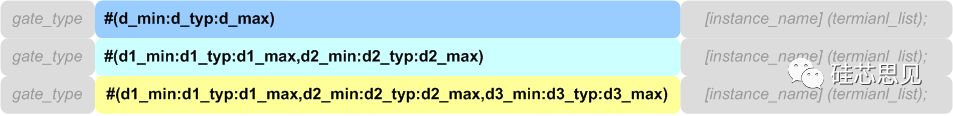

1.3 "最小值:典型值:最大值"形式

采用这种方式表示延迟时,延迟中的每一项将都以"最小值:典型值:最大值"形式出现,根据具体指定的延迟的个数,其常见格式如下:

【示例:指定一个延迟】and #(13) u(out,d1,d2);

| 工况 | 上升延迟 | 下降延迟 | 输出为x延迟 | 关断延迟 |

| 最小 | 1 | 1 | 1 | 1 |

| 典型 | 2 | 2 | 2 | 2 |

| 最大 | 3 | 3 | 3 | 3 |

此时的各种延迟在特定工况下的值都是相同的.

【示例:指定二个延迟】and #(13,46) u(out,d1,d2);

| 工况 | 上升延迟 | 下降延迟 | 输出为x延迟 | 关断延迟 |

| 最小 | 1 | 4 | min(1,4) | min(1,4) |

| 典型 | 2 | 5 | min(2,5) | min(2,5) |

| 最大 | 3 | 6 | min(3,6) | min(3,6) |

此时的两个延迟分别指的是上升延迟和下降延迟,关断和输出为x的延迟取决于每种工况下上升延迟和下降延迟的最小值.

【示例:指定三个延迟】and #(13,46,79) u(out,d1,d2);

| 上升延迟 | 下降延迟 | 输出为x延迟 | 关断延迟 | |

| 最小 | 1 | 4 | min(1,4,7) | 7 |

| 典型 | 2 | 5 | min(2,5,8) | 8 |

| 最大 | 3 | 6 | min(3,6,9) | 9 |

此时的三个延迟分别指的是上升延迟、下降延迟和关断延迟,输出为x的延迟取决于每种工况下上升延迟、下降延迟和关断延迟的最小值.

门单元可以指定这么多种的延迟,那么在进行仿真时如何告诉仿真器应该使用哪种工况下指定的延迟呢?目前在使用主流EDA工具进行仿真时可以针对需要使用的延迟在命令参数中指定"+mindelays"(对应最小值,此时所有的延迟取最小值)、"+typdelays"(对应典型值,此时所有的延迟取典型值)、"+maxdelays"(对应最大值,此时所有的延迟取最大值)来实现,但是每次仿真时只能指定一种延迟模式,并且这种选择在仿真过程中是不能修改的.

2 模块路径延迟(Module Path Delay)

模块路径延迟描述的是模块中信号从源端到目的端传输的延迟,这些路径以及对应的延迟是在模块中的specify块中指定的,其中信号源端一般为input或者inout,而目的端则只能为output或者inout.在specify中指定的模块路径,常见的形式主要三种,分别是:简单路径(Simple Path),边沿敏感路径(Edge Secsitive Path)和条件相关路径(State-dependent Path).

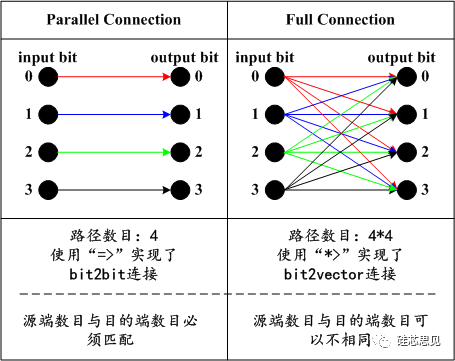

在这三种路径中根据源端和目的端之间路径的可能连接方式又分为两种:并行连接(Parallel Connection)和全连接(Full Connection),在specify块中的三种模块路径中描述延迟时主要就是通过这两种连接方式进行描述的.

2.1 并行连接(Parallel Connection)

并行连接表示每条延迟路径只有一个源端和目的端,其语法格式如下:

(

其中delay_value可以为1~3个延迟量表达方式,延迟量也可以采用"最小值:典型值:最大值"的形式,如果延迟量多于两个,则可以使用小括号将延迟量包括其来,延迟量之间用逗号分隔.

2.2 全连接(Full Connection)

全连接中源端中的每一位可以与目的端中的每一位相连接,即使源端位数与目的端位数不一致也可以,其格式如下:

(

其中delay_value的指定方式同并行连接.

下面是上述两种连接方式的示意图和注意事项和区别:

不管是并行连接还是全连接,都可以应用于模块路径延迟的三种类型中.

2.3 模块路径

2.3.1 简单路径

一般只包含*>和=>连接的路径,在其中仅描述简单的源端到目的端的延迟,属于基本模块路径延迟表示形式.

2.3.2 边沿敏感路径

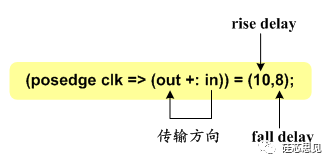

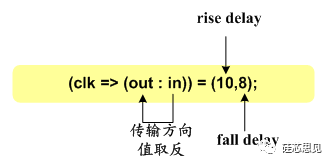

主要用来描述信号在特定边沿事件发生时数据从源端传递到目的端的路径,其中延迟主要指的是边沿敏感事件发生时刻到数据信号传递到目的端的时间,常用的格式如下:

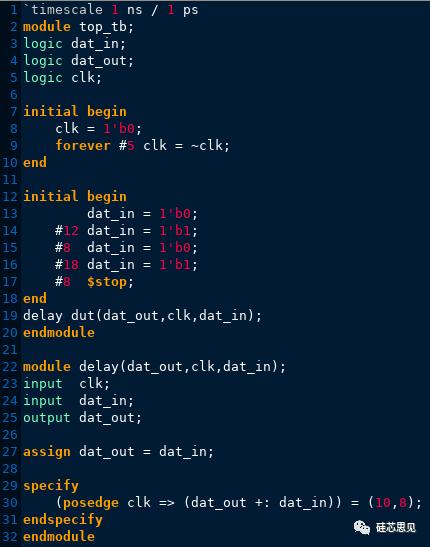

【示例】

【仿真结果】

示例中,在时刻5ns时,clk发生上升沿事件,经过10ns延迟后信号dat_in的上升变化传递到了输出端dat_out.在时刻15ns时,clk再次发生上升沿事件,经过8ns延迟后信号dat_in的下降变化传递到了输出端dat_out,后续变化与此雷同,不再赘述.可见此时的延迟指的是采样事件发生到输出的延迟,并不是数据输入端到数据输出端的延迟.这里需要注意的是在dat_out和dat_in之间指定传输方向是使用了极性操作符"+",主要表示输入到输出是否取反,如果要对数据取反可以将"+"换为"-",但是这里需要注意这个操作符对于仿真来说不会产生任何影响,即在仿真时不会出现取反现象,仅对时序分析工具会产生影响.

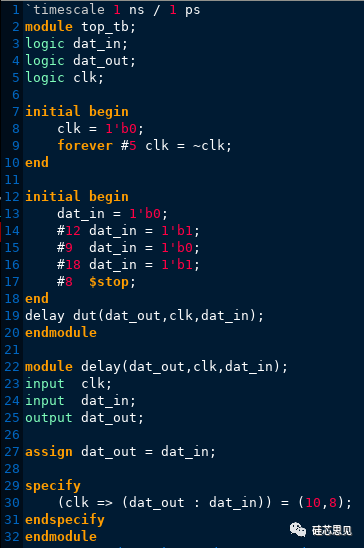

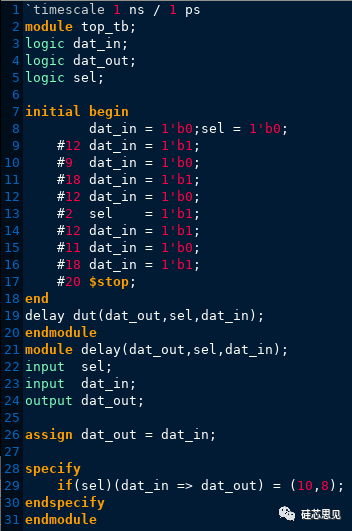

【示例】

【仿真结果】

示例中,在5ns时,clk发生上升沿事件,在clk下一次跳变发生前dat_in保持0,dat_in没有发生变化,dat_out保持不变.在10ns时,clk发生下降沿事件,dat_in的值应该在clk下降沿事件之后10ns后更新至dat_out,但是在clk下一次跳变发生前dat_in变为了1,即dat_in发生了上升变化,所以,此时最终更新至dat_out的值为dat_in的最新值,并且发生在clk下降沿事件发生后的10ns处,即20ns时刻.在20ns时,clk发生下降沿变化,此时dat_in为1,但是在clk下一次跳边沿之前dat_in变为了0,即dat_in发生了下降沿变化,所以,此时最终更新至dat_out的值为dat_in的最新值0,并且发生在clk下降沿事件发生后的8ns处,即28ns时刻.后续变化分析类似,不再赘述.

2.3.3 条件相关路径(状态依赖路径)

在指定条件成立的情况下,才会将延迟作用于模块路径,格式如下:

【示例】

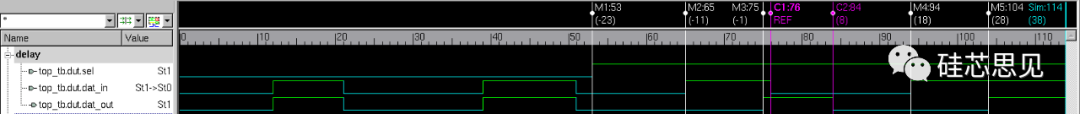

【仿真结果】

示例中,在sel不为高时,此时在specify块中指定的模块路径延迟并不会并不会作用到dat_in到dat_out这条路径上.但是在sel为高后,此时specify块中指定的模块路径延迟会作用到从dat_in传递到dat_out的数据.这里需要注意的是,在specify块中指定条件的if语句块不能使用else分支结构.

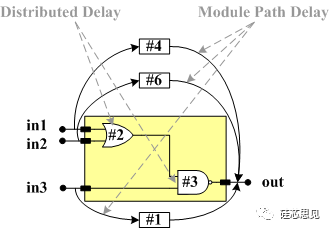

3 分布延迟和模块路径延迟同时存在情况

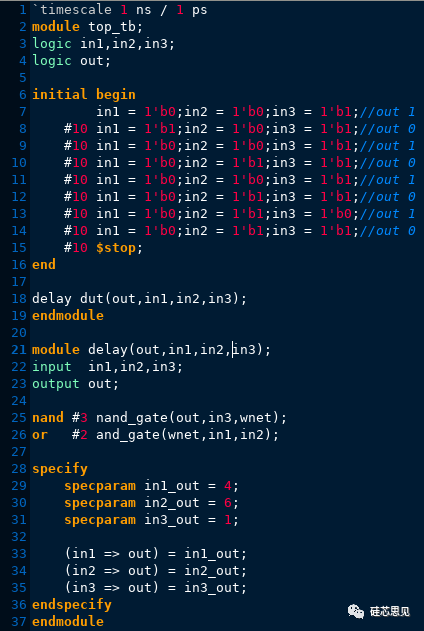

一般情况下,一个模块中不止会包含specify块,还会包含大量的门单元,在specify块中会指定模块路径延迟,模块内的路径上各个基本单元(可以是基本的门级单元、开关级元件或者子模块)又存在分布延迟,模块中这两种延迟经常会共存,那么此时进行仿真时应该使用哪种延迟呢?下面通过下面电路进行示例说明两种延迟对于信号在模块中传递是如何产生影响的.

【电路结构】电路中存在三个输入端口in1、in2、in3和一个输出端out,并且in1到out的模块路径延迟为4个时间单位,in2到out的模块路径延迟为6个时间单位,in3到out的模块路径延迟为1个时间单位,或门产生延迟为2,与非门延迟3.

【示例】

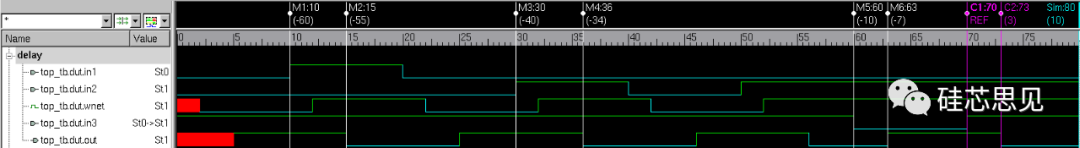

【仿真结果】

示例中针对几个时间点变化汇总如下:

在10ns时,in1变为1,in2为0,in3为1,此时in1和in2经过或操作输出wnet,且或门延迟为2,所以wnet延迟2个时间单位后变化,wnet和in3经过与非门后输出至out,因为此时wnet和in3连接的与非门门延迟为3,所以wnet变化后3个时间单位变化更新至out,此时out变为0,可见此时从端口in1信号的变化到输出端输出的延迟时间不是in1和out之间指定的模块路径延迟4,而是该路径经过的所有门单元延迟总和,即是该路径分布延迟值;

在30ns时,in2从0变为了1,in1为0,in3为1,此时in1和in2经过或操作输出wnet,且或门延迟为2,所以wnet延迟2个时间单位后变化,wnet和in3经过与非门后输出至out,虽然此时wnet和in3连接的与非门门延迟为3,但是因为从端口in2信号的变化延迟到输出端输出的分布延迟为2+3=5,小于从in2到out的模块路径延迟6,所以此时从端口in2信号的变化到输出端输出的延迟时间为6;

在60ns时,in3从1变为了0,in1为0,in2为1,此时因为in1和in2都没有变化,所有wnet保持1,所以此时影响输出的只有in3,in3在60ns变化后,out发生变化的时间为3ns,即与非门的门延迟值,并不是in3到out的模块路径延迟1;

通过上述三个时间点in1、in2、in3的分别变化到out输出的延迟情况可以看出,模块端口的最终延迟取决于分布延迟和模块路径延迟中的最大者,因此本电路输入端口到输出端口的延迟可以表示如下表所示.

| 选项 | 分布延迟 | 模块路径延迟 | 最终延迟 |

| in1 -> out | 2+3=5 | 4 | 5 |

| in2 -> out | 2+3=5 | 6 | 6 |

| in3 -> out | 3 | 1 | 3 |

最后,大家需要注意,上述这些延迟的单位和精度为当前模块使用的时间单位和时间精度.

审核编辑 :李倩

-

SystemVerilog中的Virtual Methods2022-11-28 1186

-

systemverilog学习教程2015-04-01 8655

-

verilog在psoc中延迟2018-11-06 1828

-

使用SystemVerilog来简化FPGA中接口的连接方式2021-01-08 1906

-

循环模型编译器Verilog和System Verilog语言支持指南2023-08-12 452

-

SystemVerilog 3.1a语言参考手册2009-07-22 1900

-

SystemC 和SystemVerilog的比较2010-08-16 5765

-

使用Verilog/SystemVerilog硬件描述语言练习数字硬件设计2022-08-31 3122

-

SystemVerilog中的Shallow Copy2022-11-21 1571

-

从Verilog PLI到SystemVerilog DPI的演变过程2023-05-16 1753

-

verilog/systemverilog中隐藏的初始化说明2023-08-25 2095

-

verilog-2005和systemverilog-2017标准规范2023-09-04 4730

-

SystemVerilog在硬件设计部分有哪些优势2023-10-19 2505

-

SystemVerilog相比于Verilog的优势2023-10-26 2374

-

如何利用Verilog-A开发器件模型2024-10-18 3046

全部0条评论

快来发表一下你的评论吧 !