一种用于先进封装的圆台硅通孔的刻蚀方法

电子说

描述

摘要

在集成电路的制造阶段延续摩尔定律变得越发困难,而在封装阶段利用三维空间可以视作 对摩尔定律的拓展。硅通孔是利用三维空间实现先进封装的常用技术手段,现有技术中对于应用于 CMOS 图像传感器件封装的圆台硅通孔,采用的是在顶部不断横向刻蚀的方式实现的,不利于封装 密度的提高,且对于光刻设备的分辨率有一定的要求。针对现有技术中的问题,一种严格控制横向 刻蚀尺寸 (仅占原始特征尺寸的 3%~12%) 的圆台硅通孔刻蚀方法被研究探索出来。该方法通过调节 下电极功率 (≤30 W),获得了侧壁角度可调 (70°~88°)、通孔底部开口尺寸小于光刻定义特征尺寸 的圆台硅通孔结构。这一方法有望向三维集成电路领域推广,有助于在封装阶段延续摩尔定律。

引言

依循摩尔定律,芯片的特征尺寸越来越小,以满 足器件集成度的增长。但是,当芯片的特征尺寸小到 一定程度会出现量子效应等现象,从而改变芯片目前 所遵循的物理规律。因此,长期来看,单纯采用越来越 先进的工艺技术来延续摩尔定律是不可持续的。值得 注意的是,先进工艺技术节点对特征尺寸的微缩主要 还是一种针对平面区域的概念。目前最先进的环栅技 术尽管可以实现晶体管立体 / 三维方向的堆叠,但还 没有确切的量产记录(韩国三星公司声称已可以实现 量产)。加入封装交流群,加VX:tuoke08。相比于在芯片制造过程中利用三维空间,在芯 片封装过程中利用三维空间的难度更低。能够利用三 维空间的区域将增加芯片的集成度,实际上就可以视 作对摩尔定律的拓展。利用三维空间进行堆叠封装, 可以实现高性能的异质集成,这样的系统级封装具有 更高的容量、更好的性能和更高的良率。

硅通孔(TSV)技术是先进封装中的常用技术之 一,采用硅通孔技术实现三维空间中芯片或者线路 的垂直互连具有降低寄生效应、提高运行速率和降低 器件功耗等优点。硅通孔技术在先进封装中的应用 可以分成以下几类:(1)在三维空间中实现芯片的垂直 堆叠互连,这类通孔被称作 3D 硅通孔(硅通孔是在芯 片所在的硅片上开通的,封装与芯片制造的界限模糊 化,因此也被称作 3D IC);(2)采用硅转接板将不同芯 片的通信距离拉近,硅转接板上的这类通孔被称作 2.5D 硅通孔;(3)采用圆台硅通孔技术,从而利用三维 空间对图像传感器件进行封装。

同时,硅通孔技术也面临一些挑战。尽管采用硅 通孔的三维封装电学性能优良,但其工艺流程相对复 杂,在生产成本上不如采用重新布线技术来实现三维 封装。具体到硅通孔技术的工艺流程,其最主要的步 骤是硅通孔刻蚀和钝化层、阻挡层金属填充。在进行 硅通孔刻蚀时,通常采用 Bosch 工艺,但这种工艺形成 的硅通孔角度一般比较垂直,不利于后续的钝化层、 阻挡层金属填充。例如,在 3D 系统级封装的硅通孔中 深宽比比较大,一般需要原子层沉积等技术来实现孔 的填充,导致产能降低。另外,虽然采用直孔替代斜孔 可以提高封装的密度和可靠性,但是采用直孔无法挂 胶(即无法通过旋涂实现孔侧壁钝化胶的涂布),需要 改用等离子体增强化学气相沉积(PECVD)工艺生长 绝缘层、物理气相沉积(PVD)工艺生长种子层和电镀, 而每增加一步工艺过程都会增加产品的制造成本,过 长的工艺路线会使产品失去商业竞争力。因此,对于 应用于图像传感器件的封装,其通孔一般采用圆台结构,可以通过旋涂实现孔侧壁钝化胶的涂布,降低成 本。现有的技术主要利用硅的侧向刻蚀获得这类圆台结构,即现有技术对通孔侧壁角度的工艺量化控制 是通过调节上开口的尺寸实现的。因此,现有技术中 的圆台通孔的下开口尺寸与光刻胶定义的尺寸相同, 而上开口的尺寸则大于光刻胶定义的尺寸。这就对光 刻分辨率提出了更高的要求,即在圆台通孔的上开口 尺寸一定的情况下,需要利用***定义出更小的图 形。与光刻定义线条状图形不同,定义孔状图形对光 刻分辨率的要求更高,当孔的尺寸小到一定程度后, 定义的图案会出现不圆等异常。并且,硅的侧向刻蚀 容易导致开口尺寸的均匀性难以控制,甚至相邻 2 个 孔之间会发生穿通,使得 2 个孔之间需要预留安全距 离,限制了封装密度的提高。针对上述问题,本文提出 了一种应用于图像传感器件封装的圆台硅通孔的刻 蚀方法,可以保证其上开口与光刻定义的尺寸近乎一 致(偏差仅为 3%~12%),从而降低工艺整合时对光刻 工艺的要求,并且可以避免硅侧向刻蚀所导致的封装 密度下降的问题。

2 试验部分

2.1 试验仪器与材料

本研究使用的试验仪器包括:上海微电子公司生 产的 SMEE SSB500 步进式***,北方华创公司生 产的 HSE P230 等离子体刻蚀机,日立公司生产的 SU8010 冷场发射扫描电子显微镜。本研究使用的试验材料包括:12 英寸硅晶圆,电子 级 O2、He、SF6、C4F8、Ar,德国 All Resist 公司生产的光刻 胶和显影液,北京化工厂生产的 H2SO4(浓)和 H2O2。

2.2 试验方法

本研究使用的 12 英寸硅晶圆,其(100)晶面垂直 于晶圆平面朝上。试验采用 Piranha 溶液H2SO4(浓)和 H2O2 以 7:3 的配比组成] 清洗后,在晶圆上旋涂光刻 胶。然后,试验使用步进式***进行光刻,并通过显 影定义出待刻蚀的图形。最后,试验使用等离子体刻 蚀机进行刻蚀,刻蚀后的剖面结构使用冷场发射扫描 电子显微镜进行表征。

其中,等离子体刻蚀是关键的试验步骤,等离子 体刻蚀的基准工艺配方如表 1 所示。

其中,气压用于达到等离子体产生的条件,应用 于刻蚀机的等离子体属于低温等离子体,需要一定的 真空才能产生,而电感耦合等离子体形成所需要的真 空一般在 26.66 Pa 以下;上电极功率产生等离子体;下 电极射频功率牵引腔室中的等离子体向下运动作用 于晶圆;SF6 用于产生氟基自由基刻蚀硅片;O2 用于形 成硅氧复合物保护孔道结构的侧壁,从而实现各向异 性刻蚀;工艺时间与所需要的刻蚀深度相关。

2.3 试验结果

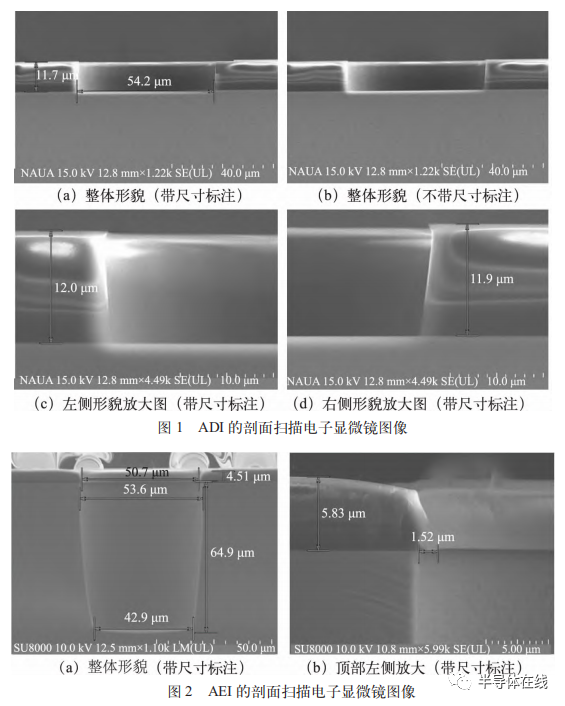

图 1 为光刻胶显影后(即等离子体刻蚀之前)检测 (ADI)的剖面扫描电子显微镜图像,光刻所定义出的 特征尺寸约为 50 μm。

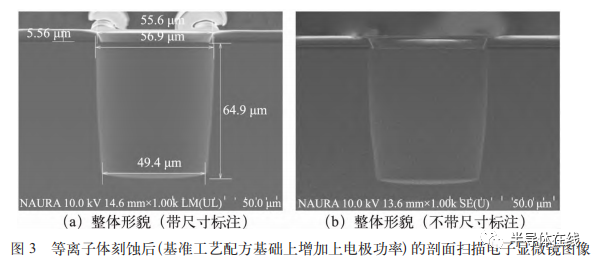

图 2 为等离子体刻蚀后检测(AEI)的剖面扫描电 子显微镜图像。

从图 2(a)可以看出,其硅通孔的上开口尺寸(大 约为 54 μm)与光刻定义的特征尺寸(大约为 50 μm) 相差无几,下开口尺寸(大约为 43 μm)则显著小于光 刻定义的特征尺寸,再结合约 65 μm 的刻蚀深度值, 可得出其侧壁的平均角度大约为 85°,有利于后续的 填充工艺;而从图 2(b)的放大图可以更加清晰地看 出,硅通孔的顶部没有出现明显的在光刻胶底部向硅 通孔内侧的刻蚀现象,即没有明显的下切现象出现。进一步的研究还发现,当光刻定义出的图案的特征尺 寸减小时,采用上述等离子体刻蚀技术所刻蚀出的图 形的下切尺寸的绝对值也会随之减小,而下切尺寸占 光刻定义尺寸的比值虽有上升,但有逐步趋于饱和的 趋势,预示其有望向尺寸更小的三维封装方向发展, 但相应地也存在一定的挑战。

3 分析与讨论

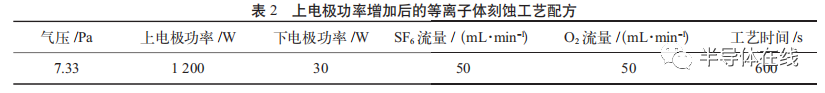

对形成上述形貌的影响因素进行探讨。首先,调 整工艺配方中的上电极功率,若上电极功率增加,对 形貌的影响不大(上开口尺寸约为 57 μm,下开口尺寸 约为 49 μm,刻蚀深度约为 65 μm,下切现象加重,但 侧壁的平均角度保持为约 85°不变),图 3 为等离子体 刻蚀后的剖面扫描电子显微镜图像。上电极功率增加 后的等离子体刻蚀工艺配方如表 2 所示。

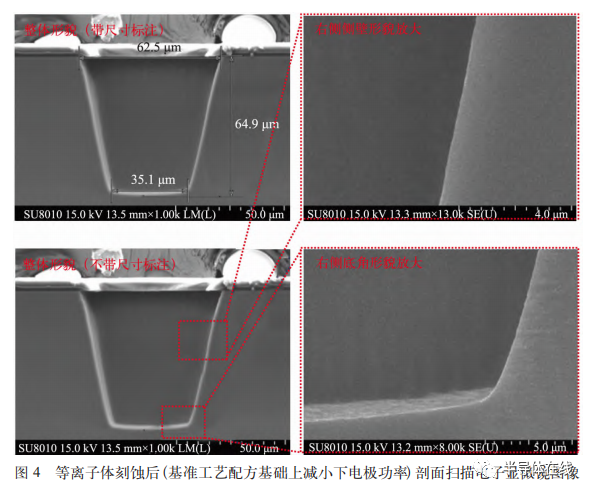

试验结果证明,上电极功率并不是形成该形貌的 主要影响因素。通过进一步的探索发现,若减小下电 极功率,则可以获得侧壁角度更加倾斜的硅通孔(上 开口尺寸约为 62 μm,下开口尺寸约为 35 μm,刻蚀深 度约为 65 μm,侧壁平均角度约为 76°),图 4 为其等 离子体刻蚀后的剖面扫描电子显微镜图像。

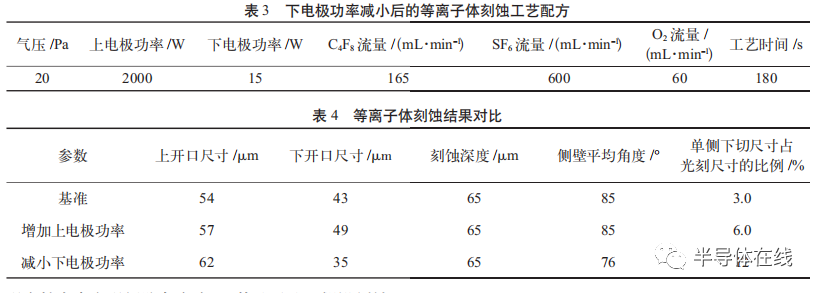

从图 4 可以看出,相比于高深宽比的 Bosch 工艺, 该等离子体刻蚀技术在侧壁粗糙度方面具有优势,有 利于后续工艺以及保证器件的电学性能。下电极功率 减小后的等离子体刻蚀工艺配方如表 3 所示。

对试验的结果进行分析,增加上电极功率会加大 下切现象(通过单侧下切尺寸占光刻定义出的原始特 征尺寸的比例来定量描述该现象),但不会明显影响 侧壁的平均角度,而减小下电极功率则可以明显减小 侧壁的平均角度,等离子体刻蚀结果对比如表 4所示。

从唯象的角度,对减小下电极射频功率可以获得 圆台型微孔结构进行分析讨论:对于电感耦合等离子 体刻蚀机而言,其上电极射频功率用于产生等离子 体,下电极射频功率用于牵引腔室中的等离子体向下 运动并作用于晶圆。等离子体的平均自由程有限,在 孔道结构中运动时更容易发生湮灭,当下电极功率不 足时,会使得到达孔道结构底部的等离子体明显少于 顶部,进而获得上大下小的圆台型微孔结构。

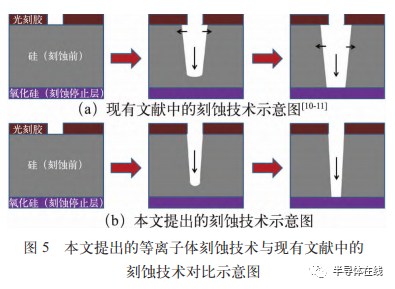

现有文献中,硅通孔的下开口尺寸与光刻胶定义 的特征尺寸保持一致,倾斜侧壁是通过较大的下切现 象获得的,图 5(a)为现有文献中的刻蚀技术示意图。而本文提出的刻蚀方法,是硅通孔的上开口尺寸与光 刻胶定义的特征尺寸保持一致,通过对侧壁的保护作 用使得下开口明显小于光刻胶定义的特征尺寸而获 得倾斜侧壁。图 5 为本文提出的等离子体刻蚀技术与 现有文献中的刻蚀技术对比示意图,当光刻胶定义的 特征尺寸一定的情况下,通过本文提出的刻蚀方法能 得到尺寸更小的硅通孔结构,从而使得硅通孔技术对 于光刻分辨率的要求降低。从定量的角度分析,采用现有技术来实现侧壁角度为 76°的硅通孔,假设刻蚀 深度为 65 μm、光刻定义的特征尺寸为 50 μm,通过一 个简单的三角函数运算可以得到现有技术的上开口 需要达到 82 μm(现有技术的下开口尺寸与光刻定义 的特征尺寸 50 μm 保持一致),比原始的特征尺寸 50 μm 多出 32 μm,比本文报道的上开口尺寸还要多 出 20 μm,单侧的下切值占特征尺寸的比例达到 32%, 远大于 3%~12%的比例,不利于封装密度的提高。

另外,不同于集成电路制造领域(特别是制约先 进制程发展的特征尺寸领域)的光刻定义的图案(主 要是线条状的图案),先进封装领域的光刻图案主要 是圆孔状的图案,在相同特征尺寸下的圆形图案比线 条状图案对光刻分辨率的要求更高。

对硅通孔的侧壁角度进行进一步的分析:一方 面,硅通孔刻蚀后的工艺是钝化胶的涂布工艺或者通孔的填充工艺,所以通孔刻蚀的侧壁不能太直,否则 不利于后续的钝化胶涂布(无法挂胶)或者填孔工艺 (封口效应);另一方面,通孔刻蚀的侧壁又不能太斜, 太斜的话会降低晶圆利用率,并且在回刻步骤中容易 破坏侧壁的绝缘层。因此,这类圆台硅通孔的侧壁倾 斜角度在 70°~88°最适宜。研究结果证明,通过调节下 电极功率可以实现圆台硅通孔侧壁倾斜角度的调节。

本技术所能实现的硅通孔深宽比还有待提升,目 前并不适合集成电路的高密度互连,更加适合分立器 件的先进封装,例如微机电系统器件(如低阻硅柱的 三维互连等)以及图像传感器件等的三维封装。此 类器件的共同特征是所需的互连接口数量较少,而器 件尺寸又相对比较大。另外,采用本技术形成的硅通 孔侧壁粗糙度具有优势,有利于减少光学传输损耗, 还可以应用于半导体照明等领域。

4 结论

本文提出了一种圆台硅通孔的刻蚀方法,可以在 先进封装(特别是针对图像传感器件的封装)中引入 侧壁平均角度在 70°~88°的硅通孔互连结构。通过施 加 30 W 及以下的下电极功率实现圆台硅通孔的刻 蚀,该圆台硅通孔的下开口尺寸显著小于光刻定义的 特征尺寸。与现有文献中的刻蚀技术不同,该刻蚀技 术可以降低工艺整合时对光刻分辨率的要求,且有利 于提高封装密度。该刻蚀技术对于高深宽比的刻蚀还 具有一定的局限性,对于如何将该技术扩展到三维封 装硅通孔刻蚀还需要进一步的研究和探索。

审核编辑:汤梓红

-

一种简单的可控硅好坏判断方法2009-07-28 6497

-

硅通孔封装工艺流程与技术2023-05-08 5693

-

硅通孔电镀材料在先进封装中的应用2025-10-14 6325

-

【转帖】干法刻蚀的优点和过程2018-12-21 5617

-

中微推出用于3D芯片及封装的硅通孔刻蚀设备Primo TSV200E(TM)2012-03-15 1759

-

基于功能细分的硅通孔容错方法2017-01-07 553

-

晶体硅太阳能电池刻蚀的作用及方法与刻蚀的工艺流程等介绍2017-09-29 1938

-

实现高精度深硅刻蚀的方法2020-10-09 16677

-

硅通孔设计有助于实现更先进的封装能力2022-10-27 1652

-

干法刻蚀工艺介绍 硅的深沟槽干法刻蚀工艺方法2023-07-14 9688

-

先进封装中硅通孔(TSV)铜互连电镀研究进展2023-09-06 2217

-

PDMS湿法刻蚀与软刻蚀的区别2024-09-27 1054

-

先进封装中的TSV/硅通孔技术介绍2024-12-17 3224

-

芯片湿法刻蚀方法有哪些2024-12-26 1597

全部0条评论

快来发表一下你的评论吧 !