FCBGA封装的CPU芯片散热性能影响因素研究

电子说

描述

来源 | 计算机工程与科学 作者 | 陈彪,陈才,张坤,叶琴 单位 | 飞腾技术(长沙)有限公司 原位 | DOI: 10.3969/j.issn.1007-130X.2023.03.004

摘要:散热设计是芯片封装设计中非常重要的一环,直接影响芯片运行时的温度和可靠性。芯片内部封装材料的尺寸参数和物理特性对芯片散热有较大影响,可以用芯片热阻或结温的高低来衡量其散热性能的好坏。通过数值模拟(有限体积法)的方法,对某国产FCBGA封装的CPU散热性能进行研究,分析CPU封装内的各层材料尺寸、导热系数及功率密度等因素对CPU温度和热阻的影响。研究结果表明:TIM1导热系数在35 W/(m·K)以内时,TIM1导热系数和厚度对CPU散热有较大影响;晶圆面积(功率密度)对CPU散热有较大影响,晶圆厚度对CPU散热影响不大。

01引言

随着万物互联、云计算和5G 商用的算力需求日益增长,计算芯片的性能需求也越来越高,而计算性能的提高又引起芯片的功耗迅速增长。图1为某国产CPU平 台 和Intel CPU平台近三代 CPU的热设计功耗TDP(Thermal Design Power)增长趋势图。从图1可以看出,其功耗年增长率接近20%。同时,芯片集成化和小封装的需求也不断增长,这就导致了芯片的功率密度(单位面积的功耗)越来越高,因此芯片散热问题日趋严峻。芯片散热是将芯片晶圆产生的热量传递到外界环境中去,主要通过对流、传导和辐射3种换热形式进行。

图1 服务器CPU功耗增长趋势

02CPU 散热方式

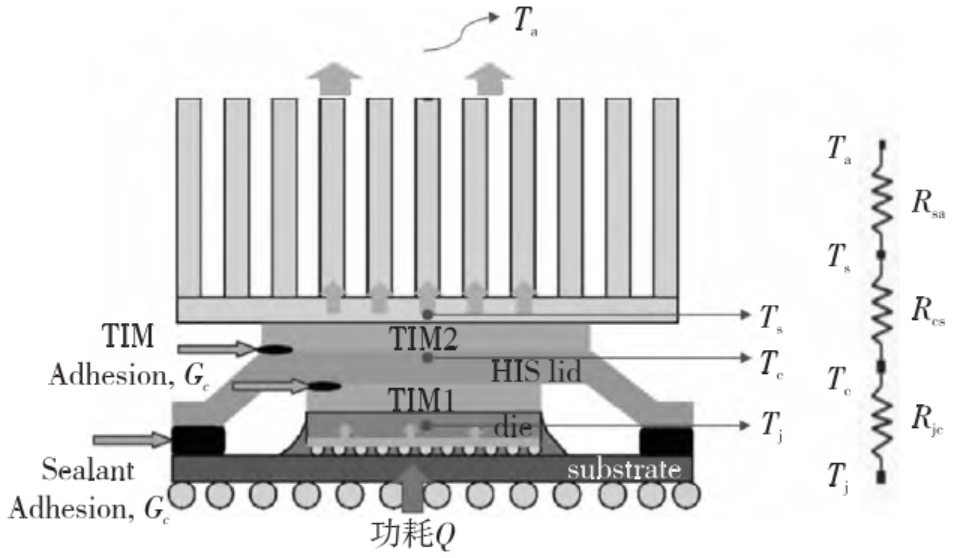

对于FCBGA(Flip Chip Ball Grid Array)倒装球栅阵列封装的CPU芯片来说,通常有2个传热路径:一部分热量通过封装底面的焊盘传导至主板上进行散热;另外一部分热量通过封装顶面传导至散热器,再由散热器向外界环境散热。根据FCBGA封装的结构特性和相关研究表明,约90%以上的热量是通过封装顶面传导至散热器进行散热。因此,为提高芯片散热效率,需要尽量减少芯片晶圆到外界环境的散热热阻。如图2所示,为某FCBGA封装的CPU传热结构和传热热阻链路示意图。

图2 某FCBGA封装CPU传热路径

根据CPU的传热热阻路径可以得到如式(1)和式(2)所示的热阻和温差计算公式:

Tj-Ta=Q*(Rjc+Rcs+Rsa) (1)

Tj-Ta=ΔTjc+ΔTTIM2+ΔTheatsink (2)

其中,Tj表示芯片结温,单位为℃;Tc(见图2)表示芯片壳温,单位为℃;Ts(见图2)表示散热器基板温度,单位为℃;Ta 表示环境温度,单位为℃;Q表示芯片功耗,单位为W;ΔTjc 表示芯片结壳温差,单位为℃;ΔTTIM2 表示界面材料 TIM2的上下表面温差,单位为℃;Theatsink表示散热器基板和空气的温差,单位为℃;Rjc表示芯片结壳热阻,单位为℃/W,主要由封装结构、材料属性决定;Rcs表示接触热阻,单位为℃/W,主要由 TIM2的厚度、导热系数及有效传导面积决定;Rsa表示散热器热阻,单位为℃/W,主要由散热器本身属性决定。

由式(1)热阻计算公式可知,当环境温度和芯片功耗一定时,芯片结到外界环境的热阻越低,芯片的结温就越小。而芯片结到环境的热阻由结壳热阻、接触热阻及散热器热阻三者之和组成,其中结壳热阻为芯片内部热阻,接触热阻和散热器热阻为芯片外部热阻。

本文以芯片内部热阻为研究目标,通过芯片级热仿真和控制变量法,分析芯片封装结构和材料参数对芯片散热效率的影响,即对芯片结壳热阻或温度的影响。

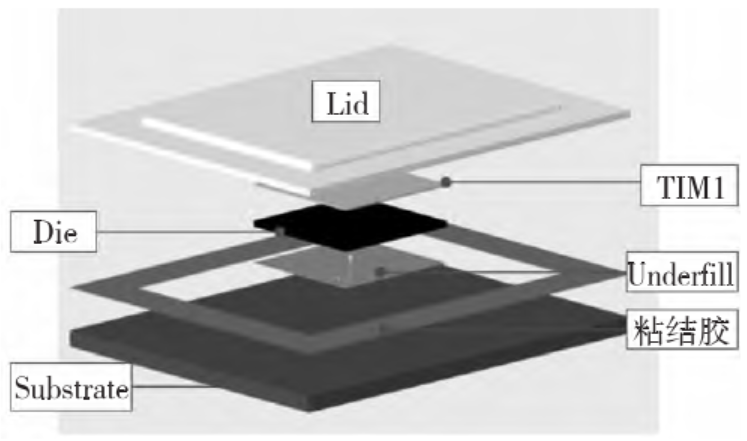

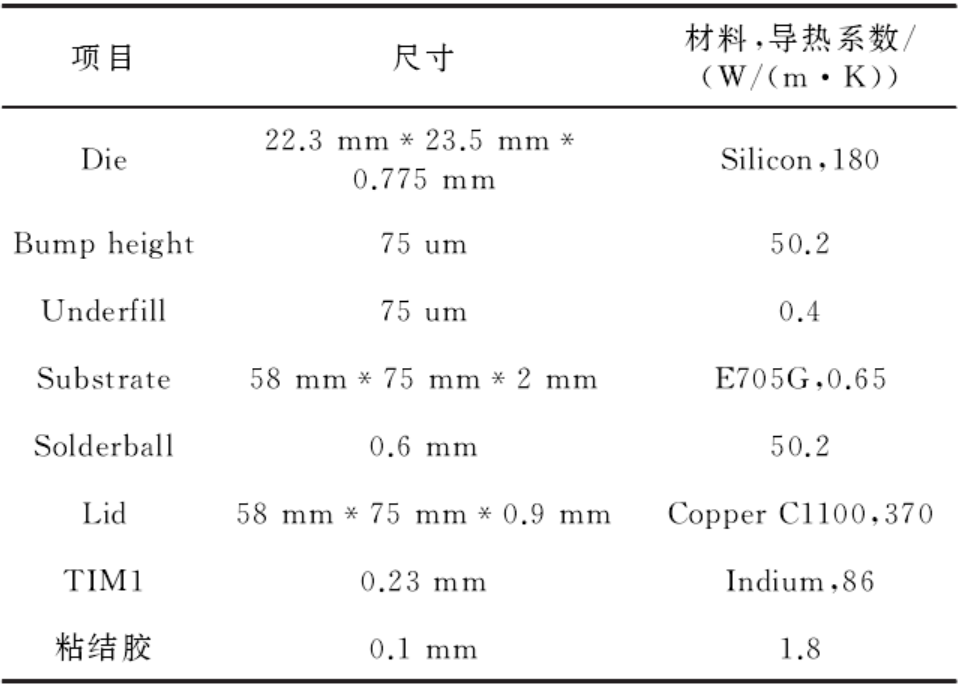

03某 CPU 封装结构及参数定义

本文以某国产CPU为研究对象,分析 CPU封装各个部件的结构尺寸和材料参数对芯片散热的影响趋势。图3为该CPU 的封装结构图。如图3所示,该 CPU 封装结构由上往下分别为散热盖(Lid)、界面材料 (TIM1)、晶圆 (Die)、填底材料(Underfill)、粘结胶、基板(Substrate)和焊球(Sol-derball)。因为焊球数量有3000余个,如果详细建模会导致总体网格数量和计算量过大,因此通过等效法将焊球归一为各项异性的整体模块,节省计算资源。

图3 某CPU封装结构图

图3中,Lid表示 CPU 封装顶盖,对 CPU 内部起了一个物理隔离和保护的作用,同时具有一定的散热作用,材质为纯铜,导热系数较高;TIM1表示热界面材料,起到粘结封装盖板和晶圆的作用,同时具有传热效果,能降低晶圆和盖板间的接触热阻;Die表示 CPU 晶圆,材料为纯硅;Underfill表示填底材料,用于填充晶圆和基板之间的缝隙,是倒装芯片中使用的材料。

表1给出了该芯片封装的结构尺寸和导热系数参数。

表1 某 CPU 封装物理参数

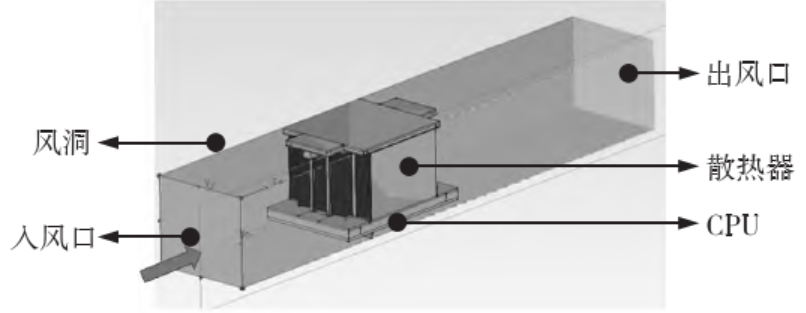

04研究方法

本文利用数值模拟技术,建立一个数值风洞,通过模拟CPU在数值风洞中的散热情况,研究CPU封装材料和结构参数对其散热的影响。如图4所示,为仿真软件中构建的数值风洞,CPU 通过一种2U翅片散热器进行散热,风洞入口处给以一定风量的入口边界条件,以此计算 CPU 的温度分布和最大结温,并研究 CPU 最大结温和各个影响因素之间的关系。

图4 数值风洞

05研究结果及分析

5.1 TIM1导热系数对 CPU 散热的影响

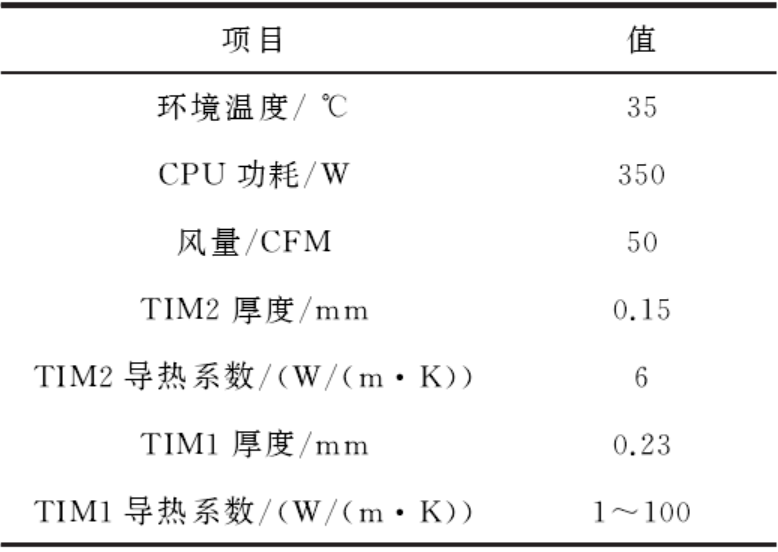

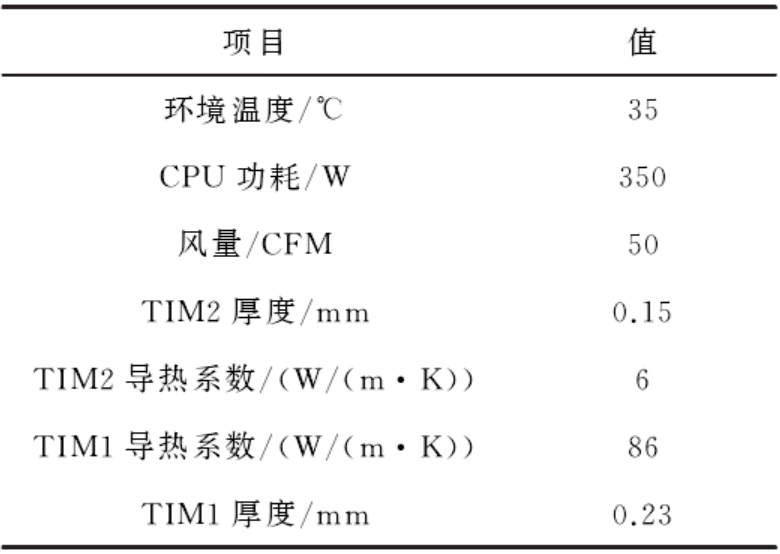

控制其他参数不变,研究 TIM1 导热系数从1~100(W/(m·K))变化时,CPU 最大结温的变化情况。表2为仿真条件。

表2 TIM1导热系数的仿真条件

通过一系列的仿真计算,得到 CPU 最大结温的变化曲线图,如图5所示。

由图5可以看出:

(1)TIM1导热系数低于10 W/(m·K)时,导热系数的提升对CPU结温的改善比较显著;

(2)TIM1导热系数超过35 W/(m·K)时,CPU结温随导热系数增高而下降的趋势放缓,直到稳定不变;

(3)该型号 CPU 使用的 TIM1材料(Indium)导热系数为86 W/(m·K),处于曲线稳定状态;

(4)由于散热器性能不变,所以 CPU 壳温基本不受TIM1导热系数影响。

图5 CPU壳温、结温、结壳温差与TIM1导热系数的关系曲线

5.2 TIM1厚度对 CPU 散热的影响

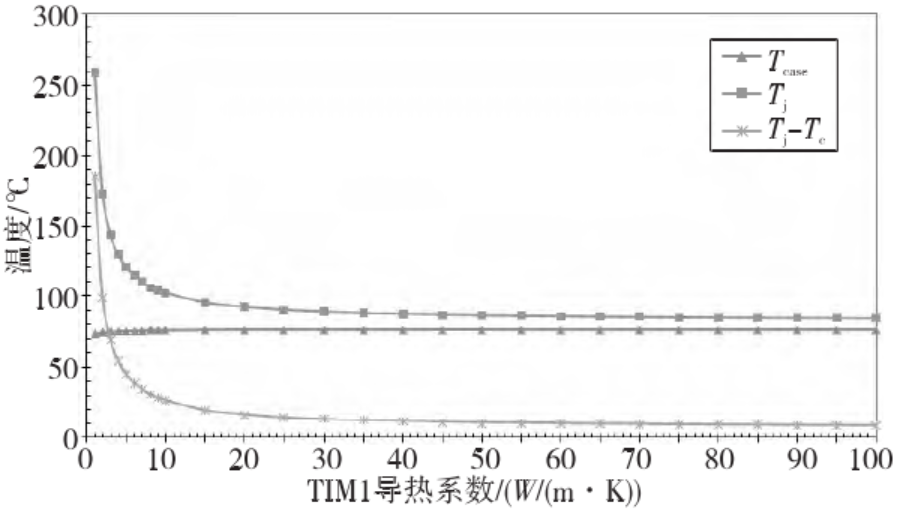

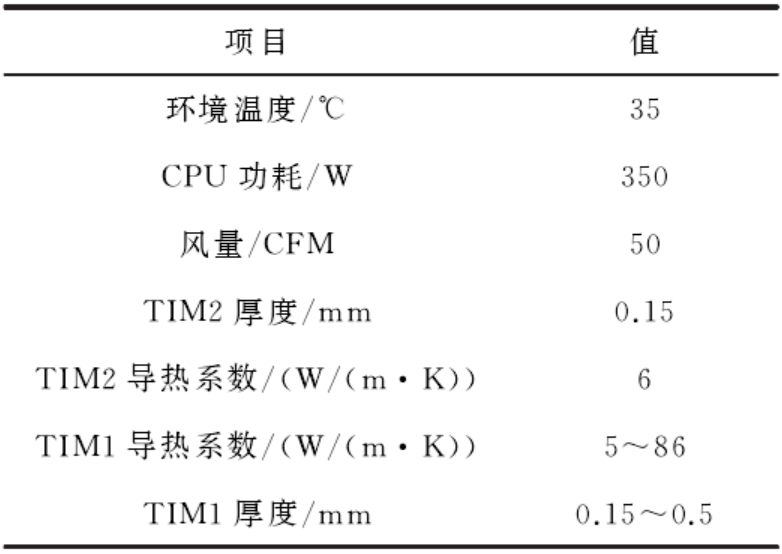

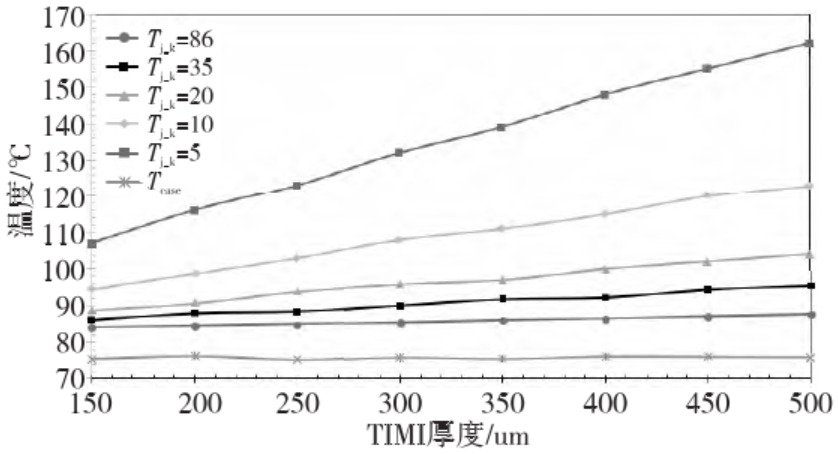

研究方法同上。由于在不同 TIM1导热系数情况下,CPU 结温随 TIM1厚度变化的趋势有一定差别,因此本节研究了不同 TIM1导热系数情况下,TIM1厚度变化对 CPU 结温的影响。根据5.1节的计算结果,选取几组典型的 TIM1 导热系数(5 W/(m·K),10 W/(m·K),20 W/(m·K),35 W/(m·K),86 W/(m·K)),TIM1厚度控制在 0.15~0.5mm变化,计算不同导热系数情况下,TIM1厚度变化对CPU最大结温的影响。表3为本节的仿真计算条件。

表3 TIM1厚度的仿真条件

图6为计算得到的CPU最大结温和TIM1厚度之间的变化曲线,每一组导热系数值对应一条变化曲线。

图6 CPU结温与TIM1厚度的关系曲线

从图6可以看出:

(1)TIM1厚度增大时,CPU 结温有升高趋势;

(2)TIM1导热系数越小,CPU 结温随 TIM1厚度增加而升高的趋势越明显;

(3)TIM1 导热系数超过 35 W/(m·K)后,TIM1厚度增加对CPU结温影响较小;

(4)该型号 CPU 使用的 TIM1材料(Indium)导热系数为86 W/(m·K),此时 TIM1 厚度在150~500um变化,对 CPU 结温的影响可以忽略不计;

(5)由于散热器性能不变,因此 CPU 壳温基本不受TIM1厚度和导热系数影响。

5.3 晶圆厚度对 CPU 散热的影响

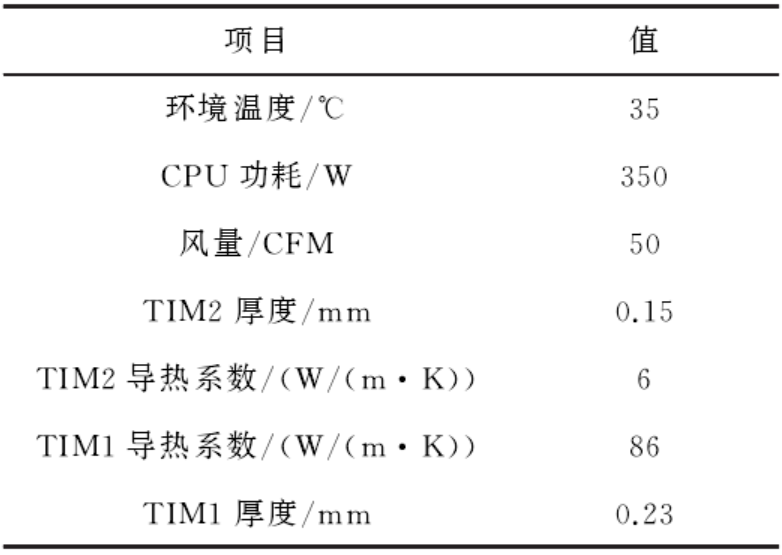

研究方法同上,控制其他参数不变,研究晶圆厚度在500~1000um变化时,CPU 最大结温的变化情况。表4为基本仿真条件。

表4 晶圆厚度的仿真条件

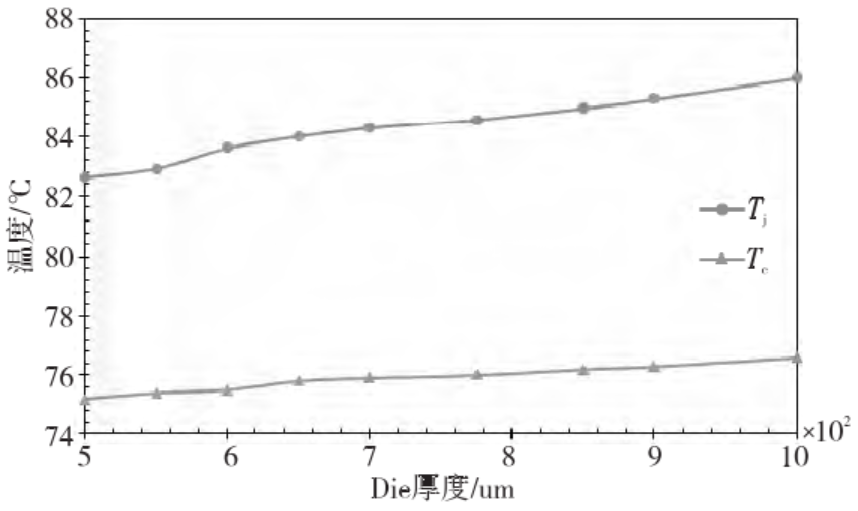

图7为计算得到的CPU最大结温和晶圆厚度之间的变化关系曲线。

图7 CPU结温、壳温与晶圆厚度的关系曲线

从图7可以看出:

(1)Die的厚度增加;CPU 结温随之升高;

(2)Die的厚度从0.5mm 增加至1mm;CPU温度升高约3.5℃;

(3)由于散热器性能不变,因此 CPU 壳温基本不受Die厚度的影响;

(4)总体来看,Die厚度小范围的变化对 CPU散热影响较小。

5.4 晶圆功率密度对 CPU 散热的影响

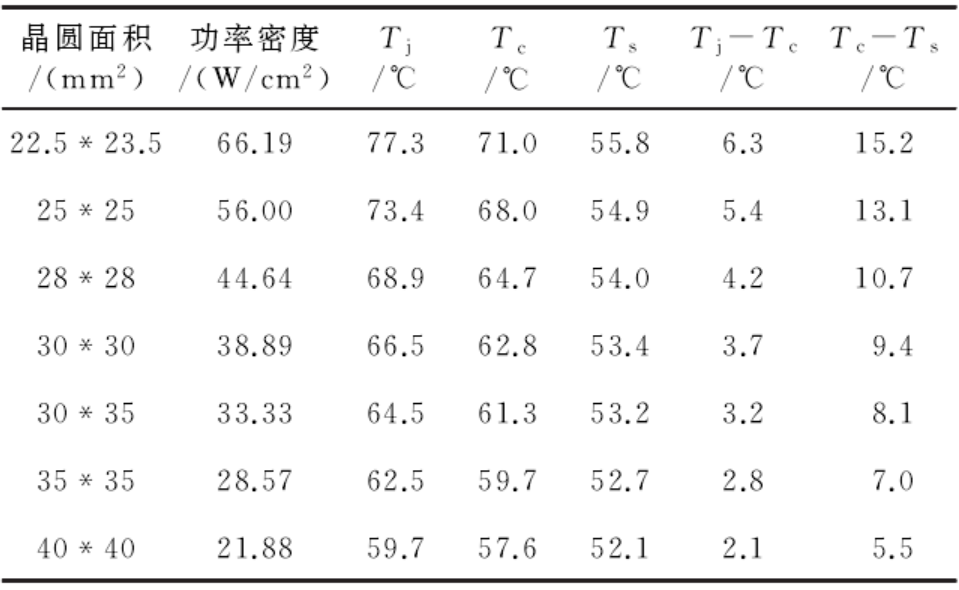

功率密度是指单位面积的功率大小,单位为 W/cm2。本节通过控制 CPU 总功率不变,改变晶圆的尺寸(面积),以此改变功率密度,再分别计算不同功率密度下CPU的散热情况。表5为仿真条件。表6 为不同功率密度/晶圆面积下,CPU 结温、CPU 壳温、散热器温度、结壳温差和 TIM1接触温差的计算结果。

表5 晶圆功率密度仿真条件

表6 不同晶圆面积/功率密度下仿真计算结果

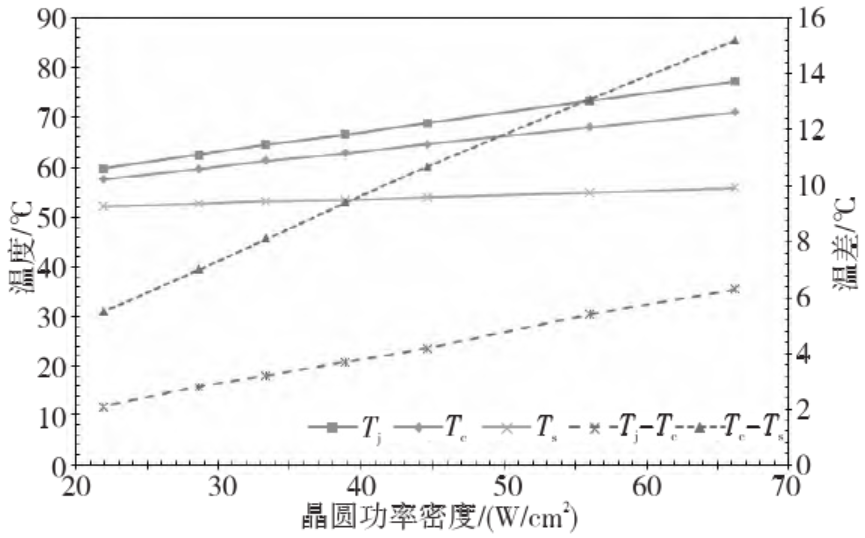

图8为晶圆功率密度和温度之间的关系曲线。

图8 晶圆功率密度与CPU结温的关系曲线

从图8可以看出:

(1)Die的面积越大,CPU 晶圆功率密度越小,CPU结温、壳温、散热器温度越低;

(2)Die的面积越大,CPU结壳温差越小,即CPU结壳热阻越小;

(3)Die的面积越大,CPU 外壳到散热器之间的温差越小;

(4)Die的面积(晶圆功率密度)对 CPU 热阻和接触热阻影响较大,Die的面积增大至40mm*40mm(功率密度为22 W/cm2左右)时,CPU 结温降低17.6℃,壳温降低13.4℃。

06结束语

(1)TIM1导热系数低于35 W/(m·K)时,导热系数的变化或者厚度变化对CPU散热影响显著;(2)TIM1导热系数超过35 W/(m·K)时,导热系数的提高对CPU散热影响较小;(3)CPU 晶圆厚度对散热影响较小,晶圆面积对散热影响显著;(4)对于功耗超过200 W 的 CPU 芯片,建议使用STIM(金属焊接封装 TIM1),或者导热系数大于35 W/(m·K)的 TIM1材料;(5)对于大功耗芯片,建议增大晶圆的设计面积,使其功率密度尽量控制在40 W/cm2以内,单个Die面积超过 30 mm*30 mm时,建议使用Chiplet多核封装;(6)建议芯片设计阶段(包括封装材料选型设计),同步进行芯片级热仿真评估,避免因芯片功率密度过大或者传导热阻过大引起的系统散热风险或散热瓶颈。

审核编辑:汤梓红

-

MUN12AD03-SEC的封装设计对散热有何影响?2025-05-19 3350

-

BGA封装对散热性能的影响2024-11-20 2471

-

实现芯片级封装的最佳热性能2024-10-15 335

-

华为公布倒装芯片封装最新专利:改善散热 CPU、GPU等都能用2023-08-17 1392

-

研究不同的模式对PCB设计热性能的影响2023-04-20 899

-

FCBGA封装的CPU散热结构设计研究2023-04-14 5480

-

Si二极管用的散热性能出色的小型封装“PMDE”评估-总结2023-02-10 1253

-

工控机为提升其散热性能都有哪些方法2022-05-17 1915

-

PCB提高中高功耗应用的散热性能2018-09-12 2270

-

LED阵列散热性能的研究2017-10-31 1200

-

LED芯片分布对散热性能的影响研究2012-10-22 5165

-

LED芯片分布对散热性能的影响2011-04-26 4456

-

电脑机箱散热性能优化问题的研究2008-12-13 707

全部0条评论

快来发表一下你的评论吧 !