基于FPGA的按键检测设计

描述

在电子产品中我们会经常用到按键,比如电脑的键盘,手机的按键等等,按键就是人机交互的一种工具。 本文使用 FPGA 程序来检测与按键对应的 I/O口的电平高低来判断按键是否按下或松开,通过点亮/点灭开发板上相应的 LED 灯来指示按键的动作。

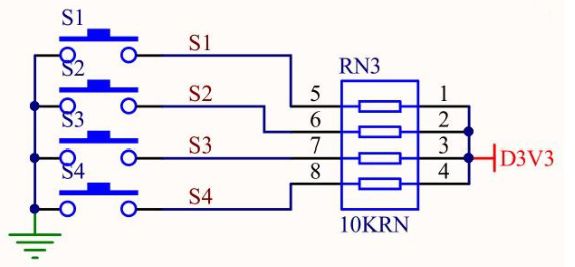

按键原理图

从原理图可知:当按键按下时,FPGA 的 I/O 口检测到低电平; 当按键弹起时,FPGA 的 I/O口检测到高电平。

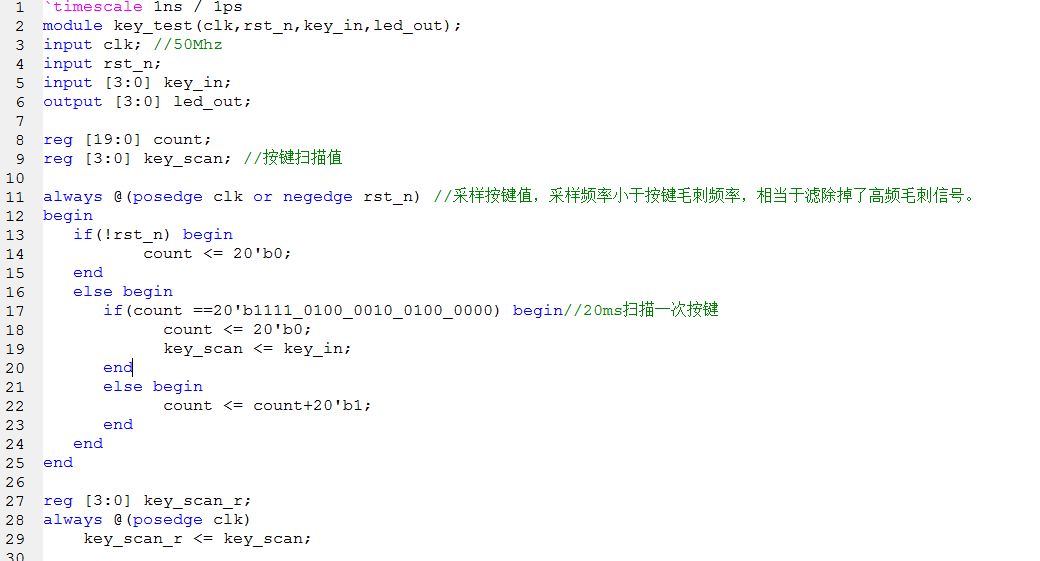

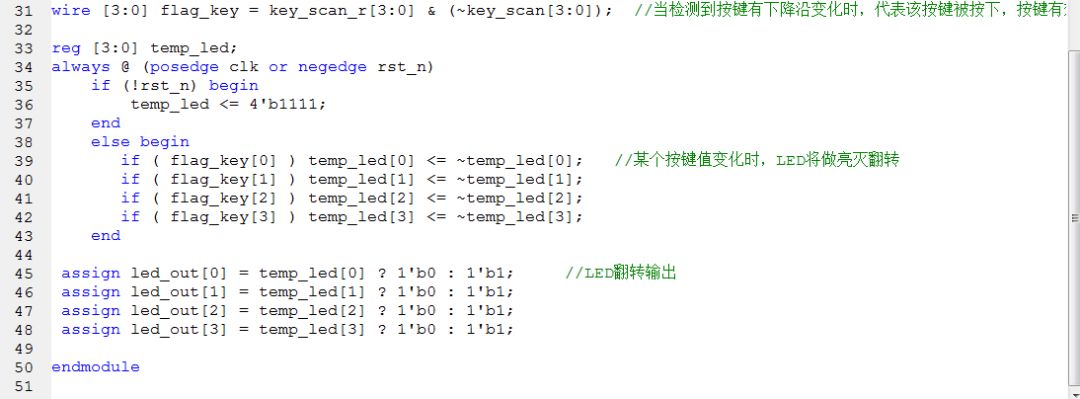

注意点:每 20ms 程序会检查一下按键的状,如果这次检测为低电平而且上次检测为高电平的话,说明有按键按下,相对应的 LED 灯反转。 一般按键按下时的按键抖动为低于 20ms 的脉冲信号,这些高频脉冲信号会被滤除。 提高了按键的可靠性。

用verilog实现:

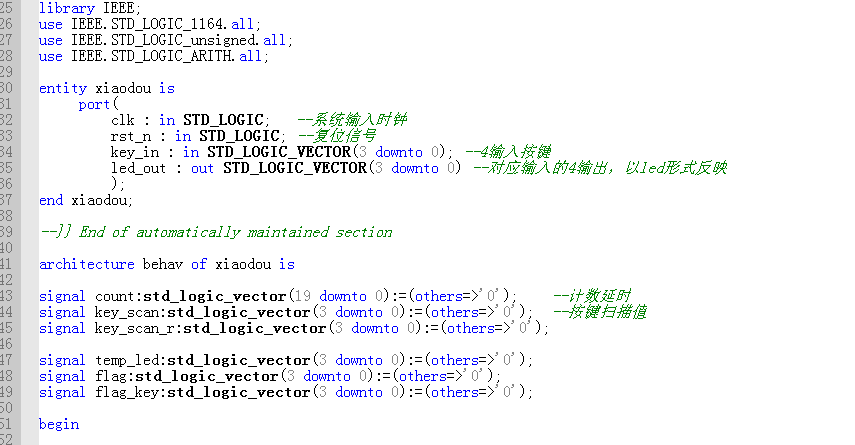

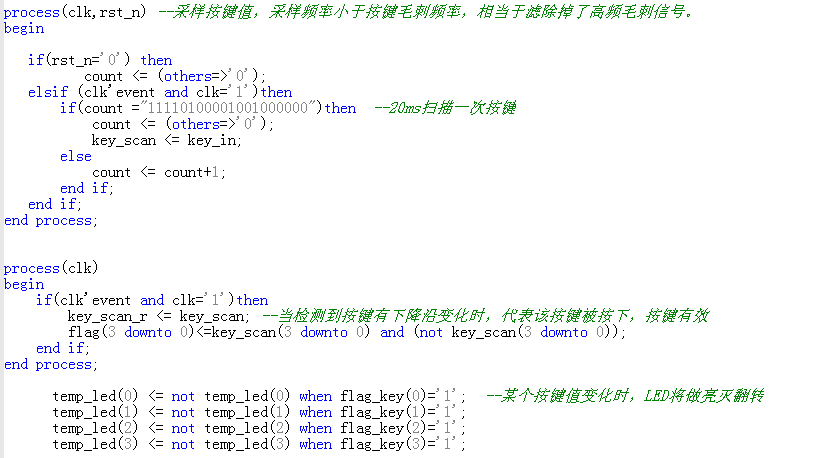

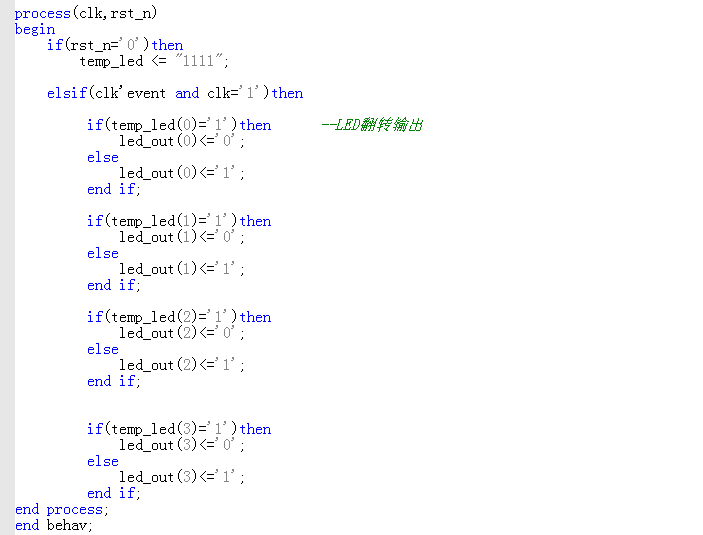

用VHDL实现

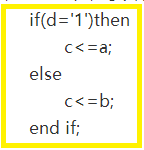

特别地:Verilog中的条件操作符号“?”,比如 assign c=d?a:b; 它的意思就是,当d=1时,把a的值赋给c,否则,把b的值赋给c。 实际在VHDL中,可以用一个if-else语句来实现同样的说法。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

远心镜头应用手机按键检测2025-01-20 996

-

基于FPGA实现按键消抖处理2024-10-24 2174

-

如何在FPGA中实现按键消抖2024-08-19 4893

-

STM32速成笔记(3)—按键检测2023-10-23 4885

-

51汇编(七):按键检测2021-11-22 1397

-

PIC单片机 按键检测识别2021-11-16 1092

-

【紫光同创国产FPGA教程】【第三章】按键检测实验2021-02-02 5239

-

【ZYNQ Ultrascale+ MPSOC FPGA教程】第九章Vivado下按键实验2021-01-22 3128

-

基于FPGA按键模式的分类和如何实现应用设计2020-07-20 2999

-

梅哥和你一起深入学习FPGA之独立按键检测(下)2018-09-26 715

-

深入而全面:FPGA学习之独立按键检测2014-12-11 13349

-

小梅哥和你一起深入学习FPGA之独立按键检测2014-11-10 11117

-

fpga教程之——按键消抖2012-02-27 22714

全部0条评论

快来发表一下你的评论吧 !