传统封装技术与先进封装技术的优劣势

制造/封装

描述

随着摩尔定律不断逼近物理极限,为获得更高性能兼具成本效益的芯片,越来越多企业开始采用chiplet架构设计,并通过先进封装技术实现芯粒的整合。作为一条全新的赛道,Chiplet架构与先进封装技术的结合,在通往成本、性能、量产时间三赢终点的同时,也引发了前所未有的挑战。如何应对这些挑战,将成为高性能企业转型chiplet之路顺利与否的关键。 在这样的背景下,2022年11月23日,奇异摩尔先进封装专家徐健应CEIA电子智造平台邀约,以《算力时代先进封装技术的机遇及挑战》为主题与CEIA观众进行了一次深入探讨,我们对演讲内容进行了整理:

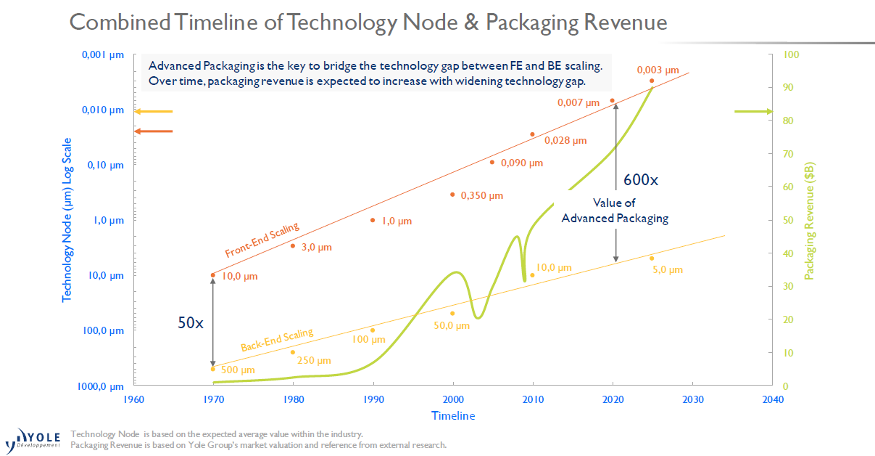

Souce: Yole 20世纪60年代以来,随着半导体芯片工艺的不断发展,全球最先进的制程能力已达到3nm级别,印刷电路板(PCB)的支撑能力也得到了显著的提升。然而,与芯片相比,PCB的追赶如同一场龟兔赛跑,今天二者间的线宽、线距相差近600倍。这一差距在大数据和AI应用兴起的背景下,还将继续扩大。为更好地适应代差,先进封装技术被引入并得到了发扬光大。

先进封装升维:2D-3D

封装作为一种将芯片和外部世界连接起来的技术,可被比作PCB与芯片间的桥梁。从制程代差的层面来说,封装的目标是解决芯片与PCB之间制程不匹配的难题。在芯片制程突飞猛进向3nm甚至1nm狂飙时,如何把被远远的甩在后面的PCB的硅信号直接导到PCB正面,也就成了封装的职责与挑战所在。 从全球封测技术发展路径来看,我们正在经历从传统封装向先进封装的演变。与传统封装技术相比,先进封装具有小型化、轻薄化、高密度、低功耗和功能融合等优点。相比SoC,先进封装可以显著提高封装密度,从FAN-IN、FC、BGA BUMPING、FANOUT、TSV、Hybrid Bonding到异构集成,其背后的原理都从封装层面去适应芯片所需的密度,从而是带动整个封装密度和互连密度的提升。

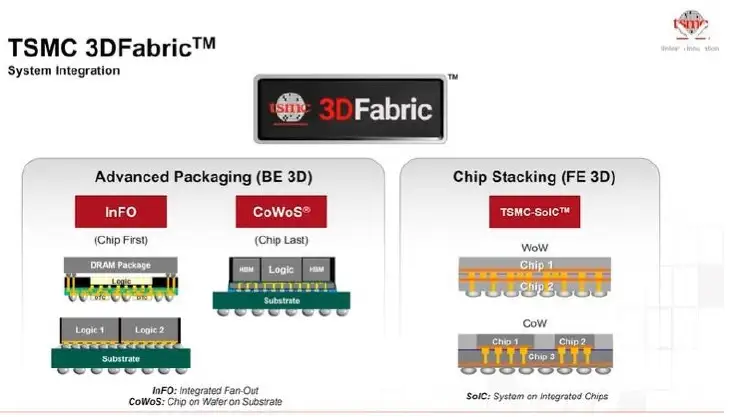

传统的2D封装,是把所有的芯片直接放在基板上,其I/O的数量受限于PCB和substrate的物理支撑能力,即使采用SAP工艺,线宽/线距也难以达到10微米以下。2.5D封装在2D封装的基础上更进一步,在芯片下添加了一层硅基基板,通过substrate引出信号。3D封装则是在顶层芯片下方添加die,基于organic substrate或silicon interposer支撑其他芯片,上层信号可以独立操作,辅助功能连接在下层芯片上,以实现上下层间信号间的互连,其优势也最为显著。

传统封装技术与先进封装技术的优劣势

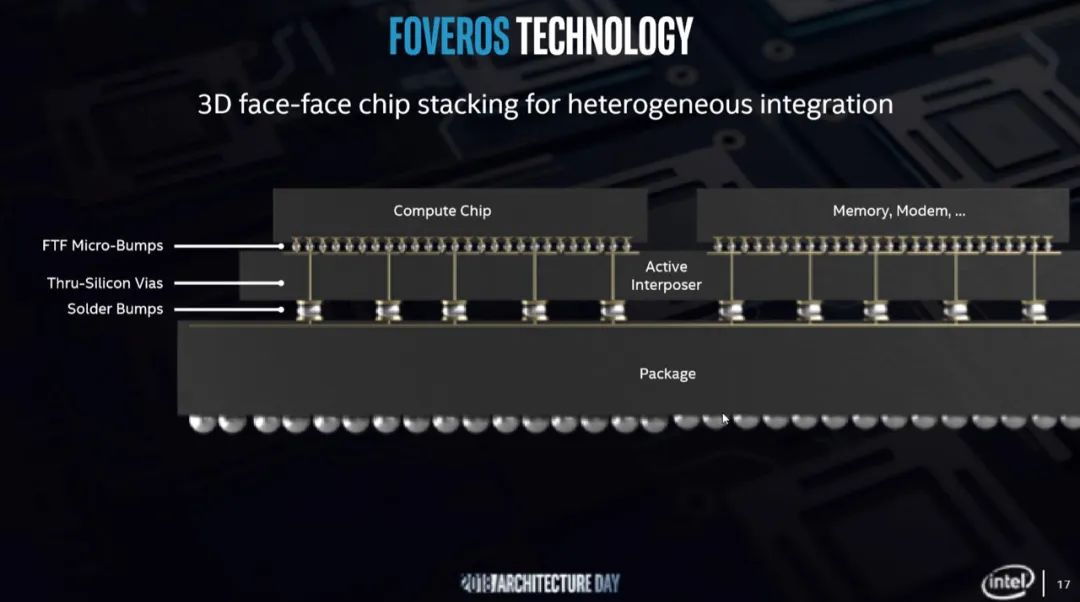

全球巨头公司都开始积极布局先进封装。代表技术方面,英特尔的2.5D技术EMIB可对标台积电的CoWoS,英特尔的3D技术Foveros则对标台积电的InFO、三星电子的Fan-Out。封装技术的演进为芯片功能升级打下了基础,也是芯片发展的重要趋势之一。

Intel Foveros: 3D die stacking

Chiplet 技术与优势分析

随着算力需求的飙升和算法的多样化发展,许多问题也接踵而来,其中包括算力功耗比的放缓、存储墙的出现、研发成本和周期成本的不断增加以及量产成本的持续上升。为解决这些挑战,有几种方法可供考虑:

同构扩展:芯片良率与单芯片的面积息息相关,将一颗较大的芯片拆分成多个小面积的芯粒,再封装为一颗大芯片,较传统的SoC更具成本效益。举例来说,150㎜²的芯片单颗芯片良率约80%,但如果芯片面积增加到700㎜²,单芯片良率就会骤降至30%。异构计算:传统芯片将多种不同的功能模块集成在同一芯片上,可能会出现相互干扰的问题,从而影响整体性能。而异构计算则是将一个大型芯片分解为多个芯粒,每个芯粒都专门设计用于执行不同的任务,并可以单独封装。通过这种方式,不同芯粒的特定设计和优化可以显著提高整体芯片的性能和效率。异构集成:通过将不同的功能模块化拆分,可以实现使用不同的工艺流程、架构和技术的异构组合,从而优化系统的整体性能,使其更加高效和灵活,更好地发挥整个系统的作用。

Chiplet优势

1、通过SIP(System in Package)技术,各个芯粒可以独立设计并统一组装,从而提高复用性。此外,不同芯片之间可以相互补充,实现更丰富的功能。

2、模块间相互独立,可降低芯片面积并提高良率。另外,模块化设计有助于提高可重用性、降低设计复杂度和提高设计准确性。

3、系统模块化,可大幅度降低研发成本和周期。不同部分可以同时开发,缩短整个研发时间。

4、支持混合工艺集成,不同模块可依据实际需求选择工艺节点,降低制造成本。

5、Chiplet封装突破了光照尺寸的限制,增加系统集成度。不同芯片可以组装在一起,实现更复杂的功能。

6、通过异质异构集成,不同种类的芯粒可以相互补充,提高系统性能。

7、通过芯片堆叠缩短传输路径,提高带宽,从而增加整体性能。

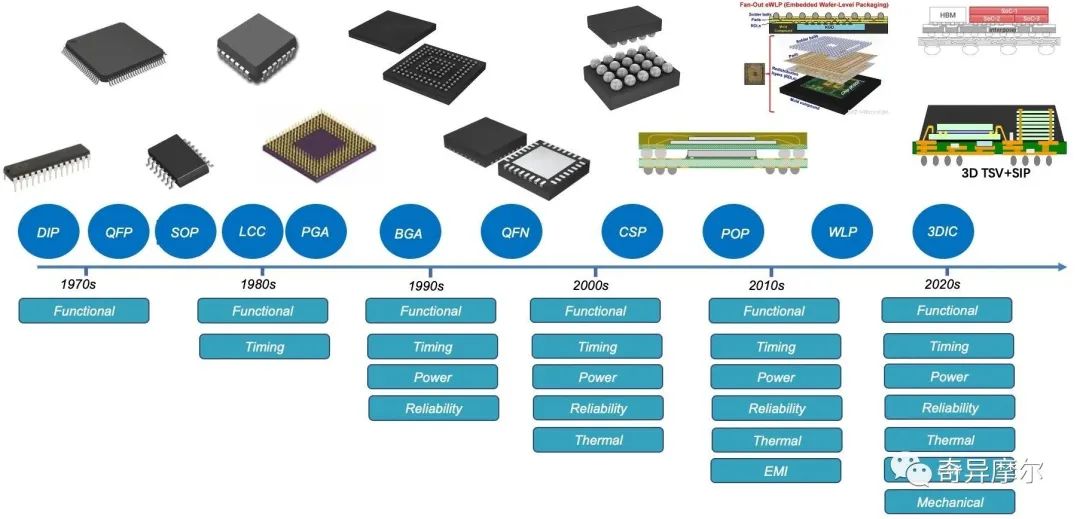

封装设计发展

1970年以来,集成电路封装经历了技术的数次迭代,包括Dual in-line package(DIP)、Quad Flat Package(QFP)、Small Out-Line Package(SOP)、Leadless Chip Carriers(LCC)、Pin Grid Array Package(PGA)等多种封装类型的发展。随着时间推移,行业的技术关注点也发生了变化。在基板和PCB时期,行业主要关注功率和可靠性方面的挑战。到了CS和POP时期,行业开始聚焦底层热问题,并引入了新型封装技术,如Fanout和wafer level CSP。自2020年以来,3D Chiplet封装技术引发热潮后,芯片堆叠也引发了对化学和EMI等领域的探讨。

Chiplet 封装工艺

当时间推移到3D chiplet封装技术时期,封装设计的侧重点已与传统封装有了相当大的不同。在3D chiplet芯片中,为实现更高的性能和密度,通常需要重点考虑几大因素:设计、供应链、热问题、模流、电信号和机械可靠性。

封装设计:虽然封装属于芯片制造的后续工序,但封装的设计往往会直接影响芯片性能、功耗、可靠性和成本。因此,封装方案需作为整个框架结构中的重要环节优先考虑,与整个工艺流程密切配合。

供应链:作为一个新兴领域,Chiplet供应链尚不成熟,如何选择合适的供应商,关乎芯片品质。供应商的技术能力、管理水平、成本控制能力、交货时间、服务水平以及行业口碑信誉都应当纳入考量、评价体系。

热力问题:3D chiplet设计中,多层结构会导致下层芯片散热题。常见的解决方案是使用散热盖来增强芯片的散热效果,或采用风冷或水冷等主动散热。

膜流问题:在2.5D或3D封装中,由于micro bump的尺寸和高度极小,下层interposer与上层的Top die之间可能只有一条缝隙,underfill有一定几率在这个狭窄的空间中形成膜流,导致填充不均匀或者甚至无法填充,确保这条缝隙中填充满足够的underfill将成为很大的挑战。

电信号问题:TDR(时域反射)、PI(功率完整性)、PDN(电源完整性)和EMI(电磁干扰)等电信号问题同样是2.5D或3D封装需要关注的核心问题之一。这些问题与信号完整性和电源完整性有关,需要通过封装版图设计来满足所需的要求。

机械可靠性:在2.5D或3D封装中,上层芯片通常会叠加多颗芯片,当芯片之间存在应力集中时,可能会导致芯片的应力超过其承受范围,引发芯片的破裂和故障。因此,在封装设计中需要通过优化芯粒布局、使用合适的材料、加强封装结构等方式来提高机械可靠性,以确保芯片和封装的长期可靠性和性能。

算力时代的封装设计方案

事实上,Chiplet封装设计并非完全依赖先进封装。为了确保封装的质量和可靠性,需要传统封装和先进封装技术的结合和多种因素的综合考量,以找到最优解方案。以传统的Wafer-Bump设计为例,Chiplet封装同样需要全面考虑工艺的最前端、芯片流片过程以及最终的封装测试和可靠性等因素,以确保封装质量和可靠性。弧长、弧高、线材、线径以及分割和距离等因素都需要进行详细分析和研究。

当然,由于Chiplet具有更高的集成度和更小的封装尺寸,需要更高级的封装技术来实现更高的性能和更小的封装尺寸。封装质量和可靠性的保障需要更多细节和更高级的技术参与,以适应算力时代对芯片性能无止境的追寻。

随着算力应用场景的不断扩张,先进工艺和封装技术的不断演进,Chiplet封装正成为未来芯片设计和封装的趋势。国际大厂,特别是在先进制程工艺方面处于行业领先地位的厂商,都开始在最先进封装领域投下重注,以求在先进制程和先进封装融合方面形成护城河。

作为一条新兴赛道,Chiplet封装领域生机勃勃,也并存着诸多挑战。对于受限于先进工艺高生产成本、设计难度、生产限制的企业而言,如何通过Chiplet设计和封装,提高自身产品竞争力,将在很长的一段时间成为重要课题。

奇异摩尔作为全球首批专注于2.5D及3DIC Chiplet产品及服务的公司,在Chiplet生产和测试方面有着丰富的实践经验,同时拥有多样化的产业资源,可提供世界领先水平的先进封装设计、小规模打样测试和其他服务,以尽可能低的成本助下一代数据中心、自动驾驶、下一代个人计算平台等领域客户解决 Chiplet领域中最棘手的挑战。

编辑:黄飞

-

DC/DC 与 AC/DC:技术原理、应用场景及优劣势全解析2025-11-14 618

-

晶圆级封装技术的概念和优劣势2025-05-08 2011

-

Prolith和HyperLith的优劣势2024-11-29 9483

-

电流检测采用高端检测和低端检测有什么区别?有什么优劣势?2024-08-16 2692

-

STM32WB和STM32L4/L4+的区别和优劣势是什么?2024-04-26 649

-

RC modeling的优劣势2023-06-19 1802

-

SPI协议的特性是什么?具有哪些优劣势?2022-02-17 1651

-

异步电路原理是什么?有哪些优劣势?2021-06-21 3210

-

请问工业机器人有什么优劣势?2021-06-18 7845

-

路由器的2.4GHz频段和5GHz频段各有什么优劣势?2021-06-17 5074

-

cob封装的优劣势2019-05-07 8907

-

六种室内定位技术的优劣势分析2018-05-04 28514

-

四大存储方式技术解析其优劣势2017-01-22 902

-

你如何看待LoRa技术的优劣势?2016-12-12 12428

全部0条评论

快来发表一下你的评论吧 !