MOSFET的结构和阈值电压

模拟技术

描述

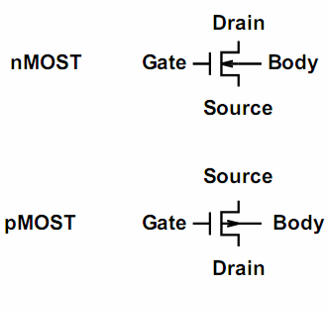

首先我们先了解什么是MOSFET?全称是金属氧化物半导体场效应管(Metal-Oxide-Semiconductor Field Effect Transistor)这是MOSFET的简易符号,表示了三个端子:栅(G)、源(S)和漏(D)。 因为这种器件是对称的,因而可以源漏互换。 大家都知道,在数字电路中,MOS管作为开关的作用时,栅极电压VG是高电平,晶体管把源极和漏极连接在一起; 如果VG是低电平,则源漏断开。

但是,这是数字电路需要研究的内容,在模拟电路中,知道这些还远远不够。 我们还是要回答几个问题:VG取多大的时候器件导通?

阈值电压是多少?

当器件导通(断开)的时候,源漏之间的电阻值是多大?

这个电阻和VDS之间的关系是怎样的?

哪些因素可以限制器件的速度?

这些问题小编会在以后给大家解答。

MOSFET的结构

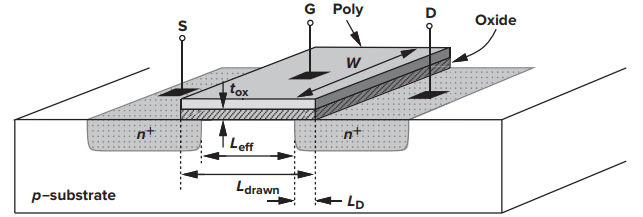

图为NMOS器件的简易结构,器件制作在P型衬底上两个重掺杂的n区形成源极和漏极。 重掺杂的多晶硅区(简称Poly)作为栅极。 一层氧化膜(Oxide)使栅和衬底分离。 Leff称为有效栅长,Ldrawn称为总长度。 LD是横向扩散长度。 tox为氧化层的厚度。 Leff(有效栅长)和tox(氧化层厚度)对MOS电路的性能起着十分重要的作用。

MOS的符号

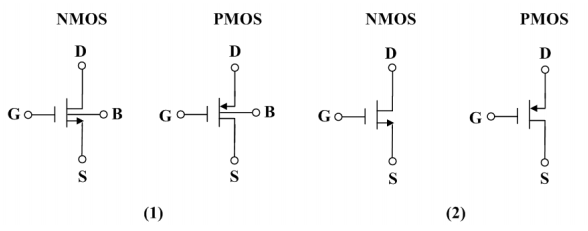

NMOS管和PMOS管的电路符号所示,MOSFET是一个四端器件,衬底是第四端,用B表示。 由于在大多数电路中NMOS管和PMOS管的衬底分别接地和VDD。 所以我们在画MOS管的符号时,经常省略这一连接。

阈值电压

当栅极电压VG从0开始上升时会发生什么情况呢?

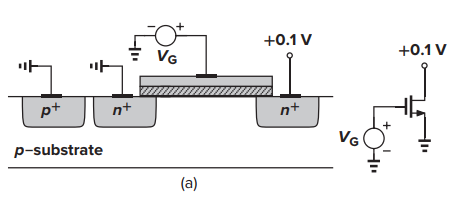

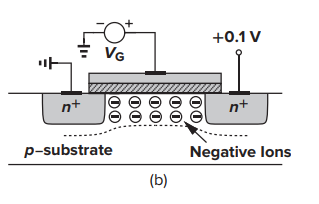

图(a)所示的是一个NMOS器件,衬底接地。 当VGS等于0时; 两个有源区被衬底分离,所以源漏之间没有电流流动。 当VG逐渐升高时,在栅极和衬底之间的SiO2 绝缘层中产生了从栅极指向衬底的垂直电场EV。 在该电场作用下,衬底中的电子受到吸引,向衬底表面运动; 而衬底中的空穴受到排斥,向衬底内部运动。 向上运动的电子与表面的空穴复合,在表面层留下了不能移动的负离子,形成了一层耗尽层。 在这种情况下,没有电流流动。 如图(b)。

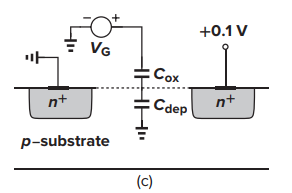

随着VGS的升高,电场EV越来越强,表面层吸引的电子越来越多,产生的负离子也越来越多,耗尽层也越来越厚。 这样的结构类似两个电容串联构成的分压器,栅氧化层电容和耗尽层电容。 如图(c)。

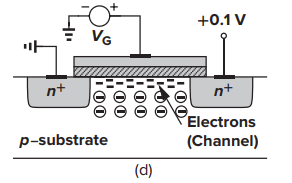

当VGS 上升到一定电位时,靠近表面的 P 型衬底发生变化,“反型”为与 N型材料类似的特性,因此该层称为反型层。 反型层将漏极和源极两个有源区连通,构成了源漏之间的导电沟道。 使晶体管产生反型层所需的VGS电压称为阈值电压或开启电压,用Vth表示。

在器件制造过程中通常向沟道区注入杂质来调整阈值电压,其实质是改变氧化层界面附近衬底的掺杂浓度。

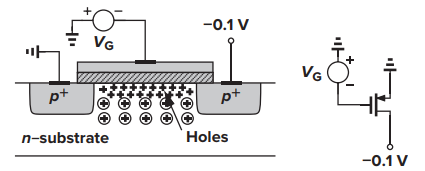

PMOS器件的导通现象类似于NFETs,但是其所有的极性都是相反的。 如图,如果栅源电压足够”负“,在氧化层-硅的界面上就会形成一个由空穴组成的反型层,从而为源和漏之间提供了一个导电沟道。 因此,PMOS的阈值电压通常是负值。

下期为大家介绍I-V特性和MOSFET的跨导。

-

MOSFET栅极阈值电压Vth2025-12-16 35

-

基于JEDEC JEP183A标准的SiC MOSFET阈值电压精确测量方法2025-11-08 7011

-

合科泰MOSFET阈值电压选型策略2025-10-29 691

-

MOS管的阈值电压是什么2024-10-29 7648

-

MOSFET阈值电压是什么?影响MOSFET阈值电压的因素有哪些?2024-07-23 24813

-

浅谈影响MOSFET阈值电压的因素2024-05-30 6698

-

什么是MOS管亚阈值电压?MOSFET中的阈值电压是如何产生的?2024-03-27 7005

-

影响MOSFET阈值电压的因素2023-09-17 16555

-

碳化硅的阈值电压稳定性2023-05-30 4076

-

EDA探索之控制阈值电压2023-02-09 2413

-

MOS管阈值电压与沟长和沟宽的关系2019-06-18 40666

-

MOSFET的重要特性–栅极阈值电压2019-05-02 17459

-

解答74HC14中正向阈值电压和负向阈值电压是什么/电压为多少2018-10-24 19553

-

阈值电压的计算2017-11-27 74918

全部0条评论

快来发表一下你的评论吧 !