MOSFET的动态性能相关参数

描述

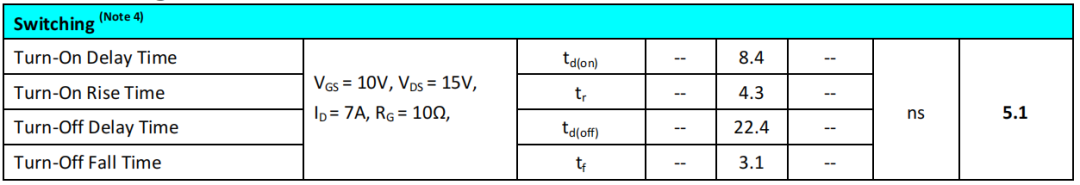

本篇是读懂MOSFET datasheet系列最终篇,主要介绍MOSFET动态性能相关的参数。 主要包括Qg、MOSFET的电容、开关时间等。 参数列表如下所示

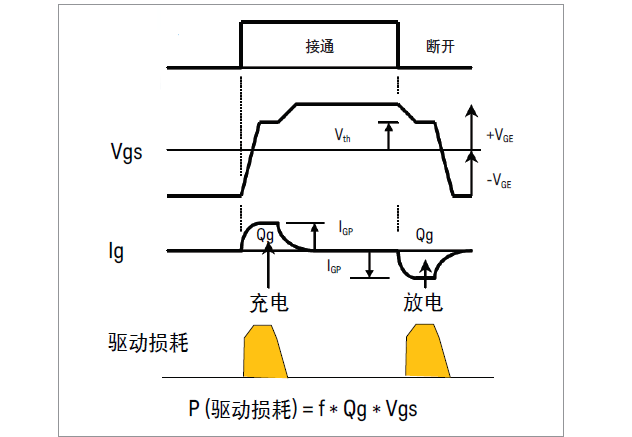

1、栅极电荷 ( Qg )

栅极电荷是指为导通MOSFET而注入到栅极电极的电荷量,有时也称为总栅极电荷。 总栅极电荷包括 Qgs 和 Qgd。 Q gs表示栅极-源的电荷量,Qgd 表示栅极-漏极的电荷量,也称米勒电荷量。

单位为库伦(C),总栅极电荷量越大,则导通MOSFET所需的电容充电时间变长,开关损耗增加。 数值越小,开关损耗就越小,从而实现高速开关。 换言之,栅极电荷也可以表示为器件转换为导通状态时电流进入选通端接的时间积分,此时开关损耗等于栅极电荷、栅电压和频率的乘积。

通常,MOSFET的芯片尺寸(表面积)越小,总电荷量就越小,但是导通电阻会变大,因此开关损耗与工作时的损耗之间存在一个平衡关系。

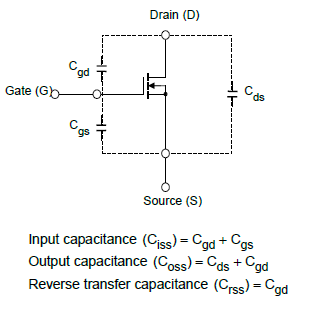

2、电容(Ciss, Coss, Crss)

Ciss, Coss, 和 Crss,跟栅极电荷一样影响着开关性能。 MOSFET 作动的过程,就是栅极电压对源极、漏极电容充放电的过程。

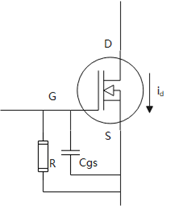

Cgs:栅极和源极之间的等效电容。 实际上控制电压输出后,就开始给电容Cgs开始充电,GS电容充电过程分三个阶段:

①上电瞬间电容等效成短路,GS电容的内阻为0,几乎所有的电流,都从电容上走;

②GS电容没有充满的情况下,电流分别从电阻及电容流过,但主要的电流依旧从电容走;

③ 电容充满了,电流不从电容走,只有很小的电流从电阻走。

Cgd:栅极和漏极之间的等效电容。 这个电容也称为米勒电容,臭名昭著的“米勒效应”也因此产生。 米勒效应,实际上是有一个固有的转移特性:栅极的电压Vgs和漏极的电流Id保持一个比例关系。

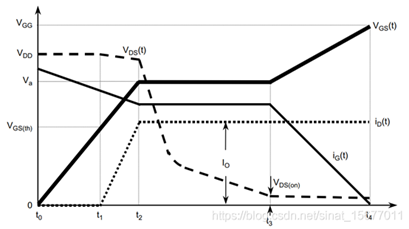

产生的问题:因为米勒电容的影响,造成mos管不能很快的进行开通和关断,中间有一段延迟时间。 通过示波器测量VGS电压波形,会发现VGS波形在上升期间有一段平台,这个平台又称为米勒平台。 (下图加粗线表示)

米勒平台大家首先想到的麻烦就是米勒振荡。 (即,栅极先给Cgs充电,到达一定平台后再给Cgd充电)因为这个时候源级和漏级间电压迅速变化,内部电容相应迅速充放电,这些电流脉冲会导致mos寄生电感产生很大感抗,这里面就有电容,电感,电阻组成震荡电路,造成MOS误导通、烧毁等问题。

产生问题的原因:

通过上图我们分析,在t0-t1这段时间内,VGS一开始随着栅极电荷的增加而增加,开始给Cgs充电,当电容达到门槛电压后,VGS=VGSth后,MOS开始进入导通状态。

在t1-t2这段时间内,MOS开始导通,此时的id就已经开始有电流,但是电流很小。 此时的D极电压比G极电压高,电容Cgd是上正下负。

然后Vgs电压继续上升,Id也会继续上升,当上升到米勒平台电压Va的时候,就会发生固有转移特性(Vgs不变,id也保持不变)。

在t2-t3这段时间内,虽然栅极电荷继续增加,但是栅极电荷也有了另外一条通路(下图紫色标注通路),栅极电荷这个时间大部分用来给电容Cgd进行充电,导致VGS电压不在增加。 此时的Cgd极性与漏极充电相反,即下正上负,因此也可理解为对Cgd反向放电,最终使得Vgd电压由负变正,结束米勒平台进入可变电阻区。 米勒平台时间内,Vds开始下降,米勒平台的持续时间即为Vds电压从最大值下降到最小值的时间。

通过上图我们可以分析在米勒平台的这段时间内,VGS 和id都是保持不变的,VDS从最大值降到了最小值。 所以刚进入米勒平台时,在MOS管上产生的导通损耗非常的大。 我们假设VDS电压从12V减低到了0.5V,id=10A保持不变,可以计算导通功耗也从 120W变为5W,这个功率的变化时很大的,如果开通时间慢,意味着发热从120w到5w过渡的慢,mos结温会升高的厉害。 所以开关越慢,结温越高,容易烧mos。

Cds电容:源极和漏极之间的等效电容。

3、栅极电阻 (Rg)

Rg 是被设计在芯片栅极区域里,在 MOSFET 嵌入 Rg 下,栅极驱动电路可以简化设计。

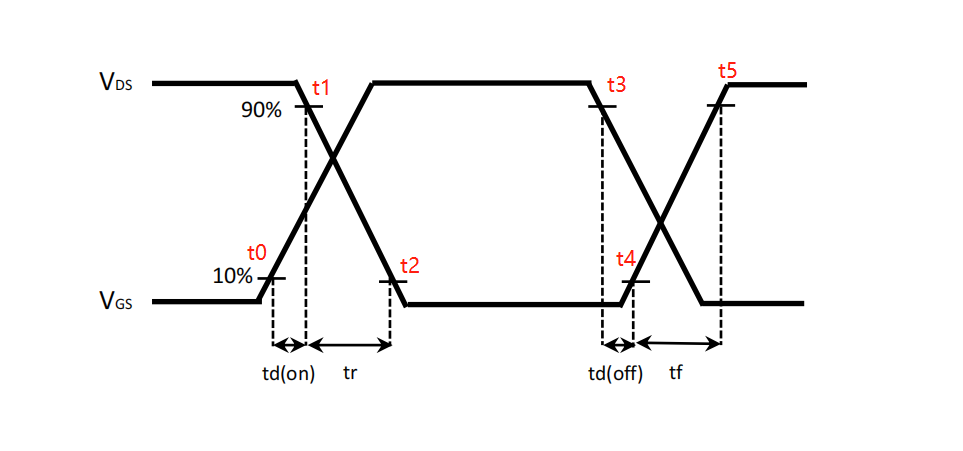

4、开关时间

MOSFET的开通时间ton由开通延迟时间td(on)和上升时间tr组成,关断时间toff由关断延迟时间td(off)和下降时间tf组成。

4、1 td(on) –导通延迟时间

td(on)是指从 VGS 输入电压升到 10% 到 VDS下降到 90% 两点之间的时间。 t0-t1时刻,驱动电平置高,打算开通MOSFET,但是由于栅极等效电容的存在,栅极电压VGS缓慢上升,由于VGS尚未达到VGS(th),所以MOSFET尚未开通,这段时间代表从开始“开通”到“开通开始生效”的延迟。

4、2 tr –导通上升时间

tr是指 VDS 从 90%下降到 VDS 的 10% 两点之间的时间。

t1时刻,VGS电压达到开通门限,MOSFET开始导通,由于漏源之间的等效电容,从t1时刻开始,VD逐渐降低,ID逐渐增大。 t2时刻,VD达到最低,ID增至最大,MOSFET完成开通过程。

实际上,在tr时间段内,VGS电压会因为“米勒平台”维持不变,在t2时刻以后,VGS电压逐渐上升到驱动电压的最大值。

这段时间称为上升时间,代表了ID电流上升到最大所需要的时间。

4、3 td(off) –关断延迟时间

td(off)是指 VGS 下降到 90% 到 VDS 上升到其关断电压的 10% 两点之间的时间。 t3-t4时刻,驱动电平置低,打算关断MOSFET。 同样由于栅极等效电容的存在,VGS只能缓慢降低,在VGS尚未降低到门限电压之前,MOSFET的导通状态不会有变化,这段时间代表开始“关断”到“关断开始生效”的延迟。

4、4 tf – 关断下降时间

tf是指 VDS 从 10%上升 到其关断电压的 90% 两点之间的时间。 在t4时刻,VGS电压降低到门限电压,MOSFET关断,t5时刻,VD达到最高,ID减小至最低,MOSFET完成关断过程。

这段时间称为下降时间,代表了ID电流下降到最低所需要的时间。

-

MOSFET相关问题分享2026-01-26 282

-

SiC MOSFET模块并联应用中的动态均流问题2025-05-30 2844

-

麦科信光隔离探头在碳化硅(SiC)MOSFET动态测试中的应用2025-04-08 1244

-

电力场效应管的动态特性和主要参数2024-09-13 3622

-

怎么提高SIC MOSFET的动态响应?2023-12-21 1609

-

闪烁噪声会影响MOSFET的哪些性能2023-09-01 1058

-

介绍MOSFET动态性能相关的参数2023-05-29 11093

-

MOSFET的热阻相关参数2023-04-26 5874

-

功率器件动态参数测试系统2023-02-16 880

-

MOSFET有哪些参数2021-03-04 3811

-

选择合适的晶体管:了解低频MOSFET参数2019-10-25 2643

-

MOSFET数据表的开关参数2018-09-05 1993

-

MOSFET动态输出电容特性分析2014-10-08 12299

全部0条评论

快来发表一下你的评论吧 !