仿真时为什么顶层不例化

电子说

描述

不管是基于什么方法学Verilog或者SystemVerilog编写测试平台,进行仿真的时候都需要将设计代码例化在顶层模块(module)中,然后将顶层名指定在仿真命令中,但是从来没有把顶层进行例化。因为可能会想如果顶层再例化就需要把顶层再例化到另一个module中,然后将这个module的名字再作为新的顶层。。。这样下去就没有穷尽了。其实在Verilog和SystemVerilog中,module的例化一般要么是在设计层次结构中被例化,以形成整个层次化的设计,要么就是作为整个仿真环境的顶层module出现进行例化,并且此时给大家的假象是没有例化。其中第一种例化方式就是“显式例化”,后一种顶层module实际上是以一种“隐式例化”的方式存在的,那么“隐式例化”和“显式例化”都有哪些特点和使用上的区别呢?本文将示例说明。

1 隐式例化

隐式例化常见的情况主要出现在顶层模块在仿真时,顶层模块会被隐式的进行一次例化,并且这个例化名与顶层module的名字,这样的一个实例称之为“顶层实例”,即顶层的“隐式例化”

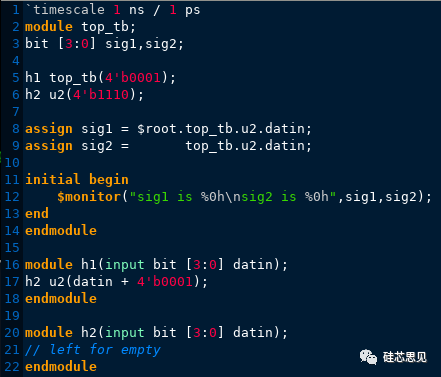

【示例】

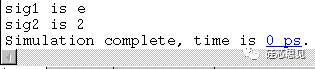

【仿真结果】

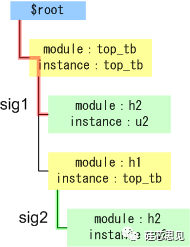

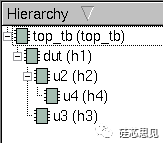

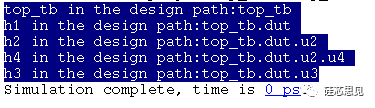

示例中,在顶层top_tb中例化了两个module(h1和h2),例化名分别是top_tb和u2,其中h1中又例化了h2,也就是h2在顶层top_tb和h1中分别进行了例化,在例化时分别传递了对应的参数。其中h1和h2在各层次的例化属于“显式例化”,整个代码的层次结构如下图所示。

示例中第8行通过层次化引用将u2中的datin的值传递给了顶层变量sig1,sig1的值来自于通过$root指向顶层例化名(top_tb,此时的top_tb就是顶层模块top_tb的“隐式例化”名),在通过顶层top_tb引用其中u2(h2例化),从而实现了对于u2中datin的访问,因为此时datin的值来自于h2在顶层中例化时传递的参数“4’h1110”,所以此时sig1值为“4’h1110”;

示例中第9行,依然是通过层次化引用的方式将u2中的datin的值传递给了顶层变量sig2,但是此时需要注意的是这里的top_tb并不是顶层module名也不是顶层module的例化名,而是当前作用域内h1的例化名(top_tb),这里h1在顶层例化时传入的参数为“4’h0001”该参数通过h1中h2例化的u2传递给了datin,此时datin的值为“4’h0010”,所以此时sig2获得数值为“4’h0010”;

2显式例化

除了顶层以外,其他模块的使用都是建立在对应module“显式例化”的基础之上,正是通过模块之间的一次或者多次例化形成了层次化的设计。

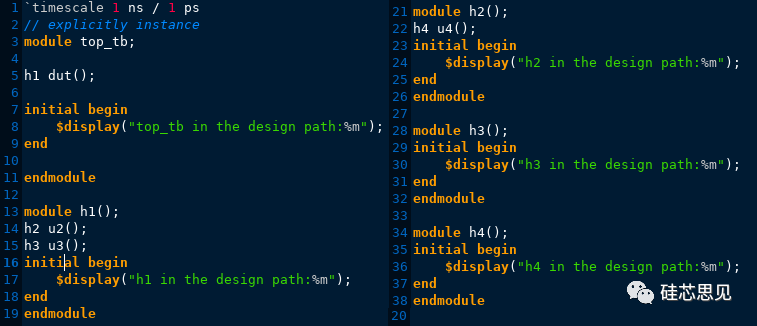

【示例】

【仿真结果】

示例仿真结果可以看到,h1、h2、h3、h4分别在不同的模块中进行了例化,形成了层次化的结构,这几个模块的例化都属于“显式例化”。

通过上述示例,在IEEE1800目前版本的SystemVerilog中“隐式例化”主要是指顶层模块的例化,不需要指明实例名,其实例名与模块名相同,“显式例化”则需要指明模块名和实例名,主要用于模块之间形成层次化结构时各模块之间的相互实例化。

审核编辑 :李倩

-

代码和原理图设计的顶层文件有什么不同么2016-07-30 7796

-

使用user design文件夹下的.v文件,如果编写顶层读写控制程序对mig-39-2.v进行例化,如何操作才能使用sim_tb_top.v仿真文件?2018-06-22 3149

-

matlab 电机仿真精华50例2018-09-07 10874

-

基于linux系统的VCS使用及仿真说明2022-07-18 5666

-

MATLAB电机仿真精华50例2015-12-24 1176

-

pcb顶层和底层互换2019-04-26 17624

-

Verilog仿真激励举例2023-06-02 2458

-

XILINX FPGA IP之DDS Compiler_ip例化仿真2023-09-07 4996

-

EDA顶层丝印层怎么画2023-12-19 4053

全部0条评论

快来发表一下你的评论吧 !