倒装芯片尺寸级封装工艺流程与技术

描述

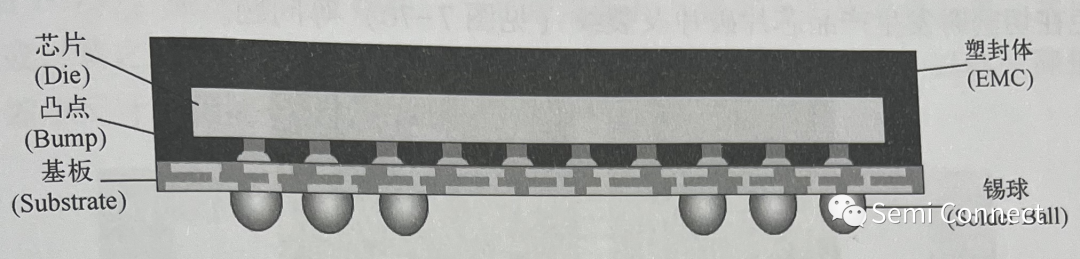

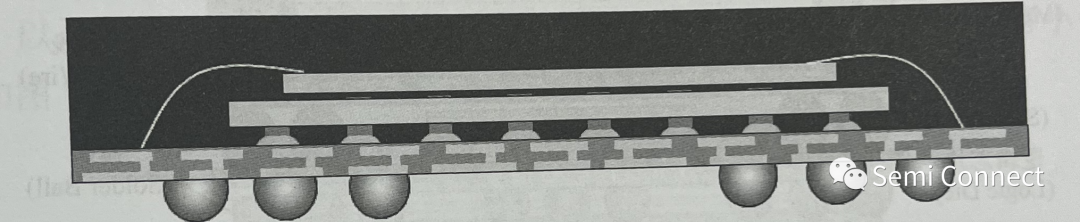

FC-CSP 是芯片级尺寸封装(CSP)形式中的一种。根据J-STD-012 标准的定义口,CSP 是指封装体尺寸不超过裸芯片 1.2倍的一种封装形式,它通过凸块与基板倒装焊方式实现芯片与基板的电气互连,且芯片面朝下,芯片焊区与基板焊区直接互连。相比于 WB 和TAB 键合方法,FC-CSP 中的半导体芯片与基板的间距更小,信号损失减小,I/O密度高,更适合大规模集成电路 (LSI)、超大规模集成电路(VLSI)和专用集成电路(ASIC)芯片使用。FC-CSP 的基本封装结构如图所示。

作为一种先进的封装技术,FC-CSP 主要具有如下技术特点。

(1)封装尺寸较小:FC-CSP 的封装面积不到 QPP (0.5mm 节距)的1/10,只有BCA 封装的 1/3~1/10;特别是运用铜杜凸块封装,可以进一步滅小凸块间距,从而减小封装面积。

(2)引脚数(I0)更多:在相同尺寸的芯片封装中,相对于传统的打线封装,FC-CSP 可容纳更多的引脚数。

(3) 电性能更优:由于芯片与封装外壳布线之间的互连线更短,寄生参数更小,信号干扰较小,且信号传输延迟时问短,因此具有更小的电阻率,以区更快的信号传输速度。

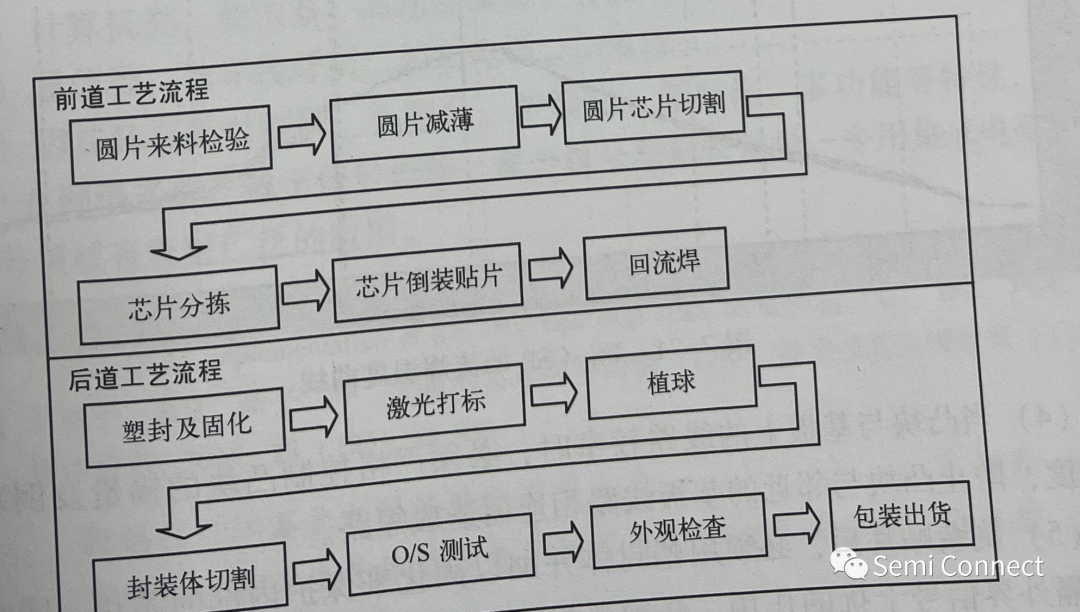

(4) 实现多种不同功能芯片及器件的一体式封装。以单芯片 (Single Die) FC-CSP 产品为例,FC-CSP 封装工艺流程如图所示。

FC-CSP 的关键技术如下所述、

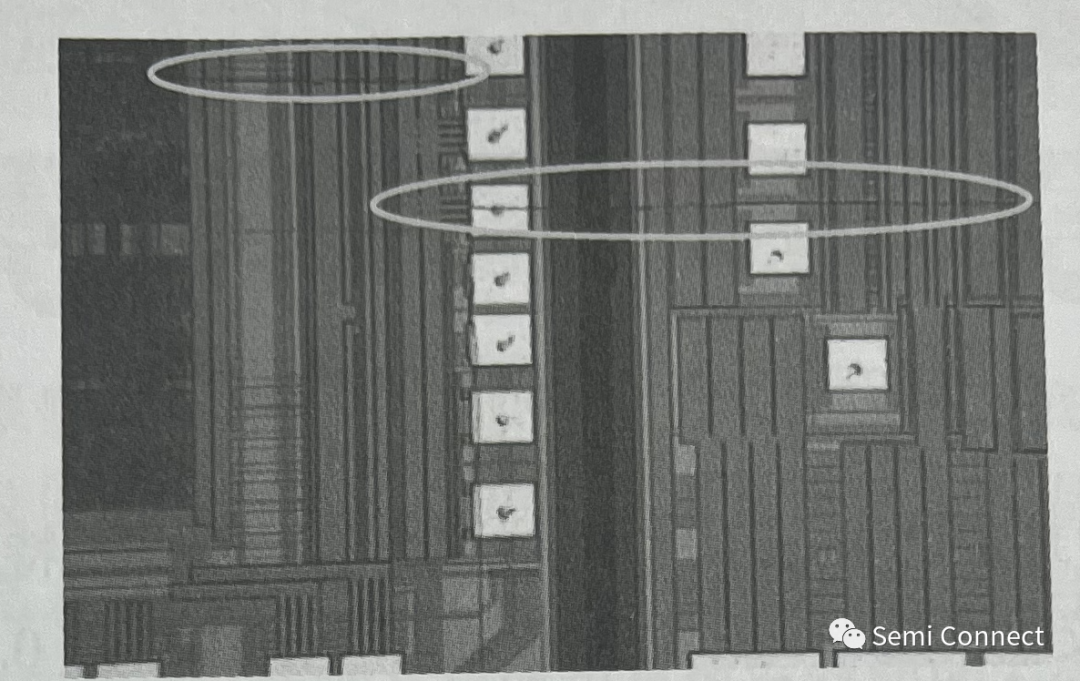

(1)FC-CSP 对于封装的厚度有较高的要求,因此在圆片减薄时,需要严格控制好最终的厚度(在目标值士151μm 以内)。另外,还要控制好工艺参数避免在切割时发生产品芯片破片及裂纹如图等问题

(2)由于采用回流焊连接芯片凸块及基板的线路,所以需要防止回流过程中的断路,以及过小间距时的短路问题。特别是当芯片与基板的面积比较大时,由于芯片与基板材料的热收缩比有所不同,可能造成高温回流焊时的翘曲不致,从而产生一定的应力,导致凸块与基板连接处发生断裂。

(3)必须严格控制回流焊的降温速率,避免凸块与基板结合处及圆片内低K材料的断裂。通常,降温到 150摄氏度以下时,应控制降温速率在4摄氏度/s以内,如图所示。

(4)当凸块与基板上的线路较窄时,必须严格控制凸块的锡量及倒装对位的精度,防止凸块与邻近的基板线路相连而造成短路。

(5)倒装贴片后,必须用塑封体并加以固化来保护内部的芯片,同时也起到阻隔外界信号干扰的作用。必须严格控制塑封过程中的固化时间及温度,避免塑封体与芯片分离,以及塑封后产品翘曲问题等的发生。

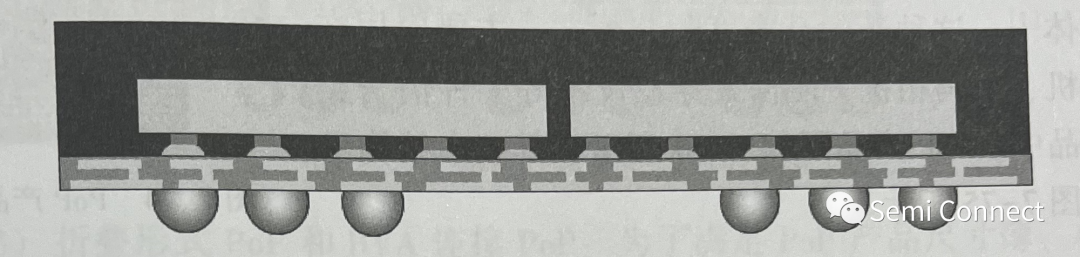

结合工艺和目前各 IC 制造厂 商的研发情况来看,FC-CSP 的主要结构类型有单芯片 (Single Die) FC-CSP、多芯片平置 ( Muli-Chip Side byside) FC-CSP(见图1)和叠层芯片混联 (Stacked-Die Hybid) FC-CSP(见图2)。叠层封装是指在一个芯腔或基片上将多个芯片堆看起来,芯片与芯片或封装之问实现连接。叠层封装主要应用在手机处理器中,以此来降低功耗、缩小尺寸,提高封装的集成度和性能。

随着 FC-CSP 技术的迅速推广,其应用也越来越广泛,主要应用领域如下

所述

(1)消费类电子产品:手机、便携式摄像机、数码电子产品、DVD、无线产品等。

(2)计算机类:稳压器、高速存储器、智能卡、外设等。

(3)通信类:数宇传呼机、移动电话、CPS 等。

(4)因其具有高引脚数、小型化、微型化、薄型化、多功能等特性,使得FC-CSP 在网络通信、数宇信号处理、混合信号和射频信号、专用集成电路、微控制器等领域有着更广泛的应用。

审核编辑:汤梓红

-

传统封装工艺流程简介2024-01-05 3358

-

SMT组装工艺流程的应用场景2023-10-20 1249

-

什么是倒装芯片 倒装芯片技术的优点 倒装芯片封装工艺流程2023-07-21 8602

-

圆片级芯片尺寸封装工艺流程与技术2023-05-06 4647

-

封装工艺流程--芯片互连技术2022-12-05 2484

-

芯片封装工艺流程讲解2022-10-31 13000

-

芯片封装工艺流程是什么2021-08-09 73404

-

集成电路芯片封装工艺流程2021-07-28 14218

-

倒装芯片的特点和工艺流程2020-07-06 14377

-

倒装晶片的组装工艺流程2018-11-23 4929

-

倒装芯片和晶片级封装技术及其应用2018-08-27 3269

-

ic封装工艺流程2010-07-18 3624

-

LAMP-LED封装工艺流程图2010-03-29 3843

-

IC芯片的封装工艺流程2008-05-26 29476

全部0条评论

快来发表一下你的评论吧 !