叠层封装工艺流程与技术

描述

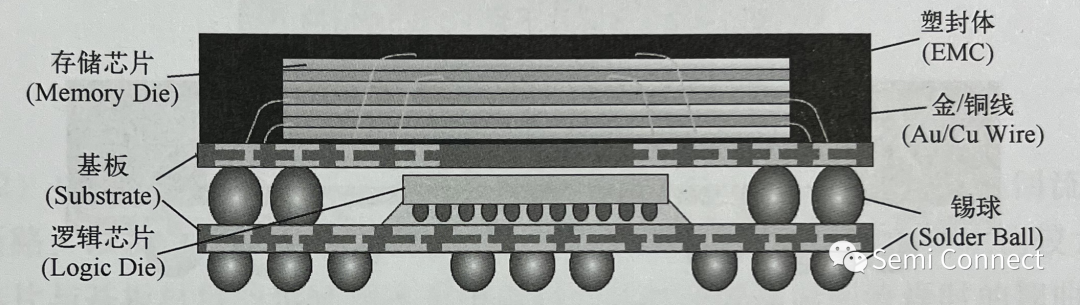

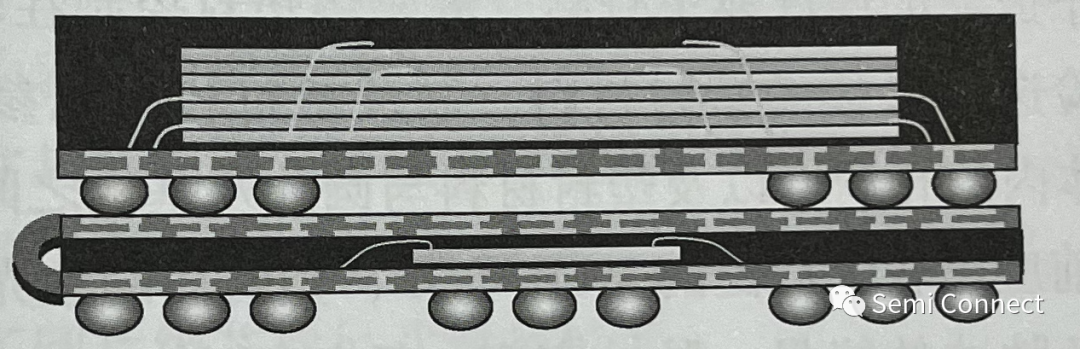

叠层封装 (Package on Package, PoP)是指在个处于底部具有高集成度的逻辑封装件上再叠加另一个与之相匹配的大容量存储器封装件,形成一个新的封装整体。这种新的高密度封装形式,主要应用在智能手机、数码相机、便携式穿戴设备等多种消费类电子产品中。PoP 产品图如下图1所示,其基本结构示意图如下图2所示。

POP 主要是针对移动设备而发展起来的系统集成3D封装,其结构主要有如下特点。

(1)存储器件和逻辑器件可自由组合,并可单独进行测试或替换,保障了成品率。

(2)POP 在垂直方向上实现堆叠,节省占板面积,提高了系统封装密度

(3)堆叠器件垂直互连取代了传统二维封装互连,可以实现逻辑器件和存储器件之间更快的数据传输。随着技术的发展,出现了如下几类主要的 POP 结构。

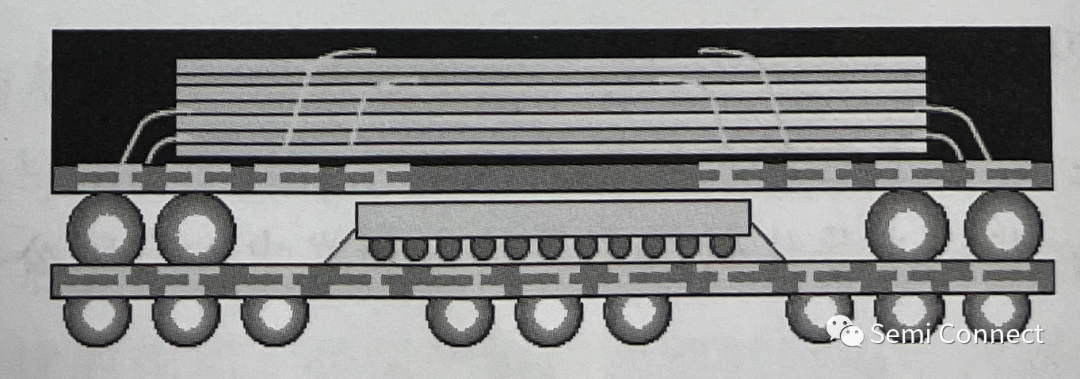

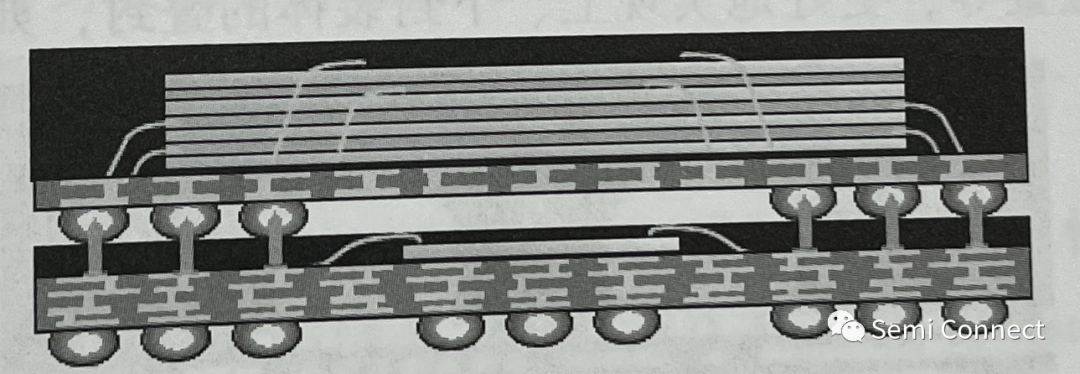

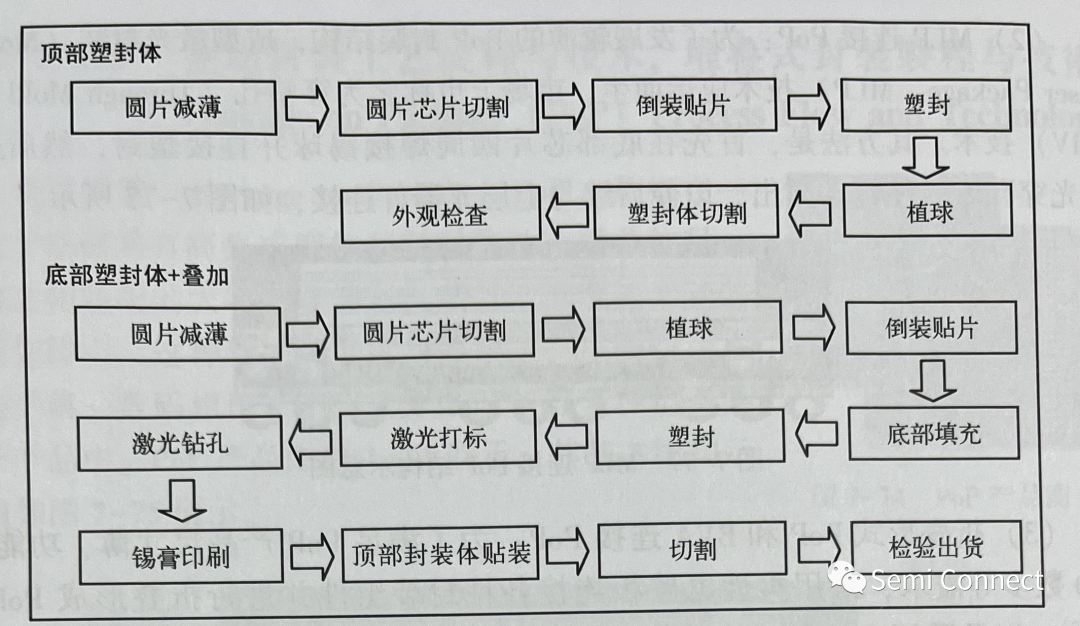

(1)锡球连接 PoP:逻辑芯片拥有更多的I/0 端口,因而常采用倒装互连(Flip Chip, FC)技术对其进行封装,并以此作为底部组件。底部芯片采用毛细管底部填充工艺(Capillary Under Fill, CUF),其结构示意图如图所示。

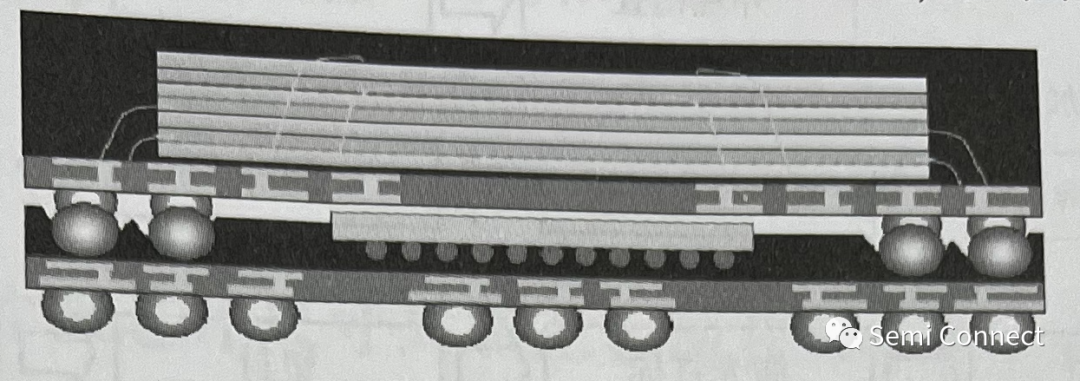

(2) MLP 连按PoP:为了发展较薄的PoP 封装结构,成型激光封裝( MoldimgLaser Package, MLP)技术应运而生,市场上也称之为穿塑孔 (Through Mold Via,TMV)技术。其方法是,首先在底部芯片四周焊接锡球并直接塑封,然后采用激光穿孔方式使锡球露出,以便后续与上层元器件连按,如图所示。

(3)折香形式 POP 和 BVA 连接PoP:为了满足 PoP 产品尺寸薄、功能强、I/0数多等需求,采用柔性电路板连接各种封装组件并进行折叠形成 PoP结构2,以及采用 BVA (Bond Via Array),技术1来提高产品性能、缩小引脚间距,如图所示。

依上所述,POP 封装体底部组件与顶部组件的连接方式主要有锡球连接(Attached with Solder Ball)、 MIP、柔性基板连接和 BVA。 MLP POP 封装工艺流程如图所示

PoP 关键技术如下所述。

(1) PoP 作为高度集成的 3D 封装体,对于封装及圆片的厚度有着更高的要求(低于 100um)。因而对减薄工艺提出了更高的要求,需严格控制并避免出现圆片破裂和芯片裂纹等问题,而且对于厚度薄于 100wm 的圆片进行切割时,易造成芯片剥离蓝膜。

(2)由于封装集成度高,信号端口之间的间距更小 (小于 0.3mom),所以对于植球工艺提出了更高的要求,需要更高精度的植球机,严格控制对推工艺精度。

(3)POP 对于成品的厚度要求较高,需要将塑封控制在较薄的厚度范围内,因而必领通过实验选择最佳的塑封材料,以及塑封和固化参数,以避免发生不完全塑封、塑封体内的孔洞,以及塑封材料与圆片及基板之问分层等问题。

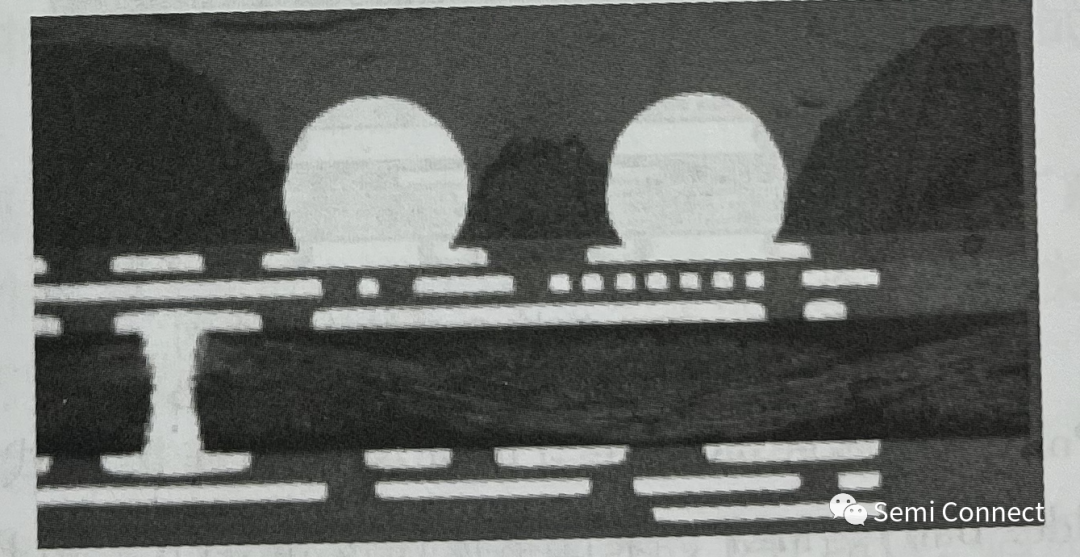

(4)作为目前应用较为广泛的 MLP-POP,塑封后的激光钻孔尤为重要,因此需要控制好激光脉冲的能量、脉冲宽度、重复频率、对位,从而控制好钻孔的尺寸、形状、位置等,更好地实现上、下封装体的叠封,如图所示。

(5) PoP作为高度集成的两个封装体的叠加,对于上、下封装体的翘曲有着较高的要求,应尽量使上、下封装体具有相同的翘曲方向,从而实现叠加上的一致性。对于封装体翘曲过大的情况,需要更好地控制香加时的锡膏量。进行新产品评估时,需要专门评估分析上、下封装体的翘曲数据。

审核编辑:汤梓红

-

半导体封装工艺流程的主要步骤2025-05-08 4092

-

传统封装工艺流程简介2024-01-05 2942

-

SMT组装工艺流程的应用场景2023-10-20 1130

-

SMT组装工艺流程的应用场景(多图)2023-10-17 2978

-

封装工艺流程--芯片互连技术2022-12-05 2327

-

芯片封装工艺流程讲解2022-10-31 12522

-

芯片封装工艺流程是什么2021-08-09 72527

-

集成电路芯片封装工艺流程2021-07-28 13868

-

倒装晶片的组装工艺流程2018-11-23 4823

-

ic封装工艺流程2010-07-18 3386

-

LAMP-LED封装工艺流程图2010-03-29 3822

-

BGA的封装工艺流程基本知识简介2010-03-04 7020

-

IC芯片的封装工艺流程2008-05-26 29183

全部0条评论

快来发表一下你的评论吧 !