如何用vcs+verdi仿真Verilog文件并查看波形呢?

描述

我们以一个简单的加法器为例,来看下如何用vcs+verdi仿真Verilog文件并查看波形。

源文件内容如下:

//adder.v module adder( input clk, input rst, input [9:0] A, input [9:0] B, output reg [10:0] C ); always @ ( posedge clk ) begin if(rst) C <= #`FFD 'b0; else C <= #`FFD A + B; end endmodule

我们再定义一个宏定义的文件:

//macro_define.sv `define FFD 1ns

我们需要再定义一个testbench文件:

//test.sv

module test;

reg clk;

reg rst;

reg [9:0] A;

reg [9:0] B;

wire [10:0] C;

initial begin

rst = 1;

A = 0;

B = 0;

#1us;

rst = 0;

#1us;

A = 10'd100;

B = 10'd200;

#1us;

A = 10'd300;

B = 10'd400;

#20us;

$finish;

end

initial begin

clk = 0;

forever #10ns clk <= ~clk;

end

adder add_inst(

.clk(clk),

.rst(rst),

.A(A),

.B(B),

.C(C)

);

`ifdef DUMP_FSDB

initial begin

$fsdbDumpfile("tb.fsdb");

$fsdbDumpvars("+all");

//string testname;

//if($value$plusargs("TESTNAME=%s", testname)) begin

// $fsdbDumpfile({testname, "_sim_dir/", testname, ".fsdb"});

//end else begin

// $fsdbDumpfile("tb.fsdb");

//end

end

`endif

endmodule

再定义一个filelist文件:dut.f

./macro_define.sv ./adder.v ./test.sv

最后就是需要一个Makefile文件了:

#!/bin/make all: comp sim comp: vcs -full64 -timescale=1ns/1ps -V -R -sverilog -debug_access+all +vc +v2k -kdb -l vcs.log -f dut.f +define+DUMP_FSDB=1 -top test sim: ./simv -l simv.log clean: rm -rf *~ core csrc simv* vc_hdrs.h ucli.key urg* *.log novas.* *.fsdb* verdiLog 64* DVEfiles *.vpd

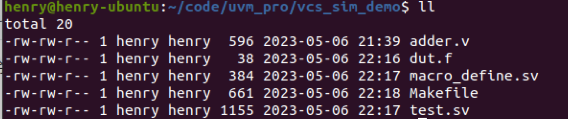

总的文件如下:

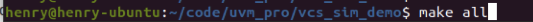

执行make all:

跑完后如下:

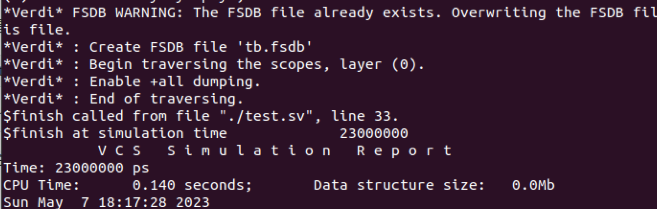

生成的文件如下:

用verdi打开波形:verdi -ssf tb.fsdb

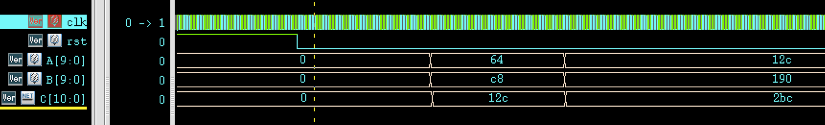

可以看到波形如下:

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

利用Verdi调试协处理器的实现步骤2025-10-30 320

-

在Linux上用vcs+verdi对demo_nice进行仿真没有成功的原因?2023-08-12 624

-

请问如何更新bin/run.makefile以支持VCS+Verdi工具?2023-08-11 596

-

Verdi环境配置、生成波形的方法2023-05-29 9343

-

如何用vcs+verdi仿真Verilog文件2023-05-11 3054

-

全网最实用的Verdi教程12023-05-05 22929

-

利用vcs+verdi仿真工具蜂鸟E200系列处理器仿真分析2022-11-17 4433

-

如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真2021-07-27 6809

-

VCS+Verdi如何安装?怎么破解?2021-06-21 7679

-

如何通过自动化脚本实现Questasim和Verdi的联合仿真2021-06-13 6813

-

vcs和verdi的调试及联合仿真案例2020-09-22 10091

-

请教VCS和verdi怎么联合使用2015-01-22 8234

全部0条评论

快来发表一下你的评论吧 !