软件与Verilog基本格式规范说明

描述

一、 说明

以前总是没有记录的习惯,导致遇到问题时总得重新回忆与摸索,大大降低了学习效率,从今天开始决定改掉这个坏毛病,认真记录自己的Verilog学习之路,希望自己能一直坚持下去。

二、 软件资源与硬件资源

软件资源说明:

1、UltraEdit:本博客所有的Verilog代码全部都在UltraEdit中编辑, UltraEdit具有语法高亮与自动补全(设置方法在本文最后面)功能,而且界面美观,绝对是写代码的利器。

2、ISE14.7或Vivado2016.3:本博客的FPGA选择的是Xilinx的,所以选择Xilinx集成开发套件,本来之前一直在用7系列的FPGA,但是目前手头只有一块Spartan-6系列的二手开发板,所以代码的验证都在Spartan-6上验证,但好在FPGA的结构基本类似,Verilog的代码基本可以通用。

3、ModelSim-win64-10.4-se:仿真工具使用ModelSim 10.4版本,其他版本也可以,无过多要求。

4、Windows-7 64-bit系统:建议大家在Windows-7 64-bit系统做开发 ,Windows-7 64-bit系统对以上软件的兼容性都比较好。我的笔记本电脑用的是Windows-8.1系统,安装ISE14.7以后导入ModelSim仿真库,选择库目录的时候出现了卡住的情况,这种就是ISE14.7与WIndows-8.1不太兼容导致的,解决办法如下。

解决Windows-8.1与ISE14.7不兼容的办法:

找到ISE安装目录的中的nt64文件夹,我的ISE的安装目录在D盘,所以nt64的路径如下D:Xilinx14.7ISE_DSISElib t64,然后把nt64文件夹中的libPortability.dll文件名改成libPortability.dll.org,再把libPortabilityNOSH.dll重命名为libPortability.dll。这样可以有效解决一部分兼容性的问题。

5、更多软件资源可以关注文末的微信公众号并输入关键字“软件安装包”获取

硬件资源说明:

1、目前手头只有一块二手的黑金AX545开发板,FPGA的型号是:XC6SLX45-2CSG324,所以代码都会在这个板子上进行验证。对于其他型号的FPGA只要理解原理了应该也不难上手。

三、 Verilog命名规范与格式说明

Verilog语言并没有固定的命名规范与编写格式,每个人根据自己的喜好而定就行了,我自己比较喜欢下面规范与格式。这里先写一部分,后面如果有补充的在加上。

Verilog命名规范:

1、所有输入端口以大写I加下划线开始,然后后面内容的一律用小写,信号比较长的话,后面的小写用下划线隔开。如:

input I_clk;

input I_led_mode;

如果输入端口低电平有效的话就在末尾加下划线和小写n,如:

input I_rst_n;

2、所有输出端口以大写O加下划线开始,然后后面内容的一律用小写,信号比较长的话,后面的小写用下划线隔开。如:

output O_led;

output O_led_mode;

3、所有reg变量以大写R加下划线开始,然后后面内容的一律用小写,信号比较长的话,后面的小写用下划线隔开。如:

reg R_cnt;

reg R_cnt_100ms;

4、所有wire变量以大写W加下划线开始,然后后面内容的一律用小写,信号比较长的话,后面的小写用下划线隔开。如:

wire W_cnt;

wire W_led_mode;

5、所有常量(parameter变量)以大写C加下划线开始,然后后面内容的一律用大写以示与变量的区别,信号比较长的话,后面的大写用下划线隔开。如:

parameter C_IDLE;

parameter C_FLASH_READ;

6、命名一定要有意义,看着变量名就大概能猜出它的作用,并适当采用缩写,下面几个缩写是写代码过程中比较常用的缩写。

‘rd’代替‘read’

‘wr’代替‘write’

‘cnt’代替‘count’

‘rst’代替‘reset’

‘addr’代替‘address’

Verilog编写格式:

1、always块的begin…end换行写,如:

always @(posedge I_clk or negedge I_rst_n)

begin

…

end

2、if…else if…else语句的begin…end换行并空一个Tab键(记得设置一个Tab为4个空格)写,如果if或者else下面只有一条语句那么就省略begin…end如:

if

begin

…

end

else if

begin

…

end

else

…

3、case…endcase语句中的条件后面如果只有一条语句,则直接在冒号后面写语句,default一定要写上,即使里面什么语句也没有。最好用UltraEdit的列模式功能把那些冒号和分号都上下对齐。如

case(...)

C_IDEL : …… ;

C_FLASH : …… ;

default : ;

endcase

case…endcase语句中的条件后面如果有多条语句,则直接在冒号后面换行加Tab键写begin…end。同样用UltraEdit的列模式功能把那些冒号和分号都上下对齐。

case(R_state)

C_IDEL :

begin

…… ;

end

C_ FLASH :

begin

…… ;

end

default :

begin

…… ;

end

endcase

4、例化模块的时候例化名就是在模块名前面加一个大写的U和下划线,并且用UE的列模式功能把括号和逗号都对齐。如:

led_work U_ led_work

(

. I_clk (I_clk ),

. I_rst_n (I_rst_n ),

.O_led_mode (O_led_mode ),

.O_led_out (O_ led_out )

);

附、 UltraEdit设置方法

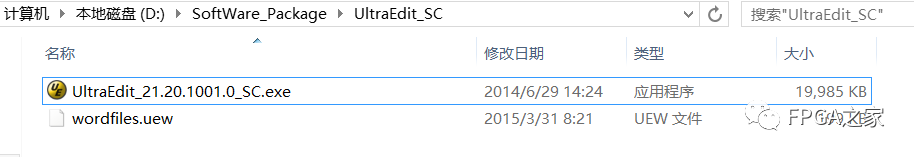

下载上文的UltraEdit压缩包并解压,里面有两个文件,一个是UE的安装包,一个是语法高亮文件

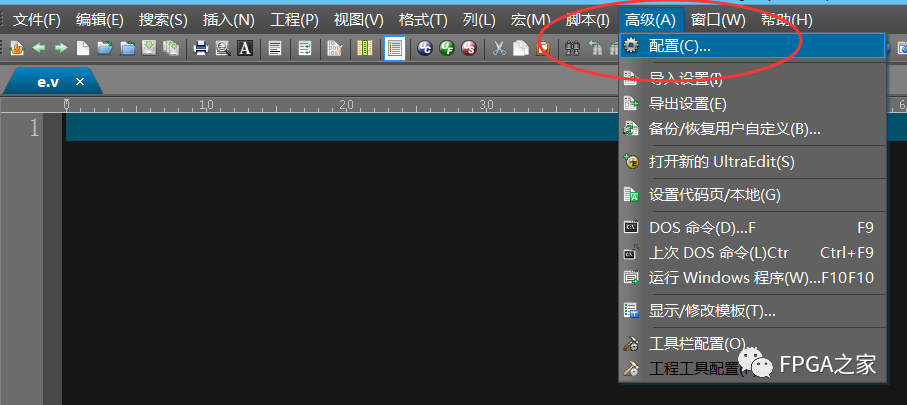

双击exe文件安装好了以后打开UE会提示选择风格,我比较喜欢黑暗风格,选完风格以后在菜单栏找到高级选项卡,然后在高级选项卡下载找到配置菜单

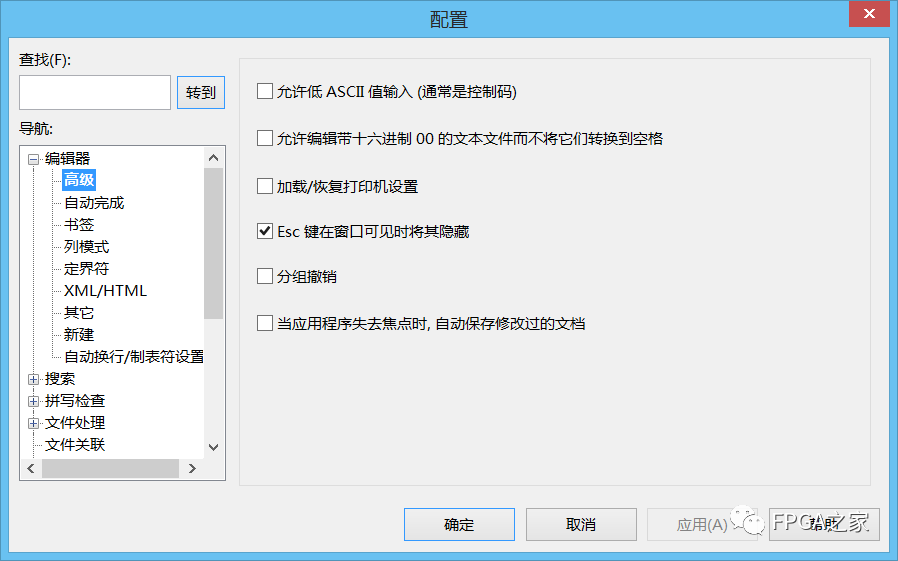

单击配置菜单,弹出如下界面

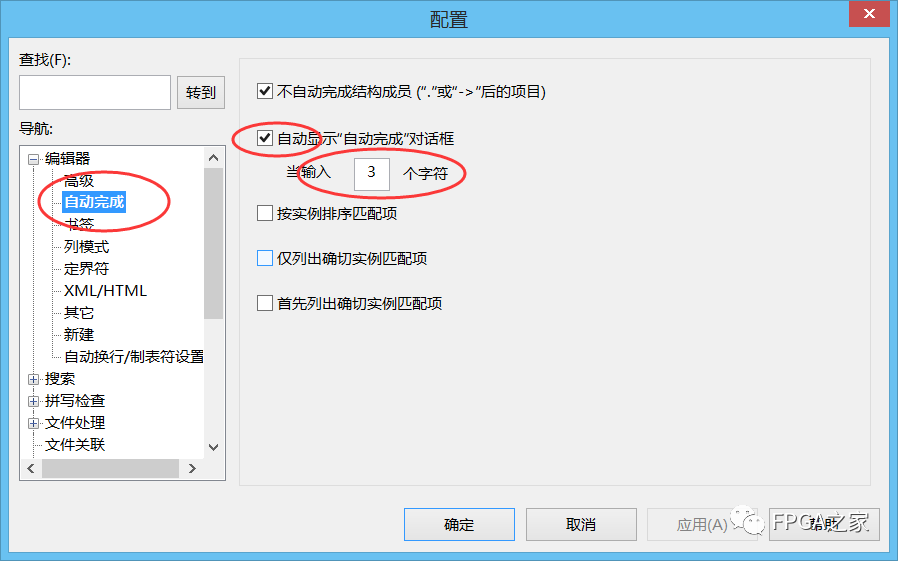

接着在上面的界面中找到自动完成功能并选中,然后按照下图进行设置

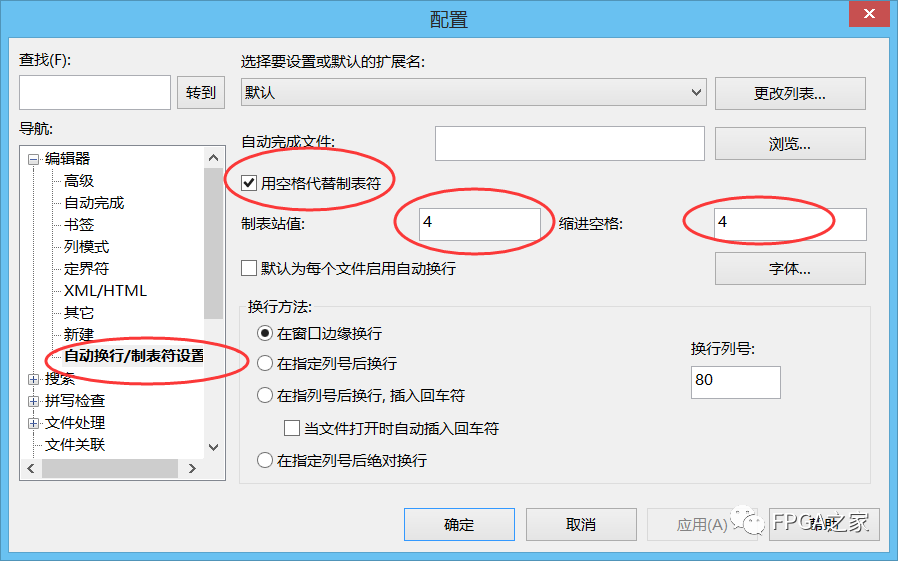

接着在找到自动换行/制表符设置,按照如下方式设置

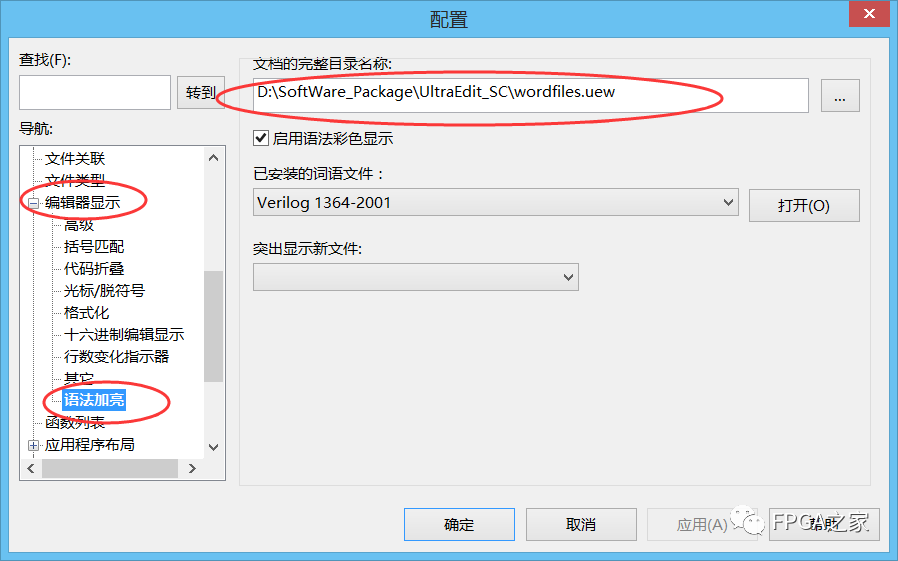

最后找到编辑器显示下面的语法加亮,选择安装包中的wordfile.uew配置文件就OK了,如下图所示

审核编辑:汤梓红

-

IC设计之Verilog代码规范2023-08-17 2783

-

FPGA的Verilog代码编写规范2023-08-15 3821

-

Verilog程序编写规范2022-09-15 5133

-

System Verilog问题和语言参考手册规范2020-12-24 3013

-

Verilog教程之Verilog的命令格式资料说明2019-01-09 1116

-

勇敢的芯伴你玩转Altera FPGA连载34:Verilog代码书写规范2017-12-27 3806

-

华为的verilog编码规范2017-11-01 1253

-

Verilog HDL代码书写规范2017-09-30 2370

-

VHDL与Verilog互转的软件2016-06-03 751

-

华为_VERILOG语言编写规范2016-03-25 640

-

【分享】verilog代码书写规范2015-05-21 5906

-

Verilog代码书写规范2010-04-15 683

全部0条评论

快来发表一下你的评论吧 !