固定优先级的仲裁round robin算法介绍

嵌入式技术

描述

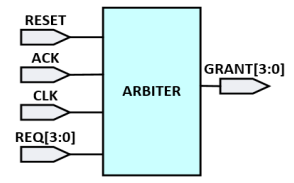

当总线上有多个master,他们都能发起传输请求req,要求占用总线。但资源是有限的,需要去仲裁谁获得总线使用权grant。 仲裁器Arbiter充当裁判,master想要访问总线,需要申请req,得到授权grant后,才发起传输。因而仲裁算法决定grant和req的函数关系

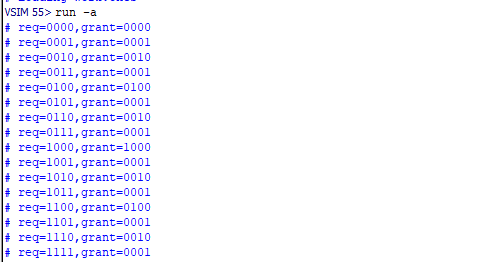

1、固定优先级 讨论一个固定优先级的仲裁算法,当master有4个时,即req[3:0],我们设定req[0]优先级最高,即当req[0]=1,grant[0]=1;req[1],req[2],req[3]优先级逐次降低 其真值表如下,功能其实很简单,从req低位到高位搜索1,第一个出现的1,其对应的grant位也是1。

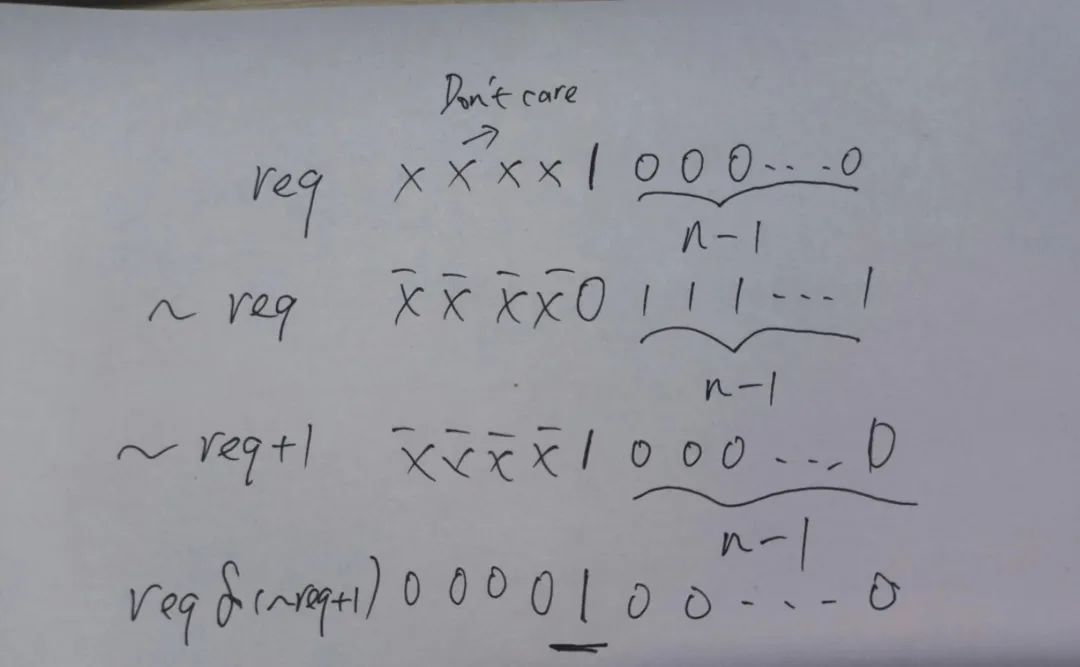

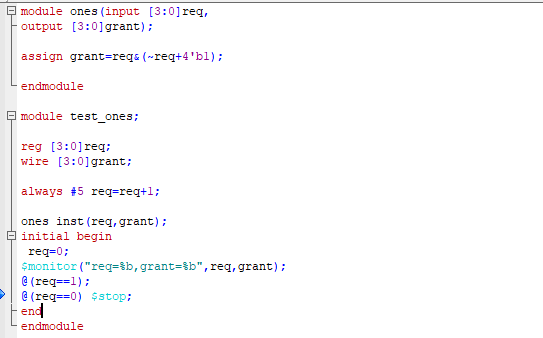

我也不知道咋推到来的,这样的逻辑关系,我们可以用:“req&req的补码 ”实现。简要论述一下,补码为req取反加1,即req'=~req+1。也就是grant=req&(~req+1)能概括上面的真值表。 如下图所示,假设req的第n bit为第一个1,~req将使得低n-1位全为1,~req+1将在第n位进位加1,其余高位仍正好是req的取反结果。这样一与,就能定位到1.

RTL如下

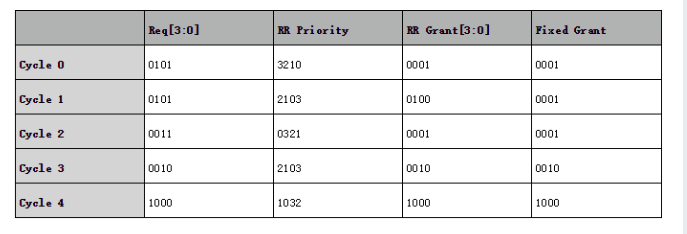

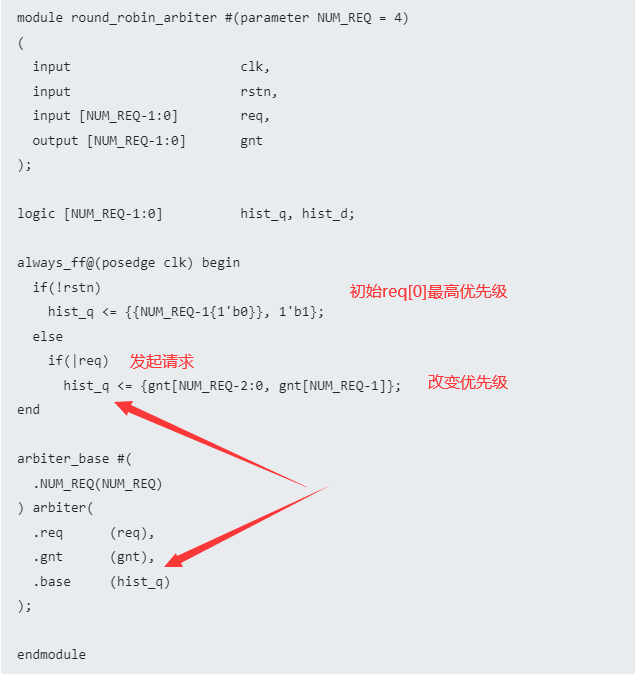

2、round robin算法介绍 回归主题round robin算法,说白了,就是以一定规则改变优先级:上次获得授权的master,其优先级降为最低,依然保持优先级向“左”递减的规律。 如下图所示,0时刻,优先级从LSB到MSB向左递减(数值越大,优先级低),grant[0]得到授权。1时刻,req[1]的优先级最高,req[0]的优先级最低,优先级呈现一个“循环”,

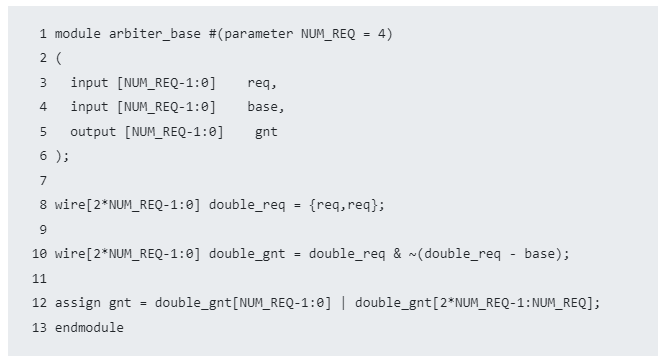

(图源:仲裁器设计(二)-- Round Robin Arbiter - 极术社区 - 连接开发者与智能计算生态 (aijishu.com),下同) 3、实现 那我们如何去调整优先级? 同样不知道咋来的,添加base信号改变优先级,其中base信号为独热码形式,如4’b0010,表示当前req[1]具有最高优先级 为了计算grant,我们需要拼接req为{req,req}为double_req,然后将double_req和~(double_req-base)相与得到double_gnt,最后将double_gnt两半相或得到输出gnt。

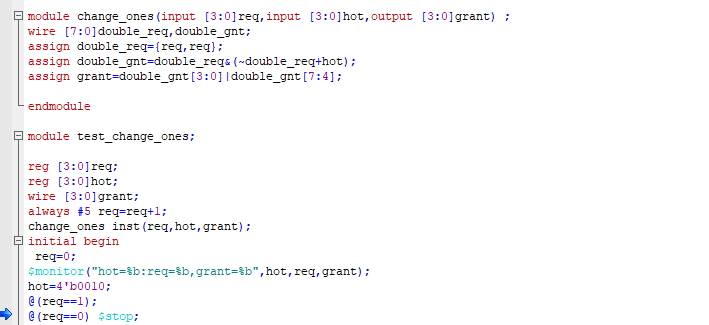

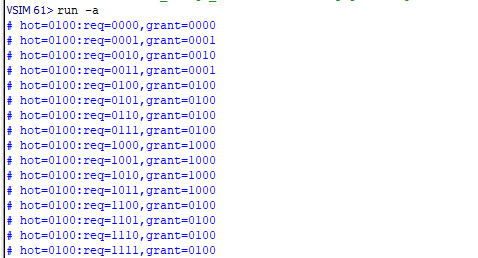

tb验证如下

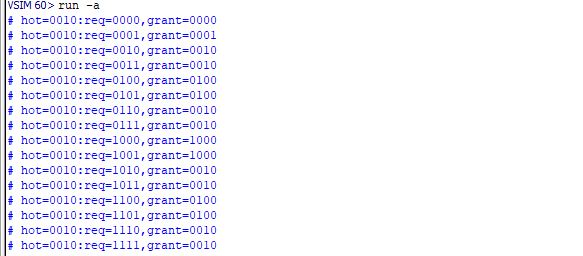

如下图,当hot=4'b0010,req[1]的优先级最高,req[2],req[3],req[0]次之

hot=4'b0100,req[2]拥有最高优先级,req[3],req[0],req[1]次之。不难看出,优先级最高的获得grant次数为8(一半),而次优先级则有4次,次次优先级有2次,最次优先级有1次,以及一个没有请求的情形。可以说,优先级高的获得授权的机会显著增多

正是hot既能显示优先级(1为最高优先级,而优先级呈现循环的向左递减),同时,hot能够影响grant的裁决,代码会简单很多。 上面的代码实现了grant=f(req,hot)的关系,我们的round robin还要求改变优先级。hot可以体现优先级,因而增加hot的改变即可。 一切都很巧合,仲裁的输出也是独热码,我们的round robin算法要求已经获得授权的master优先级最低,我们只需要对gnt向左循环移位即可

编辑:黄飞

-

基于优先级抢占系统的QNX调度算法2022-10-31 1580

-

RTOS应用中的优先级反转问题2022-12-14 2102

-

AXI4流互连IP2中True Round-Robin和Round-Robin仲裁方案之间的区别是什么2020-05-20 4621

-

如何在VHDL中实现简单优先级仲裁器2021-12-23 1677

-

什么是优先级位图算法?2021-12-27 1563

-

如何配置sequence的仲裁算法和优先级及中断sequence的执行2022-09-23 3176

-

简单优先级仲裁器:使用VHDL和Logisim在嵌入式系统中分配资源2019-02-13 1469

-

STM32单片机中抢占优先级和响应优先级的表达方式解析2019-10-14 12480

-

STM32F103芯片中断优先级以及FreeRTOS优先级设置2022-01-25 1769

-

uC/OS-II学习笔记——优先级反转与优先级继承机制2022-02-09 854

-

中断优先级处理的原则及配置 抢占优先级和响应优先级的区别2022-05-18 32080

-

具有固定优先级调度程序RTOS的优先级倒置2022-06-22 2248

-

Free RTOS的优先级翻转2023-02-10 2714

-

什么是优先级反转2023-04-24 3644

-

CLINT中断控制器优先级和抢占2023-10-08 1832

全部0条评论

快来发表一下你的评论吧 !