如何将包含XIlinx IP的用户模块封装成网表文件

描述

在Vivado TCL命令窗口中可以通过调用write_edif命令将用户自定义模块封装成.edf网表文件(类似ISE里的.ngc文件),但按照官方给出的参考用法生成的网表文件对自定义模块有种种限制,即待封装的模块不能含有Xilinx IP(少部分IP可以包含,如RAM IP、FIFO IP等),如DSP IP、MIG IP等,否则在编译时将报错,提示有未定义的黑盒。

那么如何将包含XIlinx IP的用户模块封装成网表文件,下面将给出详细步骤

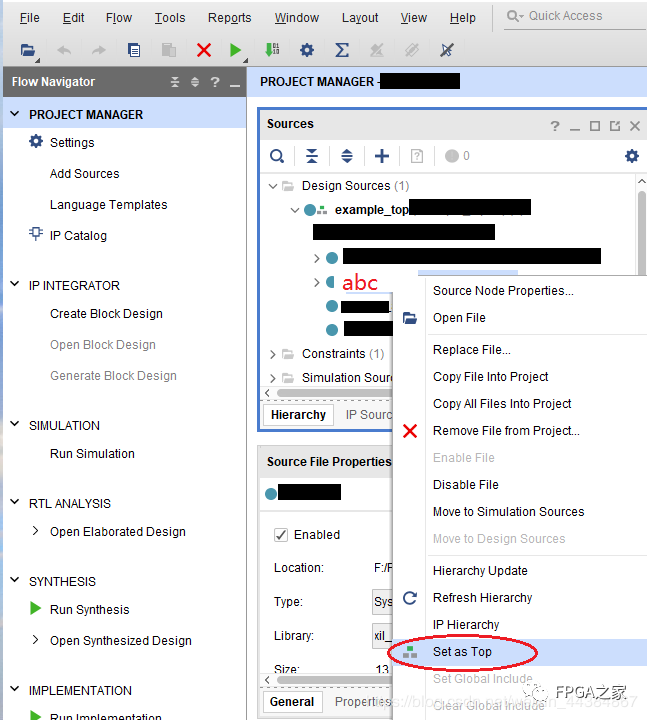

1. 将待封装模块设置为top层

如下图所示,待封装模块为abc,则选中abc后右键,选择“Set as Top”,

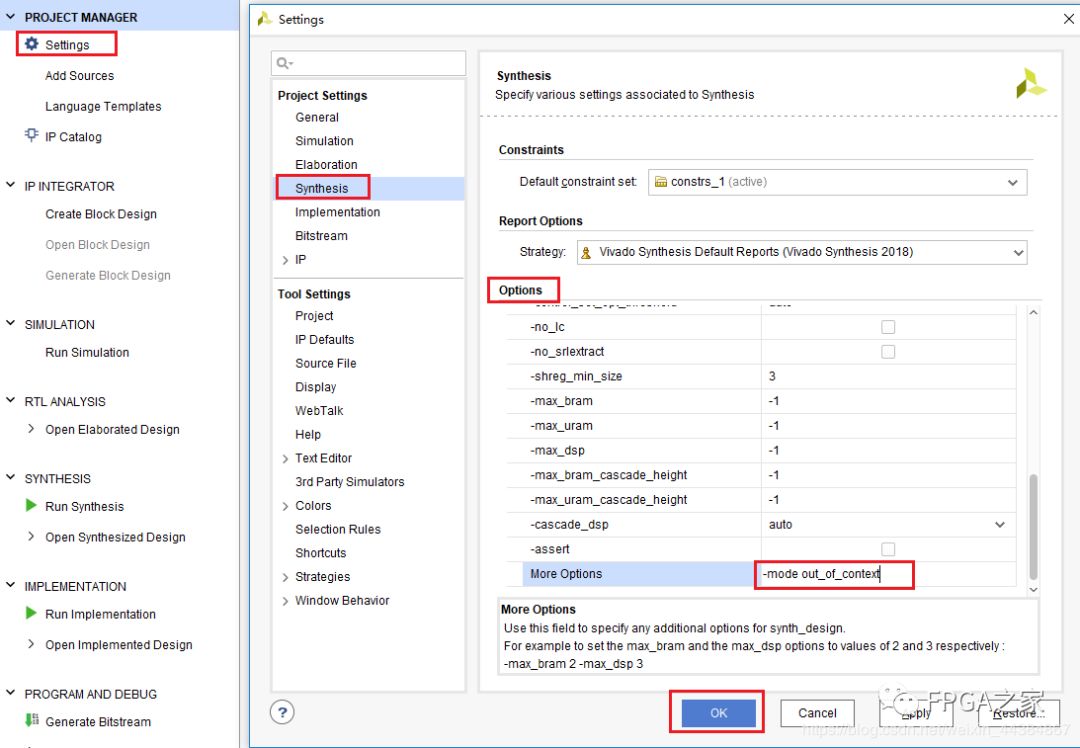

2. I/O Buffers设置

设置Settings–>综合 synthesis–>选项options下拉至最后一项:More Options,将其值设置为:

-mode out_of_context

-mode out_of_context表示在该级不插入任何I/O BUFFERs,该选项类似ISE里在相应设置处不勾选I/O BUFFERs。

另外还可以在选项options中找到“-flatten_hierarchy”,将层级结构设置为“full”,

层级结构则可设置“-flatten_hierarchy”选项为“full”:“全”该选项指示工具把层级全面变平,只剩下顶层,保护IP的层级结构不被其他用户清楚查看。

3. 综合

运行综合synthesis,完成综合后,打开综合设计open synthesized design

4. 生成仅包含IO端口信息的empty module

打开综合设计open synthesized design后,在TCL命令窗口执行如下命令:

2017.4之前版本:

write_verilog -mode port F:/FPGA/abc_stub.v

2018.1之后版本:

write_verilog -mode synth_stub F:/FPGA/abc_stub.v

其中F:/FPGA/替换为要存放的路径,如未指明路径,则将存放到工程文件所在路径下。

5. 生成edf文件

重头戏来了,分两条:

若不含Xilinx IP则可通过如下命令生成edf文件:

write_edif F:/FPGA/abc.edf

若含Xilinx IP则需通过如下命令生成edf文件:

write_edif -security_mode all F:/FPGA/abc.edf

6. 新工程中网表文件调用

将上述生成的abc_stub.v和abc.edf添加到新工程中即可。

7. 带Xilinx IP的另外一种网表封装方式(不推荐)

上述步骤3后,在tcl命令窗口中执行如下命令:

write_verilog -force abc_stub.v

-

vivado中,怎么将e203内核源代码封装成ip核,并添加总线?2025-11-10 1443

-

动态库封装成python模块的方法2023-07-13 1317

-

关于如何将函数封装成库使用的方法介绍2022-10-28 796

-

如何将常用接口封装成类似于NCNN的接口调用形式?2022-03-10 1523

-

Xilinx如何配置BSP工程包含的的公共模块2020-10-09 4566

-

怎么将HDL源文件添加到Xilinx IP?2020-04-21 1596

-

xilinx vivado 怎么封装包含一个ip核的自定义ip?2018-12-11 7522

-

如何将IP模块整合到System Generator for DSP中2018-11-20 3961

-

如何将CCS3.3工程中.C文件封装成OBJ库文件2018-11-02 6066

-

Vivado将模块封装为IP的方法介绍2018-06-26 9130

-

Xilinx CORE生成器IP列表名称及说明详解2017-11-18 5626

-

基于Vivado将verilog代码封装成IP的步骤2017-09-15 2483

-

xilinx EDF已经综合过的网表文件怎样添加到Vivado工程中?2016-09-07 15563

-

XILINX IP核移植2015-04-18 5919

全部0条评论

快来发表一下你的评论吧 !