倒装芯片封装的挑战

描述

新的工具和技术。

正在开发新的凸点结构以在倒装芯片封装中实现更高的互连密度,但它们复杂、昂贵且越来越难以制造。

对于具有高引脚数的产品,倒装芯片封装长期以来一直是一种流行的选择,因为它们利用整个芯片区域进行互连。该技术自 1970 年代以来一直在使用,从 IBM 的 C4开始,但真正广泛使用是在 1990 年代。

从那时起,凸块技术不断发展,以处理内存、高性能计算和移动计算设备所需的不断增加的功率和信号连接密度。满足这一需求需要新的互连技术,以实现更小的凸点间距,目前正在生产中。

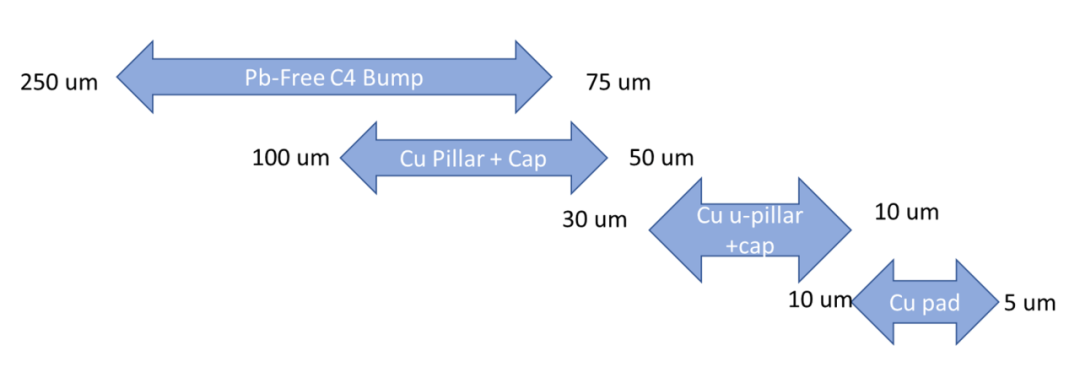

随着时间的推移,倒装芯片互连的路线图从无铅凸块发展到铜柱,再到铜微凸块。间距尺寸继续缩小,这反过来又给凸块和键合带来了制造挑战。

图 1:倒装芯片技术间距范围。来源:A. Meixner/半导体工程

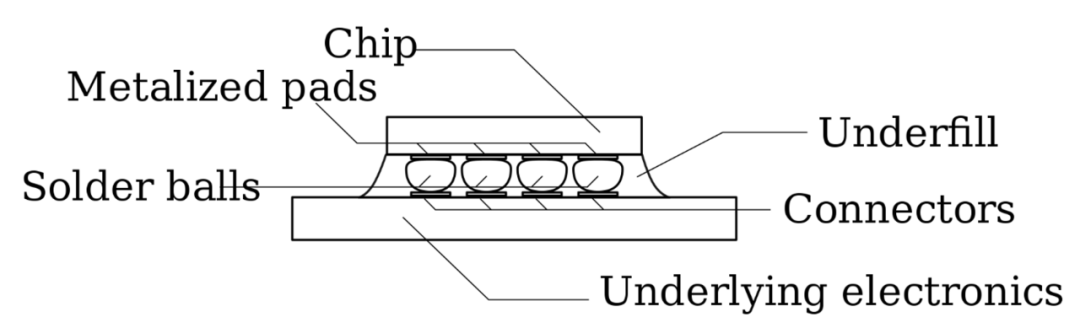

图 2:倒装芯片组件。来源:维基百科

图 2:倒装芯片组件。来源:维基百科

“在250微米及以下的倒装芯片领域,最初是锡铅凸块其中一项重大举措是无铅化。但是,当你开始达到 100 微米或以下时,你会开始看到更多的铜柱,尽管当我们看到高达 250 微米的铜柱时存在重叠,”Promex Industries 高级工艺工程师 Jeff Schaefer说。“对于 250 微米的间距,我们看到 130 微米的凸点尺寸或铜柱直径。一旦我们达到 100 微米的间距,它就是 80 微米的直径。我见过的最小间距是 62.5 微米间距和 40 微米柱。我预计很快就会看到 50 微米间距。”

基本的倒装芯片工艺在电路制造之后开始,此时在芯片表面创建金属焊盘以连接到 I/O。接下来是晶圆凸块,将焊球沉积在每个焊盘上。然后晶圆被切割,这些芯片被翻转和定位,使焊球与基板焊盘对齐。然后通常使用热空气使焊球熔化/回流,并且通常使用毛细管作用用电绝缘粘合剂在安装的管芯底部填充。

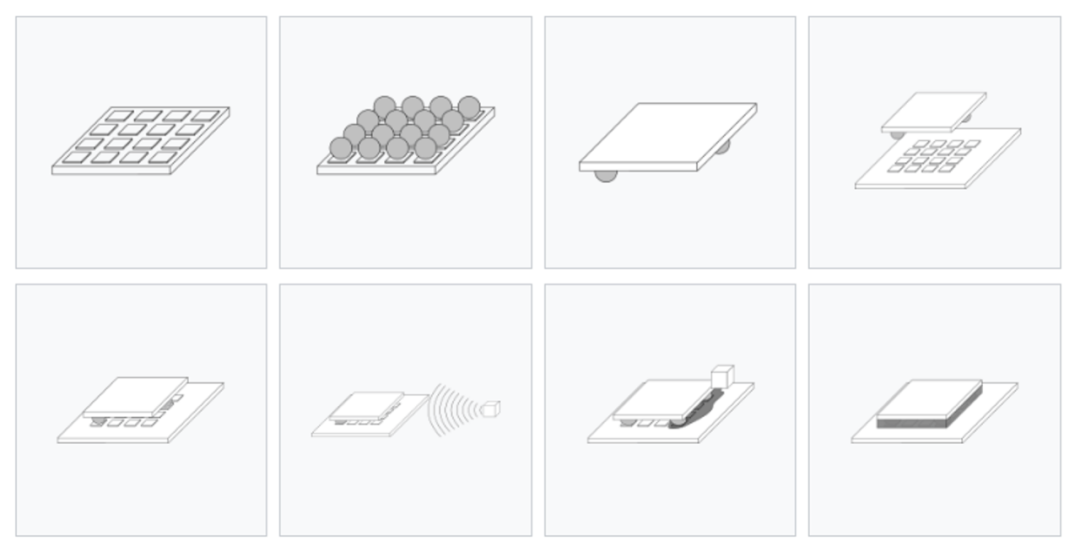

图 3:倒装芯片制造工艺。来源:维基百科

转向铜柱或微凸块需要光刻来创建这些结构。

Amkor Technology晶圆级封装高级副总裁 Doug Scott 表示:“铜柱通常用于 130µm 间距以下,因为铜柱不是圆形焊料凸点,而是主要是顶部有焊料的铜柱。”“这允许将铜柱凸点放置得更近,而不会在组装回流期间焊料连接在一起的风险——通常,~40 µm Cu + ~25 µm。”

主题也有变化。“微凸块是硅与硅之间互连的常用术语,它略有不同,因为 CTE(热膨胀系数)通常相同,” 日月光集团工程/技术营销高级总监 Mark Gerber 说。“用于铜柱的一些一般设计规则是相同的,但平坦的表面形貌和低应力接头允许使用的底部填充物具有灵活性。这也可以驱动单个凸点间距。今天,由于前面提到的路由考虑,对于所使用的晶圆级或晶圆厂级路由,35µm 的凸点全阵列间距是可能的。”

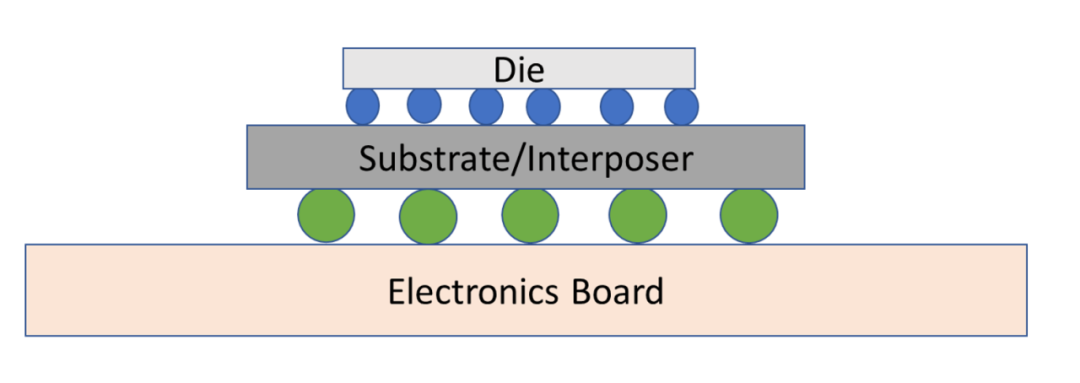

异构集成路线图描述了封装的所有方面,包括从焊线到硅通孔的裸片到基板互连。对于倒装芯片封装,芯片到基板互连、基板重新分布区域和基板到板互连都在制造限制中发挥作用。

图 4:倒装芯片封装的概念图。来源:A. Meixner/半导体工程

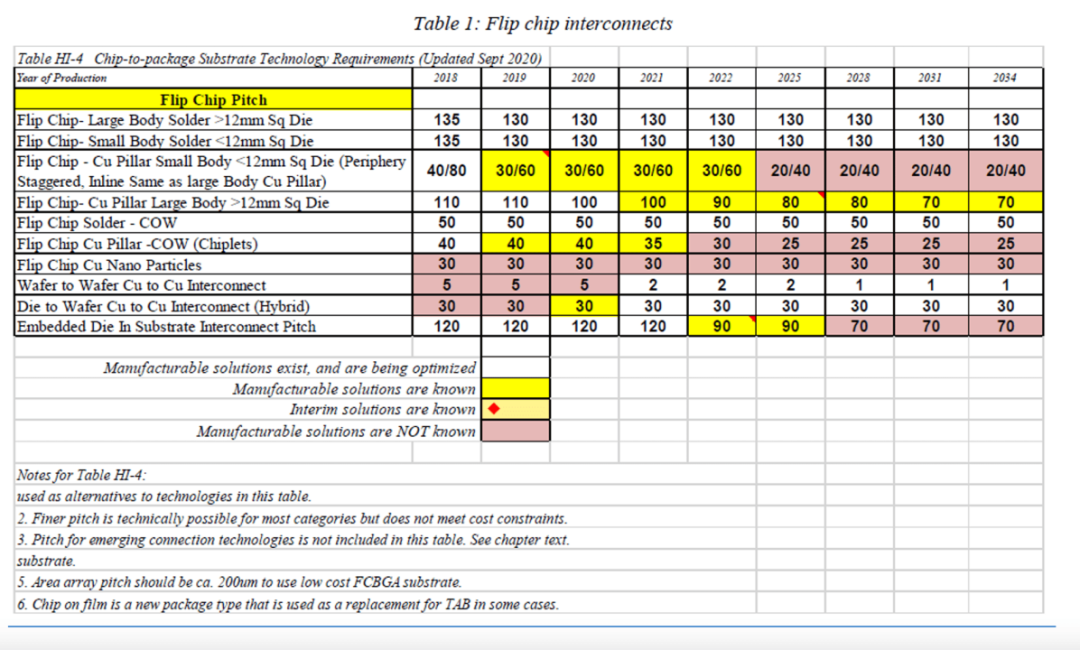

表 1 中列出了每种倒装芯片互连技术的最小间距。

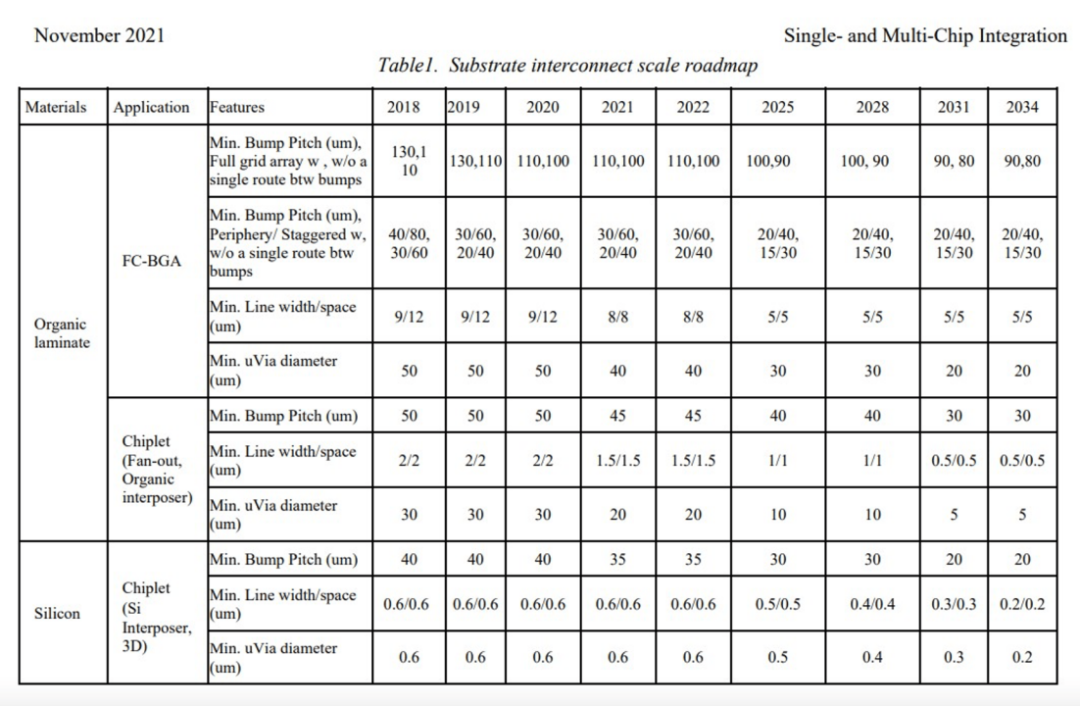

基板互连(将封装连接到电路板的部分)的相应表格。

互连技术的每一次变革都会带来新的工艺及其局限性,从而推动创新、良率管理和缺陷检测。

凸块技术限制

凸块技术是通过间距、尺寸、高度以及电气和机械特性来衡量的。热注意事项因材料的 CTE 不匹配而异。翘曲是较大管芯和晶圆的一个问题,在管芯贴装之前对晶圆进行背面研磨会加剧翘曲。

“对于每种类型的互连,间距限制有许多驱动因素,”ASE 的 Gerber 说。“从传统的焊料凸点倒装芯片互连开始,间距能力取决于底部填充的坍塌高度、走线布线的捕获焊盘间距、焊球到焊球短路风险的捕获焊盘间距以及其他几个与间距相关的敏感性。预装凸块高度有一个定义的高度,但正如 IBM 定义的 C4 术语——受控塌陷芯片连接——焊料凸块的直径和捕获焊盘尺寸将决定互连的“塌陷或最终高度”。这是使用与间距相关的焊料凸点的主要间距限制因素。”

凸点高度由设计决定,也有加工选择。

“对于标准的电镀焊料凸点和铜柱凸点,预组装凸点高度通常在 70µm 到 75µm 左右,组装后塌陷的凸点高度约为 50µm,以便为凸点之间的底部填充流动留出 x、y、z 空间。微凸块的凸块高度要低得多,并且涉及的焊料电镀要少得多。具体来说,根据间距和末端需求,微凸块的高度可以小于 10µm,同时减少铜和焊料的高度,”Amkor 的 Scott 说。“标准电镀焊料凸点通常用于 130µm 至 250µm 的间距。在 130µm 以下,当以 70µm 预组装凸点高度开始时,凸点之间没有足够的 xy 空间。”

创建铜柱需要比焊料凸点更多的处理步骤。

“当我们过渡到 die-to-die 世界时,技术是不同的,因为现在你正在处理晶圆,而与 die-to-substrate 相比,planerites 非常好。首先创建铜柱,在要获得焊料或铜柱的初始晶圆上,先是凸点下金属 (UBM)。它是向下进入硅的开口上方的一个小盖子。然后我们用它做一个铜芯,然后在上面放一个锡帽。然后是接收晶圆,它们看起来像是有一个 UBM 焊盘,上面通常有一些镍金类型的镀层,因此它既漂亮又原始,”Promex Industries 的 Schaefer 解释道。因此,您没有像层压基材那样有轻微的压痕,而是有轻微的挤压。我们发现我们实际上能够在没有“焊盘上焊料”的情况下将它们湿焊。' 这就是它们的设计和建造方式。它几乎就像焊料和焊盘一样,因为它是一个小圆顶,而不是试图进入孔内。”

铜柱形成所需的光刻步骤具有限制以及基板设计规则。

“对于由铜柱和尖端焊帽组成的铜柱,铜柱高度可以定义为一个或多个光致抗蚀剂层厚度的限制,并且当您减小间距时,铜柱的纵横比铜柱高度与光刻胶材料和成像工具功能一起成为限制,”Gerber 说。“铜柱互连的第二个限制是使用的基板设计规则。对于 >110um 的精细间距,使用了 2 种主要方法 - BOT(迹线上键合)或 ET 嵌入式迹线,其中铜柱的焊帽放置在迹线顶部,而不是传统的捕获焊盘。铜柱尺寸和形状,包括上述限制,可以限制继续缩小间距的能力和路线图。许多这些限制是由于能够在基板侧的柱子之间布线。随着晶圆级 RDL 等新技术的出现,互连路线图将得到进一步推进,但在底部填充等制造工艺的高度/纵横比方面仍然存在限制。”

其他人同意底部填充工艺会带来挑战。“当你获得更精细的间距和更小的凸起时,它们会变得更短。现在越来越难找到底层填充材料。过去,底部填充胶被设计为小于 5 密耳的间隙,现在它们降至 3 密耳,即 75 微米,”Schaefer 说。“现在我们开始看到 60 和 25 微米的间隙。我敢肯定人们正在研究新的底部填充胶。但是还有很多事情要做。一方面,当你得到更细的颗粒时,它变得更像淤泥,这使得它更难流动。这是一个需要移除的障碍。”

管理良率

随着凸块技术变得越来越小,额外的处理步骤——例如,用于创建铜柱的光刻——为良率检测器开辟了新的机会。对于成功的键合工艺,微粒、表面污染物和焊料凸点空洞都会影响良率。这些需要过程控制、计量和检查。

需要自然控制污染。“一级 OSAT 投资于降低工厂污染源的水平,从而降低缺陷率,”Amkor 的 Scott 说。

底部填充工艺的准备工作也不应被低估。

“一般来说,对于层压板,你需要在倒装芯片之后进行底部填充,”Promex 的 Schaefer 说。“我们决定将其放置在何处以及如何对其进行回流。我们清洁它以清除芯片和基板之间间隙下的任何助焊剂材料。然后我们将用流动的环氧树脂进行底部填充。它旨在浸湿而不留下空隙和那种性质的东西。但是,随着我们进入更精细的球场,我们面临着挑战。凸点变得更短,随着它们变得更短,芯片和基板之间的间隙变得更小,因此更难清洁。想象一下,将两个载玻片粘在一起,试图清除它们之间的污垢。”

计量和检测需求

对于管理过程控制和产量,计量和检测工具发挥着重要作用。ASE 的 Gerber 说:“除了在设置和定义的生产间隔时使用的过程中横截面分析之外,市场上还有一些工具可以帮助提供有关互连完整性的指导。”

凸块工艺和键合工艺各自具有需要监控的特定特性。对于凸块,计量学侧重于直径、高度和共面性。更小的间距需要更严格的凸点直径和高度控制。类似地,随着凸块高度的缩小,共面性窗口变得更小。通常,允许有 10% 的变化。例如,30µm 的凸点高度会导致 ±3µm 的允许偏差。超过此值会导致粘合不成功或粘合不良。

“键合通常使用大回流焊炉完成,”Amkor 高级封装和技术集成副总裁 Mike Kelly 说。“回流工艺的初始特征是使用阴影波纹来量化回流期间的翘曲,并使用烘箱的温度映射来确保倒装芯片部件本身的温度控制一致。在设置过程中,进行机械芯片提升和检查以确保良好的焊料润湿。此外,助焊剂通常通过“浸入式助焊剂”施加,其中芯片凸点“浸入”薄的、严格控制的助焊剂储层中。这些物品的目视检查是在抽样的基础上进行的。”

目视检查自动化程度的提高减少了对操作员查看图像和做出决定的依赖。凸块连接的指数增长是一个驱动因素。键合工艺的改变提供了另一个。自对准回流焊工艺是一项成熟的技术。与先进封装中常用的热压键合,有通过电气测试的可靠性机制。这反过来又促使使用 X 射线检测和计量工具来查看键合后的凸点。

“对于低复杂性包装,设施可以摆脱操作员和手动检查。对于具有 100 个凸点的零件,此方法是可行的。在 1,000 次颠簸时,这绝对是一种压力。一旦零件有 10,000 个凸点,就没有机会了。我们超越了这一点,我们需要转向下一个方法,”Bruker 应用和产品管理总监 Frank Chen指出“质量和复杂性是相辅相成的,因为当你试图制造更复杂的东西时,你的产量会受到影响,并且需要一些新的工具。而工装既是制程工具,又是计量工具,两者需要并行推进。从我们自己的研究中,我们看到,一旦你进行了 1,000 次颠簸,你就需要开始思考‘我的手动技术不够用,我需要一些新的东西。”

各种检测和计量工具可用于支持封装制造。

“有几种方法可以或应该用于实现过程控制。首先,传统二维检测 (AOI) 用于每个工艺流程(即 IQC、OQA、照片、清洁、电镀等)的 100% 表面缺陷检测。接下来,二维计量 (AOI) 可用于控制凸点尺寸和直径尺寸控制。此外,3D 计量 (AOI) 可用于采样凸块高度/共面度计量信息采集(这通常使用基于激光三角测量的技术完成),”Onto Innovation 产品营销经理 Nathan Peng说 “此外,3D 计量可以针对单个凸点高度特征,通常使用白光干涉仪技术收集。此外,还有一些方法可以检测凸点顶部的有机残留物,这些有机残留物可能导致凸点与焊盘连接失败。”

结论

需要更高互连数量的产品继续推动互连路线图。每种倒装芯片技术都有制造限制,包括材料特性、挑战底部填充技术的缩小尺寸,以及增加使用光刻技术来创建互连结构。键合工艺的任何变化都会导致计量和检测步骤的增加,以满足良率和质量目标。

审核编辑:刘清

-

倒装芯片封装选择什么样的锡膏?jf_17722107 2023-10-31

-

倒装芯片和晶片级封装技术及其应用2018-08-27 3272

-

倒装芯片应用的设计规则2019-05-28 3157

-

倒装芯片工艺挑战SMT组装2006-04-16 1871

-

倒装芯片封装的发展2011-10-19 5654

-

倒装芯片 CSP 封装2022-11-14 944

-

什么是倒装芯片 倒装芯片技术的优点 倒装芯片封装工艺流程2023-07-21 8613

-

倒装芯片和芯片级封装的由来2023-10-16 2319

-

先进倒装芯片封装2023-11-01 574

-

芯片倒装Flip Chip封装工艺简介2024-02-19 7094

-

浅谈FCCSP倒装芯片封装工艺2024-03-04 6017

-

倒装芯片封装技术解析2024-10-18 2783

-

倒装芯片的优势_倒装芯片的封装形式2024-12-21 4239

-

倒装芯片封装:半导体行业迈向智能化的关键一步!2025-02-22 2050

-

全面剖析倒装芯片封装技术的内在机制、特性优势、面临的挑战及未来走向2025-03-14 2317

全部0条评论

快来发表一下你的评论吧 !