基于XY平面延伸和Z轴延伸的先进封装技术

制造/封装

描述

先进封装分为两大类:

基于XY平面延伸的先进封装技术,主要通过RDL进行信号的延伸和互连;

基于Z轴延伸的先进封装技术,主要是通过TSV进行信号延伸和互连。

基于XY平面延伸的先进封装技术

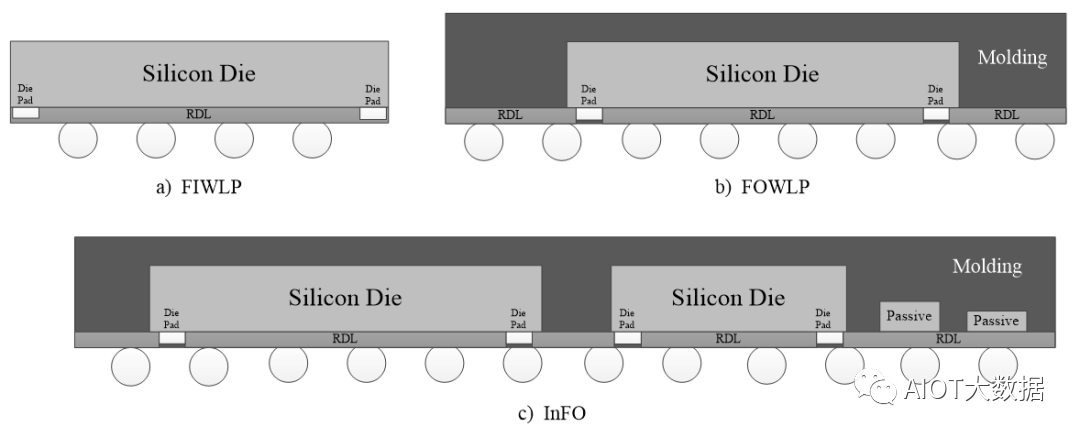

这里的XY平面指的是Wafer或者芯片的XY平面,这类封装的鲜明特点就是没有TSV硅通孔,其信号延伸的手段或技术主要通过RDL层来实现,通常没有基板,其RDL布线时是依附在芯片的硅体上,或者在附加的Molding上。因为最终的封装产品没有基板,所以此类封装都比较薄,目前在智能手机中得到广泛的应用。

1.FOWLP

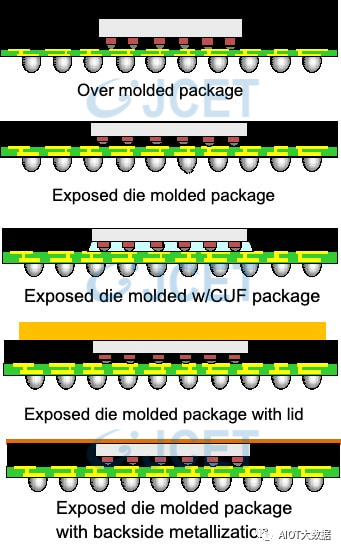

FOWLP(Fan-outWaferLevelPackage)是WLP(WaferLevelPackage)的一种,因此我们需要先了解WLP晶圆级封装。因为封装完成后再进行切割分片,因此,封装后的芯片尺寸和裸芯片几乎一致,因此也被称为CSP(ChipScalePackage)或者WLCSP(WaferLevelChipScalePackaging),此类封装符合消费类电子产品轻、小、短、薄化的市场趋势,寄生电容、电感都比较小,并具有低成本、散热佳等优点。

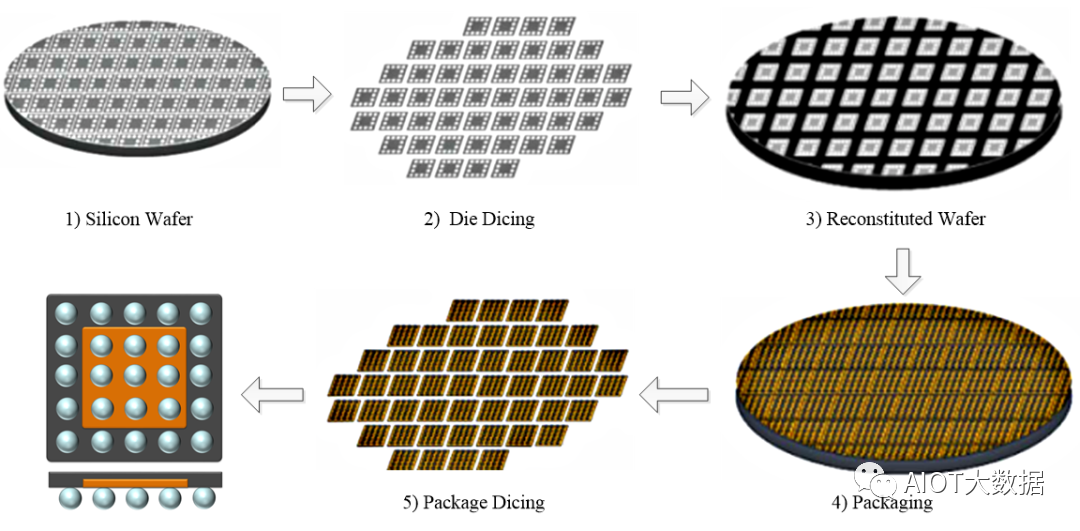

FOWLP,由于要将RDL和Bump引出到裸芯片的外围,因此需要先进行裸芯片晶圆的划片分割,然后将独立的裸芯片重新配置到晶圆工艺中,并以此为基础,通过批量处理、金属化布线互连,形成最终封装。FOWLP封装流程如下图所示。

无论是采用Fan-in还是Fan-out,WLP晶圆级封装和PCB的连接都是采用倒装芯片形式,芯片有源面朝下对着印刷电路板,可以实现最短的电路径,这也保证了更高的速度和更少的寄生效应。另一方面,由于采用批量封装,整个晶圆能够实现一次全部封装,成本的降低也是晶圆级封装的另一个推动力量。

2.INFO

InFO(IntegratedFan-out)是TSMC)于2017年开发出来的FOWLP先进封装技术,是在FOWLP工艺上的集成,可以理解为多个芯片Fan-Out工艺的集成,而FOWLP则偏重于Fan-Out封装工艺本身。

3.FOPLP

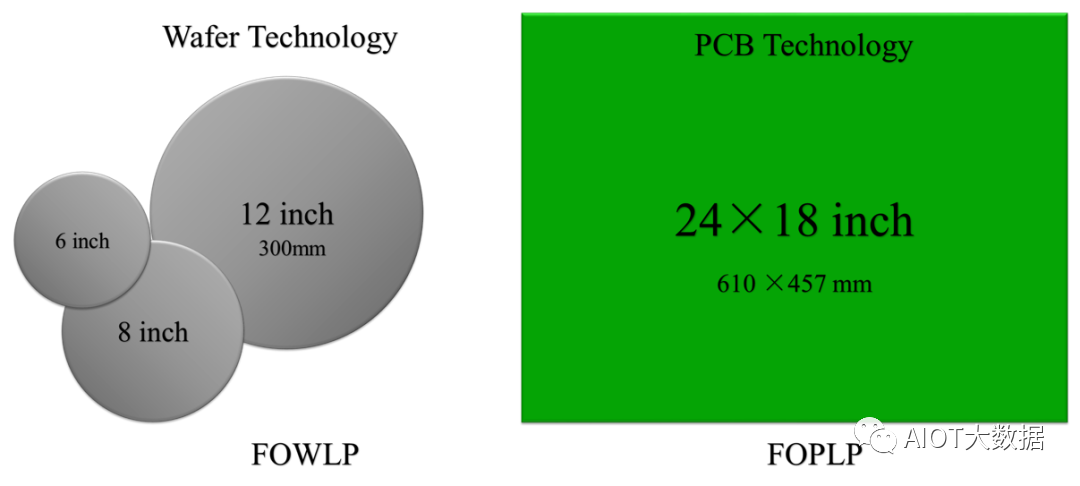

FOPLP(Fan-outPanelLevelPackage)面板级封装,借鉴了FOWLP的思路和技术,但采用了更大的面板,因此可以量产出数倍于300毫米硅晶圆芯片的封装产品。

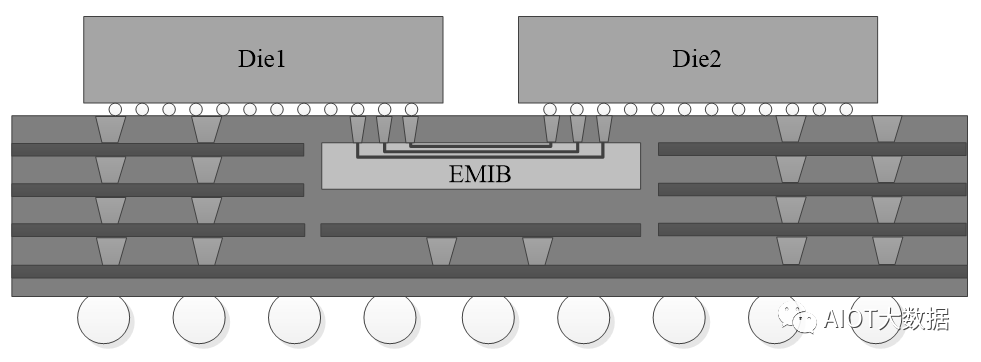

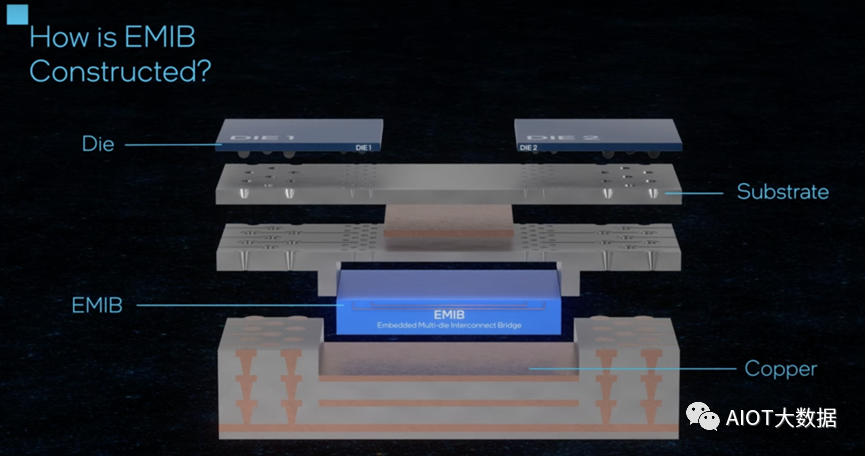

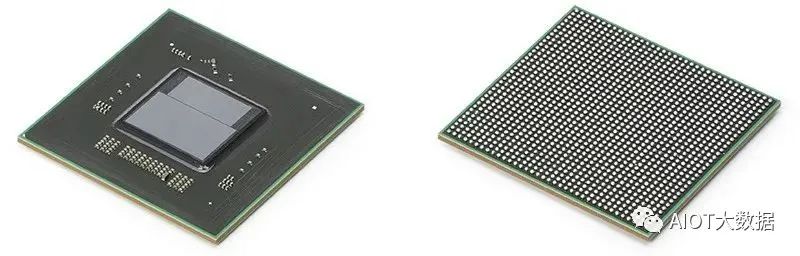

FOPLP采用了PCB上的生产技术进行RDL的生产,其线宽、线间距目前均大于10um,采用SMT设备进行芯片和无源器件的贴装,由于其面板面积远大于晶圆面积,因而可以一次封装更多的产品。相对FOWLP,FOPLP具有更大的成本优势。目前,全球各大封装业者包括三星电子、日月光均积极投入到FOPLP制程技术中。4.EMIBEMIB(EmbeddedMulti-DieInterconnectBridge)嵌入式多芯片互连桥先进封装技术是由英特尔提出并积极应用的,和前面描述的3种先进封装不同,EMIB是属于有基板类封装,因为EMIB也没有TSV,因此也被划分到基于XY平面延伸的先进封装技术。

和硅中介层(interposer)相比,EMIB硅片面积更微小、更灵活、更经济。EMIB封装技术可以根据需要将CPU、IO、GPU甚至FPGA、AI等芯片封装到一起,能够把10nm、14nm、22nm等多种不同工艺的芯片封装在一起做成单一芯片,适应灵活的业务的需求。

通过EMIB方式,KBL-G平台将英特尔酷睿处理器与AMDRadeonRXVegaMGPU整合在一起,同时具备了英特尔处理器强大的计算能力与AMDGPU出色的图形能力,并且还有着极佳的散热体验。这颗芯片创造了历史,也让产品体验达到了一个新的层次。

基于Z轴延伸的先进封装技术

基于Z轴延伸的先进封装技术主要是通过TSV进行信号延伸和互连,TSV可分为2.5DTSV和3DTSV,通过TSV技术,可以将多个芯片进行垂直堆叠并互连。

5.CoWoS

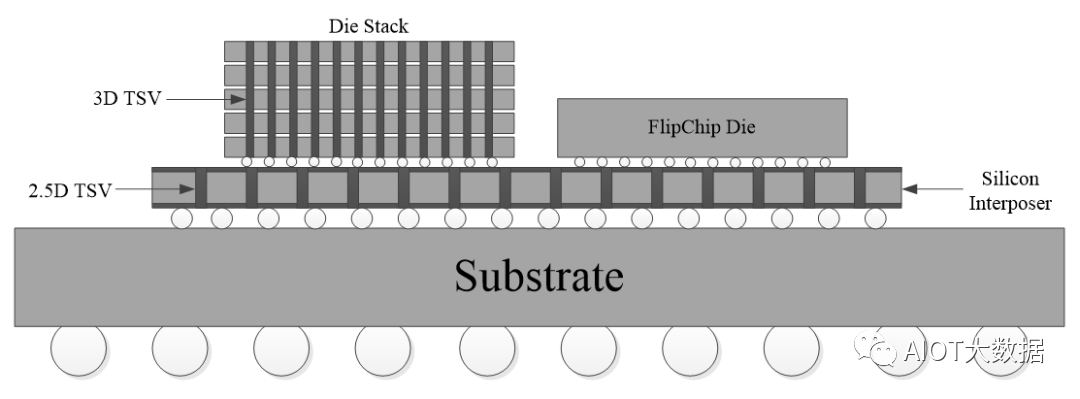

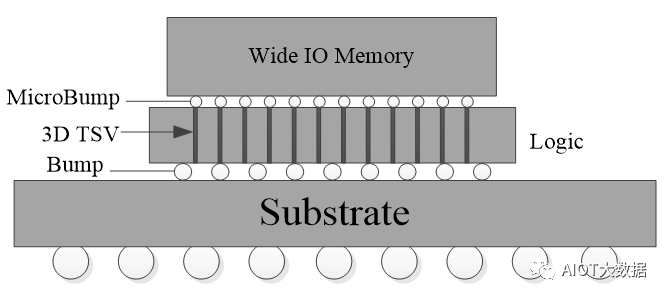

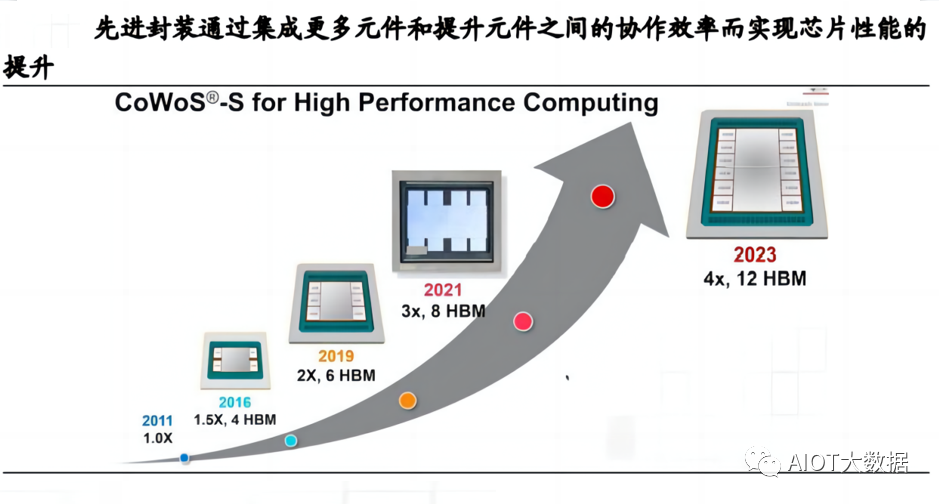

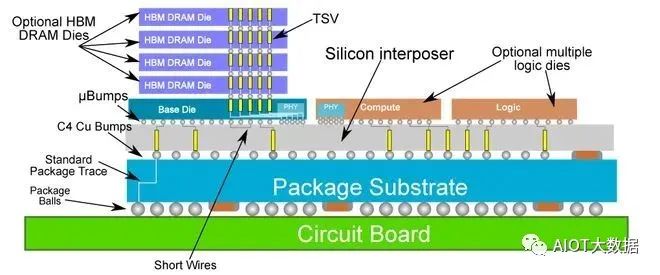

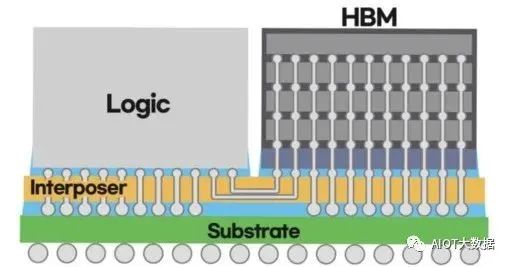

CoWoS(Chip-on-Wafer-on-Substrate)是2.5D封装技术,CoWoS是把芯片封装到硅转接板(中介层)上,并使用硅转接板上的高密度布线进行互连,然后再安装在封装基板上,如下图所示。

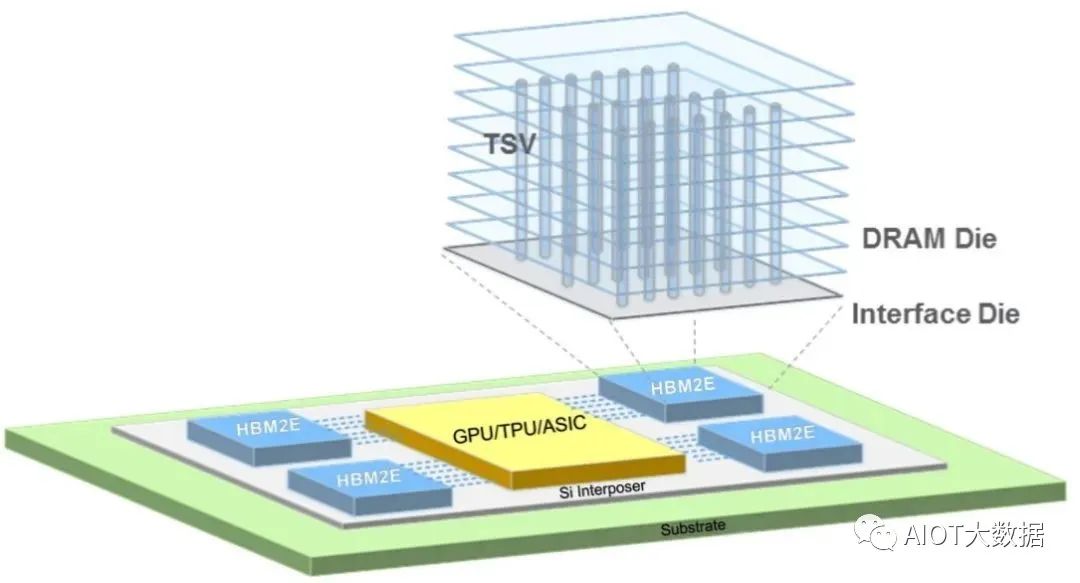

6.HBM

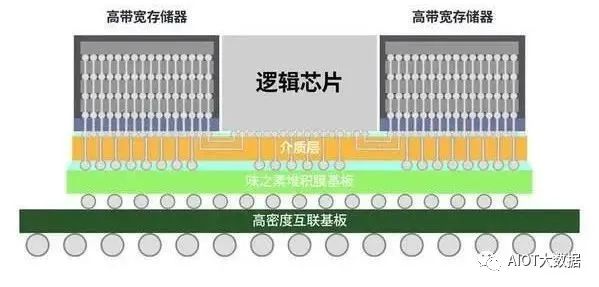

HBM(High-BandwidthMemory)高带宽内存,主要针对高端显卡市场。HBM使用了3DTSV和2.5DTSV技术,通过3DTSV把多块内存芯片堆叠在一起,并使用2.5DTSV技术把堆叠内存芯片和GPU在载板上实现互连。下图所示为HBM技术示意图。

HBM目前有三个版本,分别是HBM、HBM2和HBM2E,其带宽分别为128GBps/Stack、256GBps/Stack和307GBps/Stack,最新的HBM3还在研发中。

7.HMC

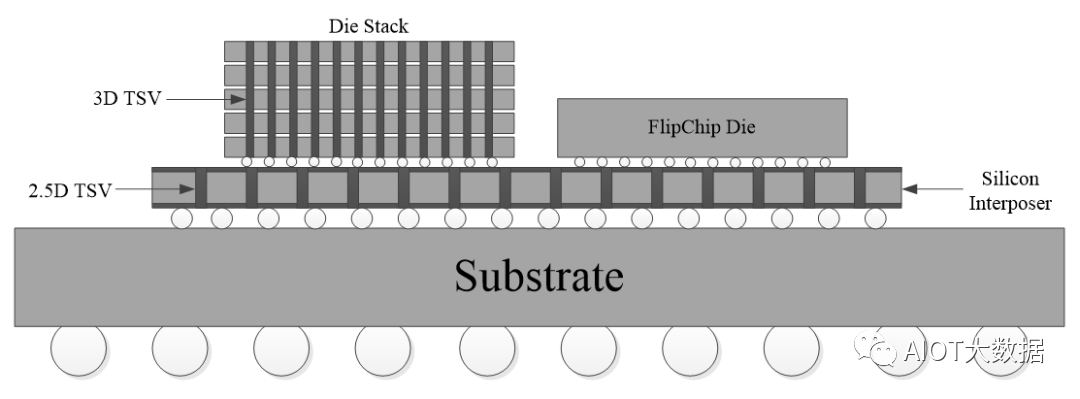

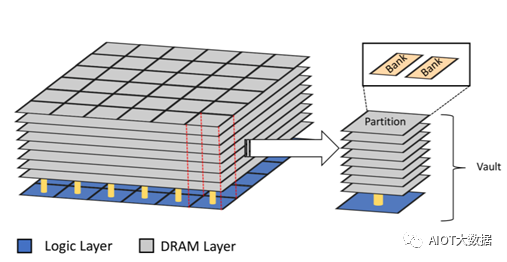

HMC(HybridMemoryCube)混合存储立方体,其标准由美光主推,目标市场是高端服务器市场,尤其是针对多处理器架构。HMC使用堆叠的DRAM芯片实现更大的内存带宽。另外HMC通过3DTSV集成技术把内存控制器(MemoryController)集成到DRAM堆叠封装里。下图所示为HMC技术示意图。

对比HBM和HMC可以看出,两者很相似,都是将DRAM芯片堆叠并通过3DTSV互连,并且其下方都有逻辑控制芯片,两者的不同在于:HBM通过Interposer和GPU互连,而HMC则是直接安装在Substrate上,中间缺少了Interposer和2.5DTSV。

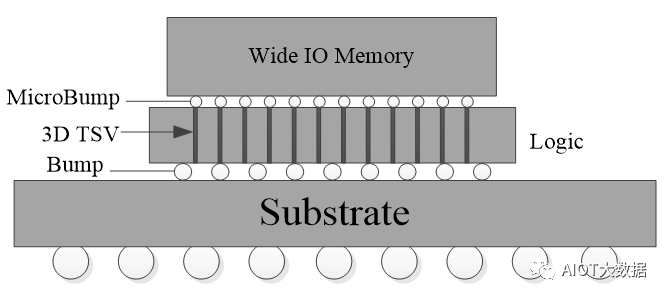

8.Wide-IO

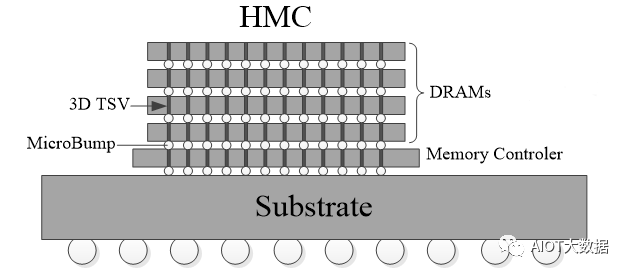

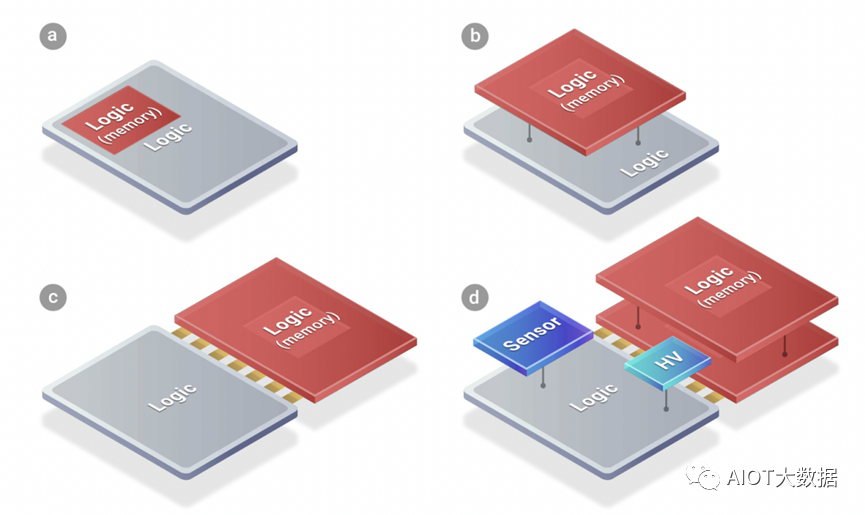

Wide-IO通过将Memory芯片堆叠在Logic芯片上来实现,Memory芯片通过3DTSV和Logic芯片及基板相连接,如下图所示。

Wide-IO具备TSV架构的垂直堆叠封装优势,有助打造兼具速度、容量与功率特性的移动存储器,满足智慧型手机、平板电脑、掌上型游戏机等行动装置的需求,其主要目标市场是要求低功耗的移动设备。

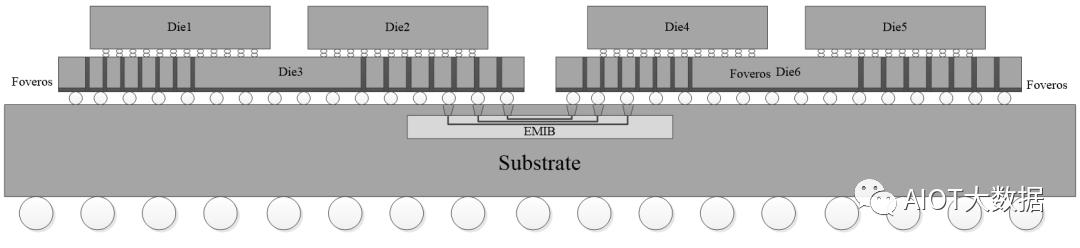

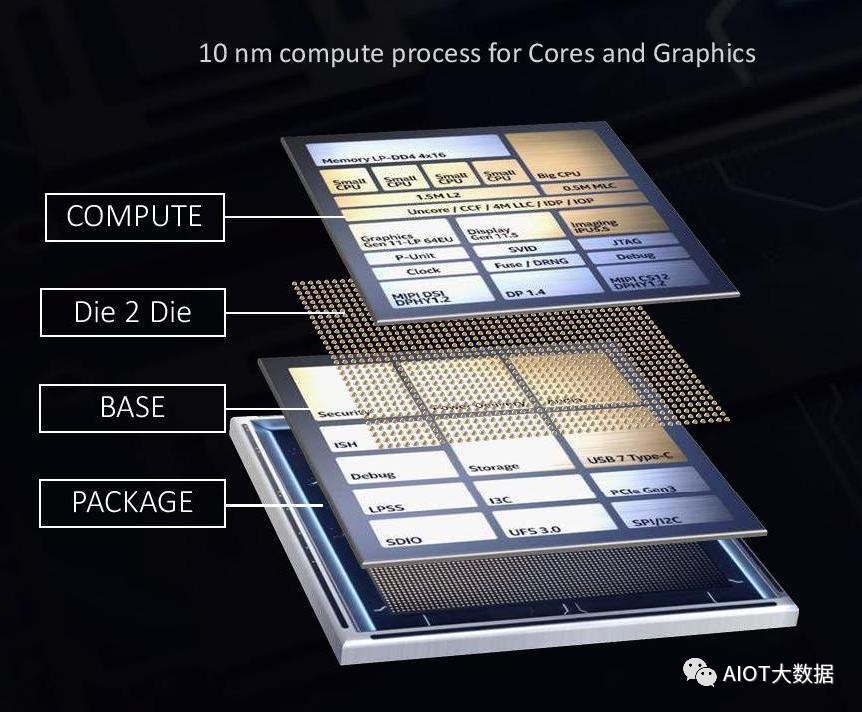

9.Foveros

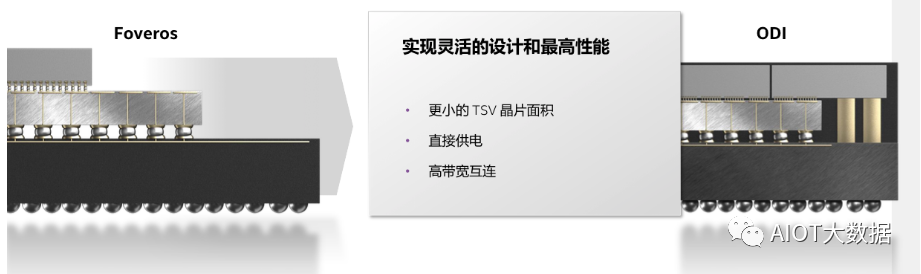

EMIB与Foveros的区别在于前者是2D封装技术,而后者则是3D堆叠封装技术,与2D的EMIB封装方式相比,Foveros更适用于小尺寸产品或对内存带宽要求更高的产品。其实EMIB和Foveros在芯片性能、功能方面的差异不大,都是将不同规格、不同功能的芯片集成在一起来发挥不同的作用。不过在体积、功耗等方面,Foveros3D堆叠的优势就显现了出来。Foveros每比特传输的数据的功率非常低,Foveros技术要处理的是Bump间距减小、密度增大以及芯片堆叠技术。下图所示是Foveros3D封装技术示意图。

首款Foveros3D堆叠设计的主板芯片LakeField,它集成了10nmIceLake处理器以及22nm核心,具备完整的PC功能,但体积只有几枚美分硬币大小。虽说Foveros是更为先进的3D封装技术,但它与EMIB之间并非取代关系,英特尔在后续的制造中会将二者结合起来使用。10.Co-EMIB(Foveros+EMIB)

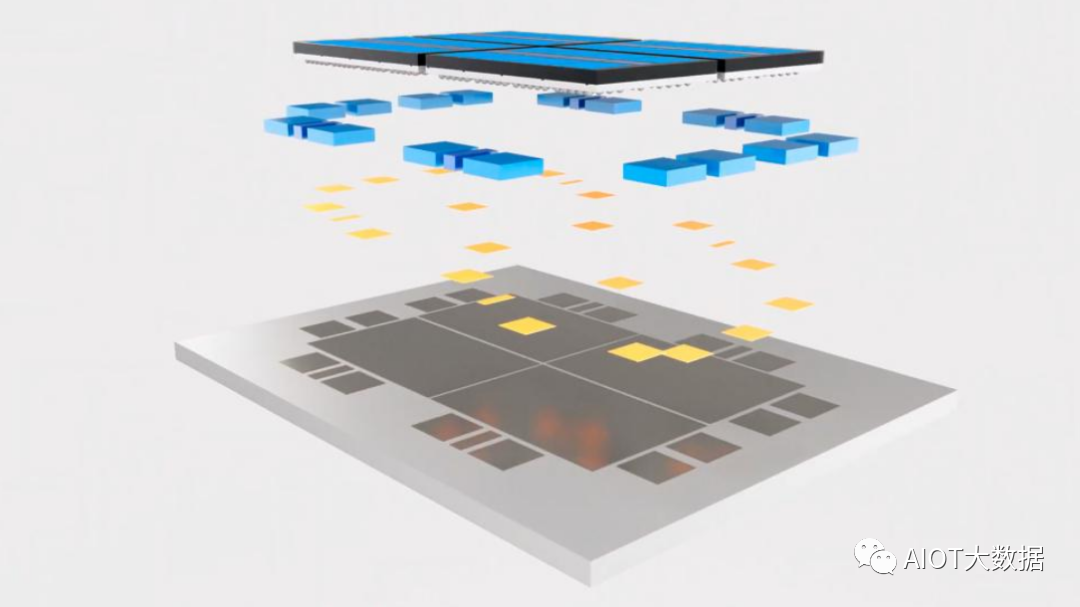

Co-EMIB是EMIB和Foveros的综合体,EMIB主要是负责横向的连结,让不同内核的芯片像拼图一样拼接起来,而Foveros则是纵向堆栈,就好像盖高楼一样,每层楼都可以有完全不同的设计,比如说一层为健身房,二层当写字楼,三层作公寓。将EMIB和Foveros合并起来的封装技术被称作Co-EMIB,是可以具有弹性更高的芯片制造方法,可以让芯片在堆叠的同时继续横向拼接。因此,该技术可以将多个3DFoveros芯片通过EMIB拼接在一起,以制造更大的芯片系统。下图是Co-EMIB技术示意图。

Co-EMIB封装技术能提供堪比单片的性能,达成这个技术的关键,就是ODI(Omni-DirectionalInterconnect)全向互连技术。ODI具有两种不同型态,除了打通不同层的电梯型态连接外,也有连通不同立体结构的天桥,以及层之间的夹层,让不同的芯片组合可以有极高的弹性。ODI封装技术可以让芯片既实现水平互连,又可以实现垂直互连。

Co-EMIB通过全新的3D+2D封装方式,将芯片设计思维也从过去的平面拼图,变成堆积木。因此,除了量子计算等革命性的全新计算架构外,CO-EMIB可以说是在维持并延续现有计算架构与生态的最佳作法。

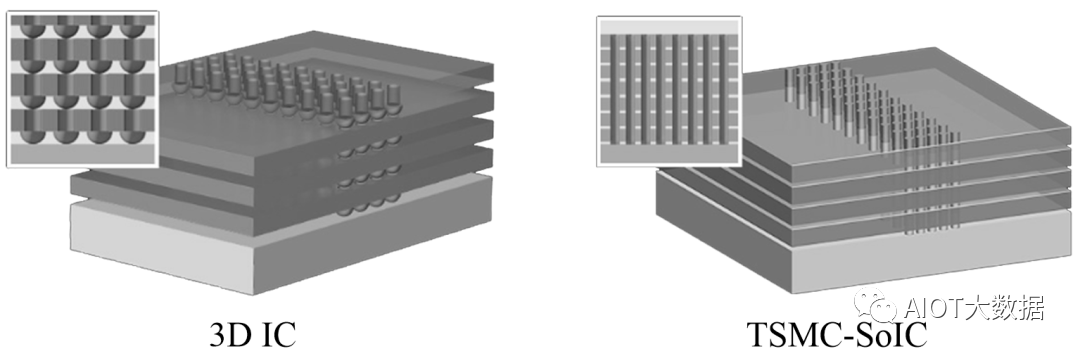

11.SoIC

SoIC也称为TSMC-SoIC,是一项新技术——集成片上系统(System-on-Integrated-Chips),预计在2021年,台积电的SoIC技术就将进行量产。究竟什么是SoIC?所谓SoIC是一种创新的多芯片堆栈技术,能对10纳米以下的制程进行晶圆级的集成。该技术最鲜明的特点是没有凸点(no-Bump)的键合结构,因此具有有更高的集成密度和更佳的运行性能。SoIC包含CoW(Chip-on-wafer)和WoW(Wafer-on-wafer)两种技术形态,从TSMC的描述来看,SoIC就一种WoW晶圆对晶圆或CoW芯片对晶圆的直接键合(Bonding)技术,属于Front-End3D技术(FE3D),而前面提到的InFO和CoWoS则属于Back-End3D技术(BE3D)。TSMC和SiemensEDA(Mentor)就SoIC技术进行合作,推出了相关的设计与验证工具。下图是3DIC和SoIC集成的比较。

具体的说,SoIC和3DIC的制程有些类似,SoIC的关键就在于实现没有凸点的接合结构,并且其TSV的密度也比传统的3DIC密度更高,直接通过极微小的TSV来实现多层芯片之间的互联。如上图所示是3DIC和SoIC两者中TSV密度和Bump尺寸的比较。可以看出,SoIC的TSV密度要远远高于3DIC,同时其芯片间的互联也采用no-Bump的直接键合技术,芯片间距更小,集成密度更高,因而其产品也比传统的3DIC有更高的功能密度。

12.X-Cube

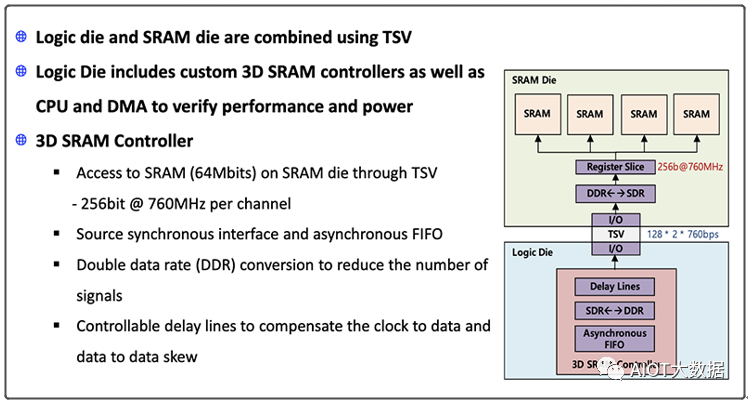

X-Cube(eXtended-Cube)是推出的一项3D集成技术,可以在较小的空间中容纳更多的内存,并缩短单元之间的信号距离。X-Cube用于需要高性能和带宽的工艺,例如5G,人工智能以及可穿戴或移动设备以及需要高计算能力的应用中。X-Cube利用TSV技术将SRAM堆叠在逻辑单元顶部,可以在更小的空间中容纳更多的存储器。从X-Cube技术展示图可以看到,不同于以往多个芯片2D平行封装,X-Cube 3D封装允许多枚芯片堆叠封装,使得成品芯片结构更加紧凑。芯片之间采用了TSV技术连接,降低功耗的同时提高了传输的速率。该技术将会应用于最前沿的5G、AI、AR、HPC、移动芯片以及VR等领域。

X-Cube技术大幅缩短了芯片间的信号传输距离,提高数据传输速度,降低功耗,并且还可以按客户需求定制内存带宽及密度。目前X-Cube技术已经可以支持7nm及5nm工艺,三星将继续与全球半导体公司合作,将该技术部署在新一代高性能芯片中。

为什么要基于Z轴延伸的先进封装技术——3D封装

一、核心结论

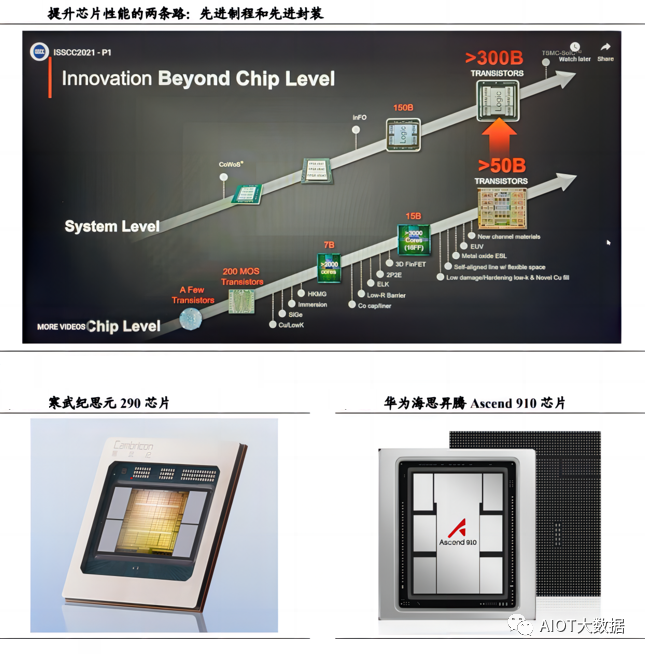

1.先进制程受限,先进封装/Chiplet提升算力,必有取舍。

在技术可获得的前提下,提升芯片性能,先进制程升级是首选,先进封装则锦上添花。

2.大功耗、高算力的场景,先进封装/Chiplet有应用价值。

3.我国先进制程产能储备极少,先进封装/Chiplet有助于弥补制程的稀缺性。

先进封装/Chiplet可以释放一部分先进制程产能,使之用于更有急迫需求的场景。

二、用面积和堆叠跨越摩尔定律限制

芯片升级的两个永恒主题:性能、体积/面积。芯片技术的发展,推动着芯片朝着高性能和轻薄化两个方向提升。而先进制程和先进封装的进步,均能够使得芯片向着高性能和轻薄化前进。面对美国的技术封装,华为难以在全球化的先进制程中分一杯羹,手机、HPC等需要先进制程的芯片供应受到严重阻碍,亟需另辟蹊径。而先进封装/Chiplet等技术,能够一定程度弥补先进制程的缺失,用面积和堆叠换取算力和性能。

先进制程受限,先进封装/Chiplet提升算力,必有取舍

三、何谓先进封装?

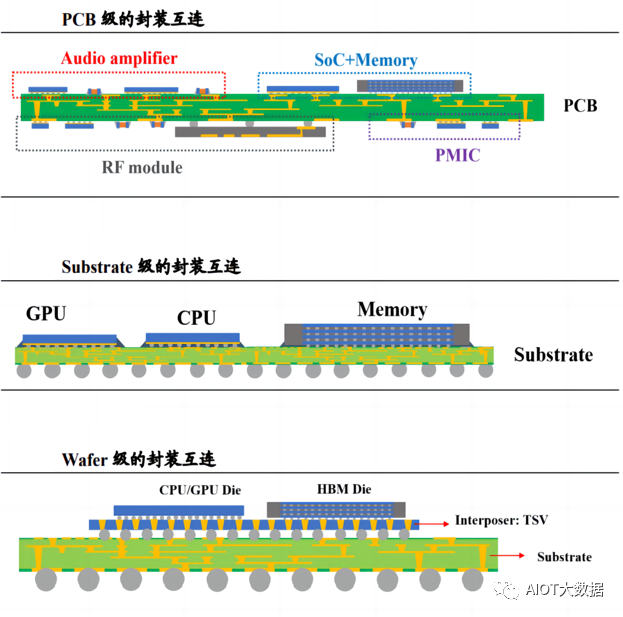

先进封装是对应于先进圆晶制程而衍生出来的概念,一般指将不同系统集成到同一封装内以实现更高效系统效率的封装技术。换言之,只要该封装技术能够实现芯片整体性能(包括传输速度、运算速度等)的提升,就可以视为是先进封装。传统的封装是将各个芯片单独封装好,再将这些单独的封装芯片装配到PCB主板上构成完整的系统,芯片间的信息交换属于PCB级的互连(interconnect),又称板级互连;或者将不同的芯片贴装到同一个封装基板Substrate上,再完成系统级的封装,芯片间的通讯属于Substrate级的互连。这两种形式的封装互连技术,芯片间的信息传输需要通过PCB或Substrate布线完成。理论上,芯片间的信息传输距离越长,信息传递越慢,芯片组系统的性能就越低。因此,同一芯片水平下,PCB级互连的整体性能比Substrate级互连的性能弱。

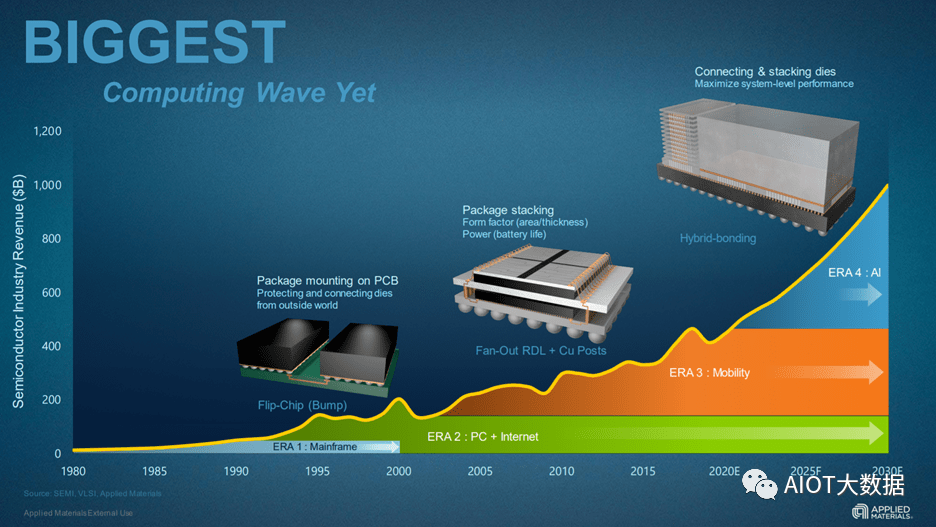

在摩尔定律失效之前,芯片系统性能的提升可以完全依赖于芯片本身制程提升(制程提升使得芯片集成晶体管数量提升)。但随着摩尔定律失效,芯片制程提升速度大大放缓,芯片系统性能的提升只能通过不断优化各个芯片间的信息传输效率,圆晶Wafer级封装互连技术的价值凸显。

Wafer级的封装互连技术,将不同的SoC集成在TSV(硅通孔技术:Throughsiliconvia)内插板(interposer)上。Interposer本身材料为硅,与SoC的衬底硅片相同,通过TSV技术以及再布线(RDL)技术,实现不同SoC之间的信息交换。换言之,SoC之间的信息传输是通过Interposer完成。Interposer再布线采用圆晶光刻工艺,比PCB和Substrate布线更密集,线路距离更短,信息交换更快,因此可以实现芯片组整体性能的提升。图XX示例为CoWoS封装(ChiponWaferonSubstrate),CPU/GPUdie与Memorydie通过interposer实现互连,信息直接通过interposer上的RDL布线传输,不经过Substrate或PCB,信息交换快,系统效率高。

从半导体制程进入10nm以来,摩尔定律已经失效,即芯片迭代不再满足“集成电路芯片上所集成的晶体管数目,每隔18个月就翻一番;微处理器的性能每隔18个月提高一倍,而价格下降一倍”。在后摩尔定律时代,对于“morethanmoore”的延续,先进封装是业界公认的有效途径。

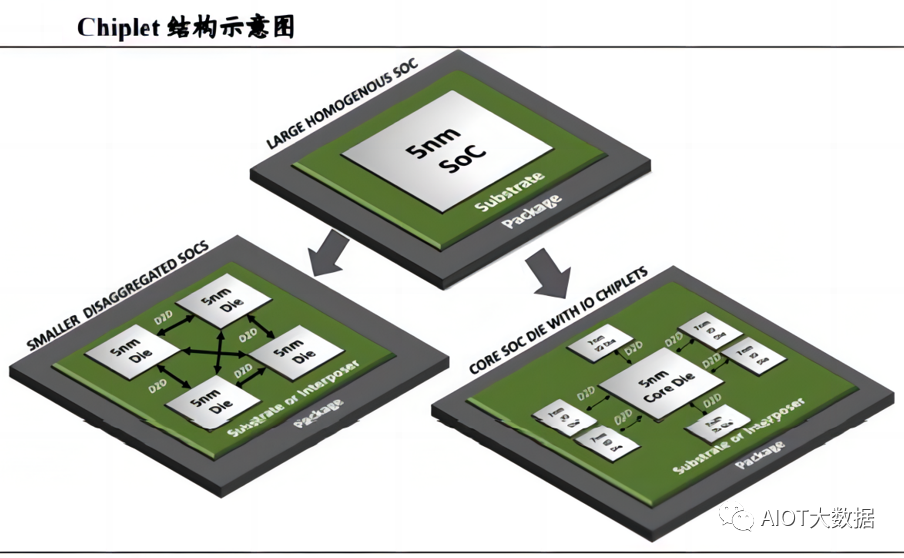

四、何谓Chiplet?

Chiplet即小芯片之意,指在晶圆端将原本一颗“大”芯片(Die)拆解成几个“小”芯片(Die),因单个拆解后的“小”芯片在功能上是不完整的,需通过封装,重新将各个“小”芯片组合起来,功能上还原原来“大”芯片的功能。Chiplet可以将一颗大芯片拆解设计成几颗与之有相同制程的小芯片,也可以将其拆解成设计成几颗拥有不同制程的小芯片。

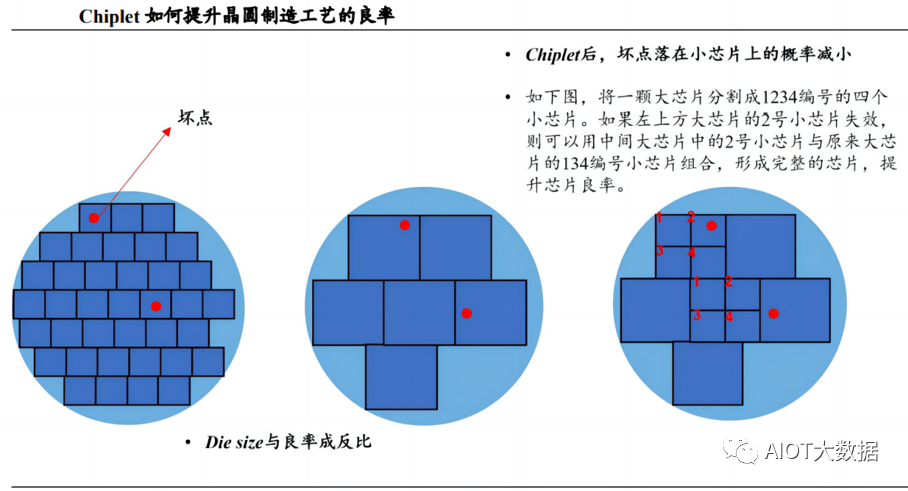

Chiplet可以提升芯片制造的良率。对于晶圆制造工艺而言,芯片面积(Diesize)越大,工艺的良率越低。可以理解为,每片wafer上都有一定概率的失效点,对于晶圆工艺来说,在同等技术条件下难以降低失效点的数量,如果被制造的芯片,其面积较大,那么失效点落在单个芯片上的概率就越大,因而良率就越低。如果Chiplet的手段,将大芯片拆解分割成几颗小芯片,单个芯片面积变小,失效点落在单个小芯片上的概率将大大降低。芯片面积Diesize与良率成反比。

五、先进制程和先进封装,对芯片性能、轻薄化的提升,孰更显著?

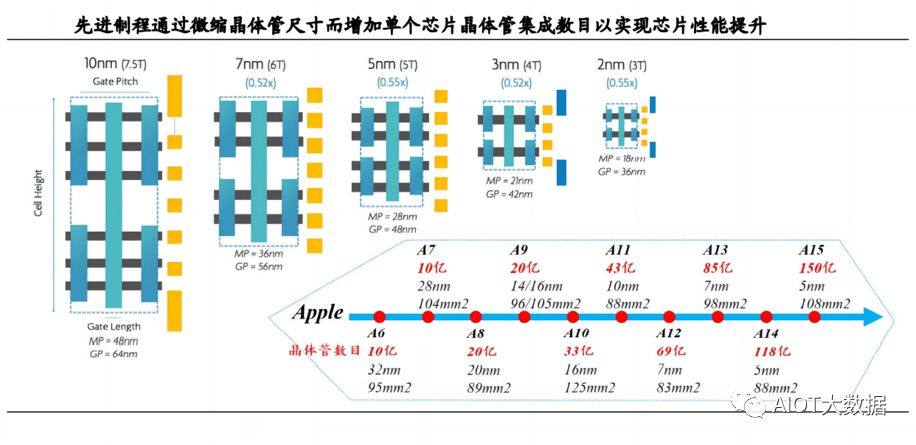

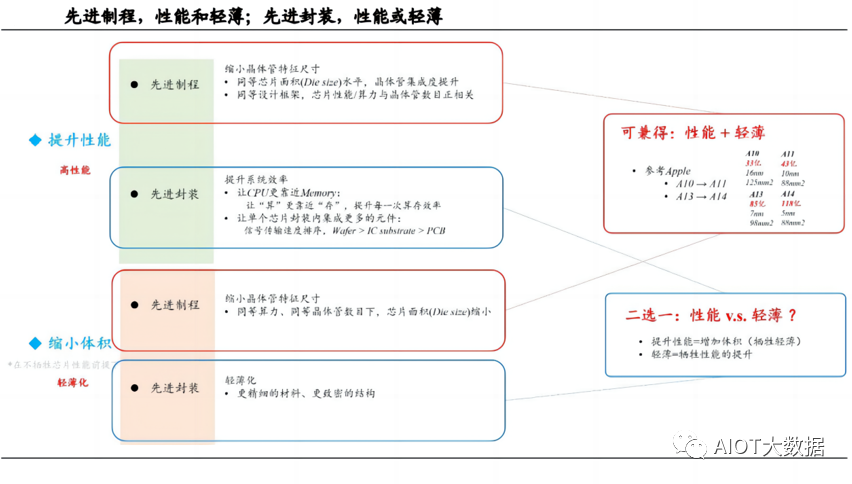

在提升芯片性能方面,先进制程路线是通过缩小单个晶体管特征尺寸,在同等芯片面积(Diesize)水平下,提升晶体管集成度(同等设计框架,芯片性能/算力与晶体管数目正相关);而先进封装并不能改变单个晶体管尺寸,只能从系统效率提升的角度,一是让CPU更靠近Memory,让“算”更靠近“存”,提升每一次计算的算存效率。二是让单个芯片封装内集成更多的元件:信号传输速度排序,Wafer>ICsubstrate>PCB,元件在芯片内部的通讯效率比在板级上更高,从系统层面提升芯片性能。

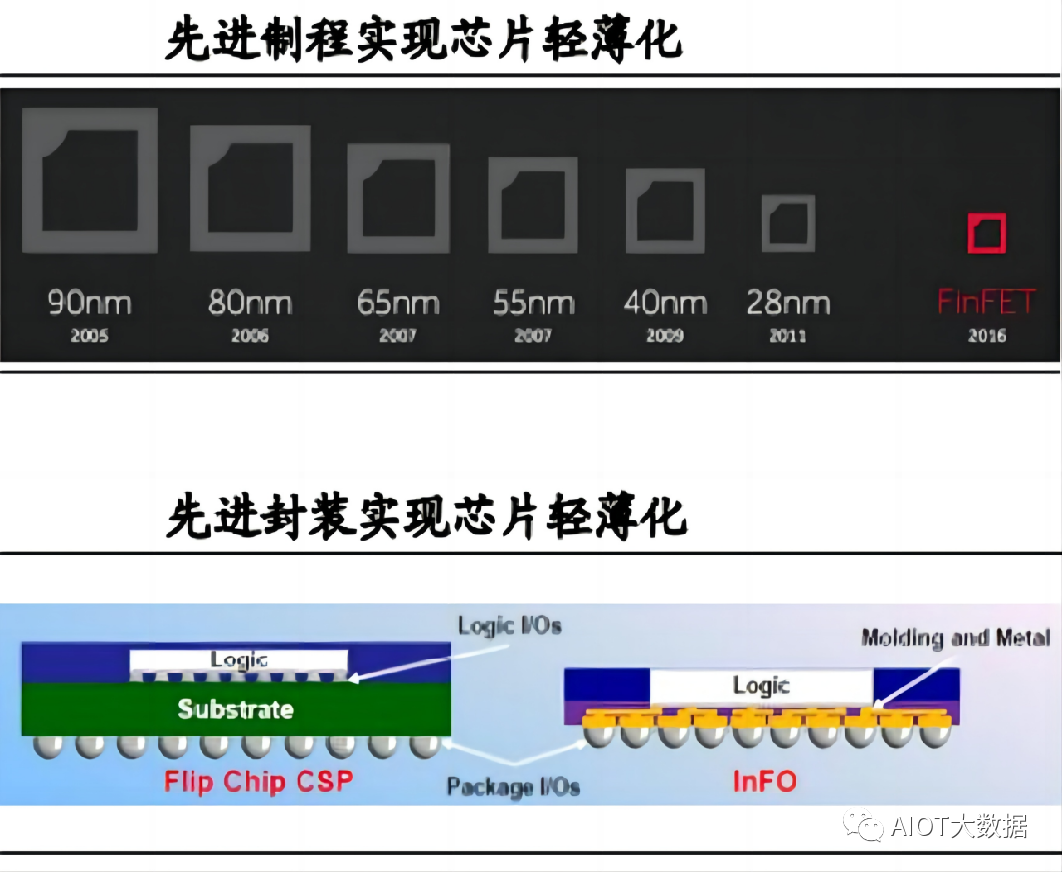

在芯片轻薄化方面,在不牺牲芯片整体性能的前提下,先进制程能够在算力和晶体管数目不变时,通过缩小单个晶体管特征尺寸,实现芯片面积(Diesize)缩小;而先进封装,因为封装对晶体管尺寸无微缩的能力,只能通过更精细的材料、更致密的结构来实现轻薄化。比如,手机AP处理器的封装多采用FCCSP的封装形式,其结构包括一个CSP载板,而Fanout(TSMC与APPLE公司合作,APPLE公司的A系列芯片多采用InFO技术封装,即Fannout)封装,取消了CSP载板(CSP载板约0.3mm厚度),封装后的芯片更轻薄,对整机(手机)结构空间余量有重要提升。

在高性能和轻薄化两个方向上,先进制程可以做到兼顾,而先进封装则有取舍。比如,APPLE的A系列芯片,从A10升级到A11时,由16nm工艺提升至10nm工艺,芯片面积从125mm2减小至88mm2,而晶体管集成数则由33亿颗增加至43亿颗;A系列芯片从A13升级到A14时,晶圆工艺从7nm升级到5nm,芯片面积从98mm2减小至88mm2,而晶体管集成数则由85亿颗增加至118亿颗,做到了性能提升和轻薄化的兼顾。而先进封装,要做到芯片性能提升,因为封装对晶体管尺寸微缩没有效果,提升性能一是增加芯片内部各元件的协作效率,二是往一个系统中堆叠更多的元件(本质上也是提升了系统内的晶体管数据),代价就是系统体积、面积更为庞大,即先进封装提升性能的代价是牺牲轻薄,实现轻薄的代价是牺牲性能的提升。

在技术可获得的前提下,提升芯片性能,先进制程升级是首选,先进封装则锦上添花。通常我们可以见到的是,高性能、大算力的芯片,会考虑上先进封装(2.5D、CoWoS等),但这些大算力芯片往往也同时采用的先进制程工艺,也就是说,先进封装/Chiplet应用通常只出现在顶级的旗舰芯片的封装方案选择中,并不是一个普适性的大规模应用方案。比如寒武纪的7nmAI训练芯片思元290,从芯片宣传图片可以看出,其可能采用“1+4”架构,即1颗CPU/GPU搭配4颗HBM存储的Chiplet封装形式,该芯片也是寒武纪的旗舰芯片产品之一;华为海思昇腾910芯片,采用7nm的先进制程工艺,从宣传图可以看出,也是采用了多颗芯片堆叠的CoWoS结构,也系Chiplet的一种形式。这些芯片都是在拥有先进制程的基础上,为了进一步提升芯片性能,而采用了CoWoS这些2.5D先进封装技术,说明了先进制程在工艺路线的选择上是优于先进封装的,先进制程是升级芯片性能的首选,先进封装则是锦上添花。

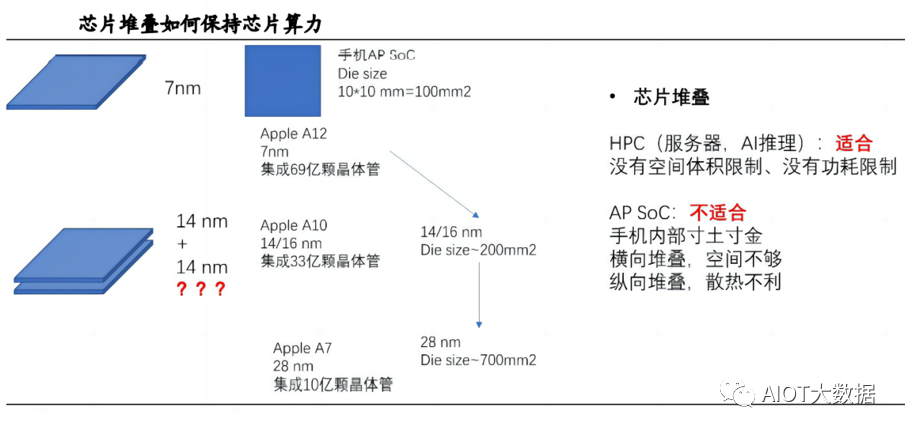

五.大功耗、高算力的场景,先进封装/Chiplet有应用价值

在先进制程不可获得的情况下,通过芯片堆叠(先进封转/Chiplet)和计算架构重构,以维持产品性能。以APPLE的A系列芯片参数为例,A12、A10、A7芯片分别采用7nm、14/16nm(Samsung14nm、TSMC16nm)、28nm制程。A系列的手机AP芯片,通常芯片面积(DieSize)在约100mm2大小。在这100mm2大小的芯片上,A12、A10、A7芯片分别集成了约69亿、33亿、10亿颗晶体管。下面,我们简单进行算术换算,讨论降制程如何维持芯片的算力。如果芯片工艺从7nm降至14nm,A12芯片上7nm工艺集成69亿颗晶体管,如果用14nm工艺以试图达到接近的算力,首先要保证晶体管数目与A12芯片一致,即~70亿颗,且在未考虑制程提升对单个晶体管性能有显著提升的背景下,14nm工艺的芯片需要两倍于7nm工艺的面积,即~200mm2;如果芯片工艺从7nm降至28nm,参考28nm的A7芯片只集成了10亿颗晶体管,如果要达到70亿晶体管数目,则需要将芯片面积扩大至~700mm2。芯片面积越大,工艺良率越低,在实际制造中得到的单颗芯片的制造成本就越高,因此,在先进制程不可获得的背景下,降制程而通过芯片堆叠的方式,的确可以一定程度减少算力劣势,但是因为堆叠更多芯片,需要更大的IC载板、更多的Chiplet小芯片、更多的封装材料,也导致因为制程落后带来的功耗增大、体积/面积增加、成本的增加。因此,比如,通过14nm的两颗芯片堆叠,去达到同样晶体管数目的7nm芯片性能;通过多颗28nm的芯片堆叠,去达到14nm芯片性能。此种堆叠方案在HPC(服务器、AI推理)、基站类大芯片领域可能有适用价值,但对于消费电子领域如手机AP芯片和可穿戴芯片,在其应用场景对空间体积有严苛约束的条件下,芯片堆叠则较难施展。

六.我国先进制程产能储备极少,先进封装/Chiplet有助于弥补制程的稀缺性

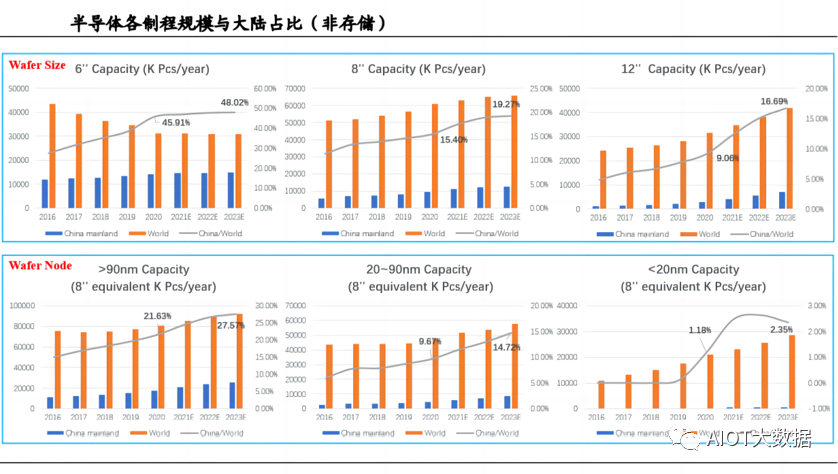

尖端科技全球化已死,大陆先进制程的产能极为稀缺、紧缺。按不同晶圆尺寸统计,大陆6英寸晶圆产能已占全球近一半,而12英寸产能仅为全球约10%。按不同制程统计,大陆90nm以上制程占全球约20%,20-90nm制程占全球约10%,20nm以下制程仅占全球约1%。大陆高端制程占比低,产业结构存在明显短板,未来扩产空间大。高端制程扩产投入大,3nm制程芯片每万片产能的投资约100亿美元,远高于28nm制程芯片每万片约7亿美元的投资。弥补大陆晶圆产业结构短板,需重点投资高端制程晶圆制造产能,既需要完成技术攻关,又需要大额投资支持,任重而道远。

先进封装/Chiplet可以释放一部分先进制程产能,使之用于更有急迫需求的场景。从上文分析可见,通过降制程和芯片堆叠,在一些没有功耗限制和体积空间限制、芯片成本不敏感的场景,能够减少对先进制程的依赖。可以将当下有限的先进制程产能,以更高的战略视角,统一做好规划,应用在更需要先进工艺的应用需求中。

3D先进封装产业格局

Chiplet:芯片异构在制造层面的效率优化

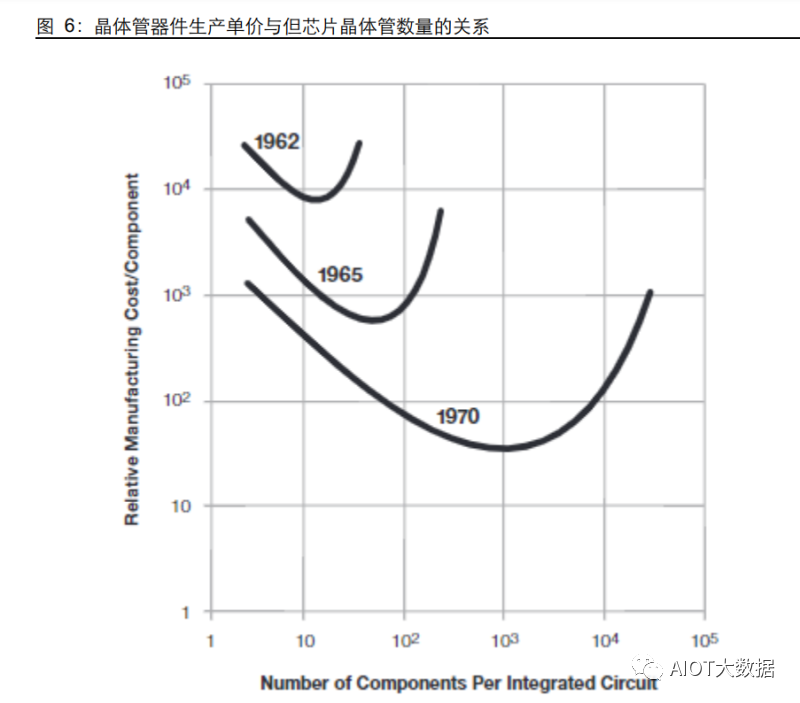

实际上,Chiplet最初的概念原型出自GordonMoore1965年的论文《Crammingmorecomponentsontointegratedcircuits》;GordonMoore在本文中不仅提出了著名的摩尔定律,同时也指出“用较小的功能构建大型系统更为经济,这些功能是单独封装和相互连接的”。2015年,Marvell周秀文博士在ISSCC会议上提出MoChi(ModularChip,模块化芯片)概念,为Chiplet的出现埋下伏笔。我们认为,现代信息技术产业的发展不是探索未知的过程,而是需求驱动技术升级,Chiplet技术的出现是产业链在生产效率优化需求下的必然选择。

Chiplet的基础:异构与高速互联共同塑造的里程碑

计算机能够根据一系列指令指示并且自动执行任意算术或逻辑操作串行的设备。日常生活中,我们所使用的任何电子系统都可以看作一个计算机,如:电脑、手机、平板乃至微波炉、遥控器等都包含了计算机系统作为核心控制设备。Chiplet出现离不开两个大的趋势:

1)计算机系统的异构、集成程度越来越高

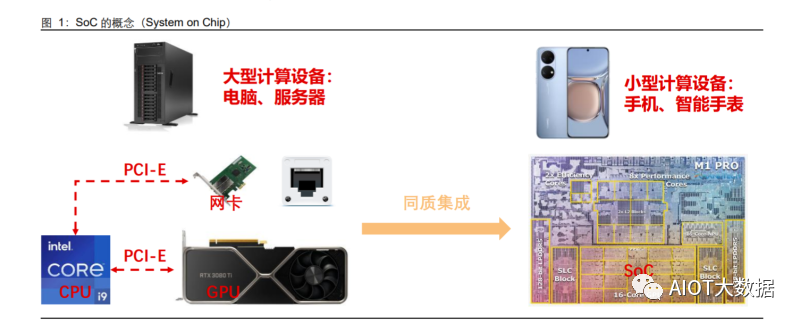

为了便于理解产业界为何一定要选择Chiplet,本报告从计算机体系结构的角度出发,本报告将首先理清计算机体系结构的一个重要发展思路——异构计算。如同现代经济系统一样,现代经济系统为了追求更高的产出效率,产生了极为庞大且复杂的产业分工体系,计算机系统的再分工就是异构计算。GPU、DPU的出现就是为了弥补CPU在图形计算、数据处理等方面的不足,让CPU能够专注于逻辑的判断与执行,这就是计算机系统(System)。精细化的分工也使得整个体系变得庞大,小型计算设备中只能将不同的芯片集成到一颗芯片上,组成了SoC(SystemonChip)。

伴随着计算机在人类现代生活中承担越来越多的处理工作,计算机体系结构的异构趋势会愈发明显,需要的芯片面积也会越来越大,同时也需要如电源管理IC等芯片与逻辑芯片异质集成,而SoC作为一颗单独的芯片,其面积和加工方式却是受限的,所以SoC并不是异构的终极解决方案。

2)芯片间的数据通路带宽、延迟问题得到了产业界的解决

芯片的工作是执行指令,处理数据,芯片间的互联需要巨大的带宽和超低的延时。既然单颗芯片的面积不能无限增加,将一颗芯片拆解为多颗芯片,分开制造再封装到一起是一个很自然的想法。芯片间的互联需要构建强大的数据通路,即超高的频率、超大的带宽、超低的延时,以台积电CoWoS技术为代表的先进封装技术也使之得到了解决。

2022年3月,Apple发布了M1Ultra芯片,其采用了UltraFusion封装架构,通过两枚M1Max晶粒的内部互连。架构上,M1Ultra采用了20核中央处理器,由16个高性能核心和4个高能效核心组成。与市面上功耗范围相近的16核CPU芯片相比,M1Ultra的性能高出90%。两颗M1Max的高速互联是苹果芯片实现领先的关键,苹果的UltraFusion架构利用硅中介层来连接多枚芯片,可同时传输超过10,000个信号,从而实现高达2.5TB/s低延迟处理器互联带宽。AMD为缓解“存储墙”问题,在其Zen3架构的锐龙75800X3D台式处理器率先采用3D堆叠L3高速缓存,使CPU可访问高达96MBL3级高速缓存,大幅提升芯片运算效率。

3)异构集成+高速互联塑造了Chiplet这一芯片届的里程碑

综上,Chiplet本身并非技术突破,而是多项技术迭代进步所共同塑造的里程碑,芯片龙头企业仍拥有话语权;因此,Chiplet技术短期内并不会给行业带来太多直接的影响和变化,但长期来看必将改变全球集成电路行业生态。同时,由于Chiplet在设计、制造、封装等多个环节具备成熟的技术支撑,其推进也将十分迅速。

Chiplet的需求:设计、生产环节的效率优化

技术服务于需求,Chiplet的出现,缓解了算力对晶体管数量的依赖与晶圆制造端瓶颈的矛盾。如前文所言,导致Chiplet技术出现的需求决定了它对行业产生的影响大小。随着现代数据处理任务对算力需求的不断提高,本质上,算力提升的核心是晶体管数量的增加。作为Intel的创始人之一,GordonMoore在最初的模型中就指明,无论是从技术的角度还是成本的角度来看,单一芯片上的晶体管数量不能无限增加;因此,业内在致力于提升晶体管密度的同时,也在尝试其他软硬件方式来提高芯片运行效率,如:异构计算、分布式运算等等。

Chiplet是异构计算的延申,主要解决了芯片制造层面的效率问题。随着制程缩进,芯片制造方面出现了两个大的瓶颈:1)28nm以后,高制程芯片的晶体管性价比不再提升;2)芯片设计费用大幅增长,先进制程芯片设计的沉没成本高到不可接受。

关于Chiplet如何提高设计、生产环节的效率,以及对EDA、IC设计等行业的影响,我们在此前的报告《Chiplet技术:成长新至,换道前行》中进行了深入的探讨:(1)基于小芯片的面积优势,Chiplet可以大幅提高大型芯片的良率、提升晶圆面积利用效率,降低成本;(2)基于芯片组成的灵活性,将SoC进行Chiplet化之后,不同的核心/芯粒可以选择合适的工艺制程分开制造,然后再通过先进封装技术进行封装,不需要全部都采用先进的制程在一块晶圆上进行一体化制造,这样可以极大的降低芯片的制造成本;(3)基于小芯片IP的复用性和已验证特性,将大规模的SoC按照不同的功能模块分解为模块化的芯粒,减少重复的设计和验证环节,可以降低设计的复杂度和设计成本,提高产品迭代速度。

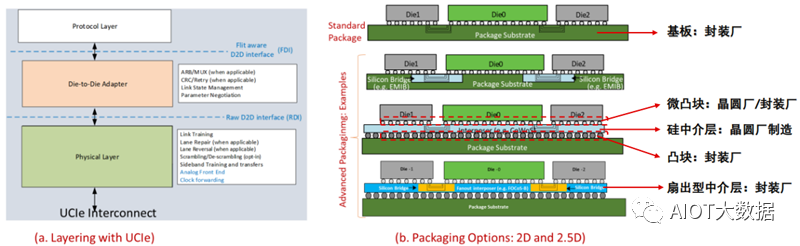

Chiplet的封装:核心是实现高速互联

Chiplet封装领域,目前呈现出百花齐放的局面。Chiplet的核心是实现芯片间的高速互联,同时兼顾多芯片互联后的重新布线。因此,UCIE联盟在具体的封装方式上未对成员做出严格限制,根据UCIE联盟发布的Chiplet白皮书,UCIE联盟支持了市面上主流的四种封装方式,分别为:1)标准封装:将芯片间的金属连线埋入封装基板中。2)利用硅桥连接芯片,并将硅桥嵌入封装基板中,如:IntelEMIB方案。3)使用硅中介层(SiInterposer)连接芯片并进行重新布线,再将硅中介层封装到基板上,如:台积电CoWoS方案。4)使用扇出型中介层进行重布线,仅在芯片连接处使用硅桥连接,如:日月光FOCoSB方案。

目前而言,台积电凭借其在晶圆代工领域的优势,其CoWoS技术平台已服务多家客户,也迭代了多个批次,初具雏形:台积电CoWoS平台的核心在于硅中介层,其生产主要通过在硅片上刻蚀TSV通孔实现,技术难点主要实现高深宽比的通孔和高密度引脚的对齐。Die与Interposer生产好之后,交由封装厂进行封装。我们认为,Chiplet在封装层面的技术核心是作为芯片间的互联,其能够实现的芯片间数据传输速度、延迟是技术竞争力的关键,同时方案的稳定性、普适性也将深刻影响其长期的发展空间。

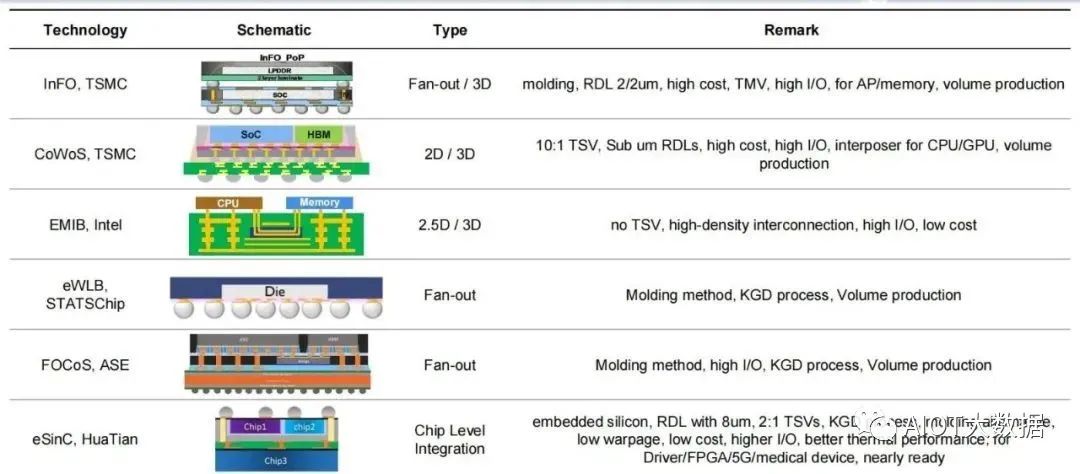

全球格局:两大阵营,群雄逐鹿

实现Chiplet所依靠的先进封装技术在产业链内仍然未实现统一,主要分为晶圆厂阵营和封装厂阵营:晶圆厂阵营以硅片加工实现互联为主,可提供更高速的连接和更好的拓展性;封装厂阵营则努力减少硅片加工需求,提出更有廉价、更有性价比的方案。

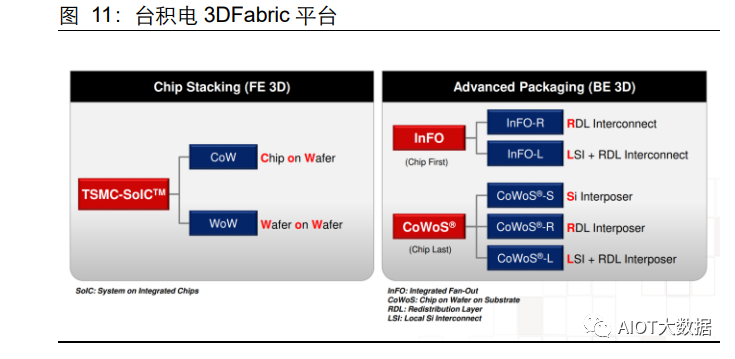

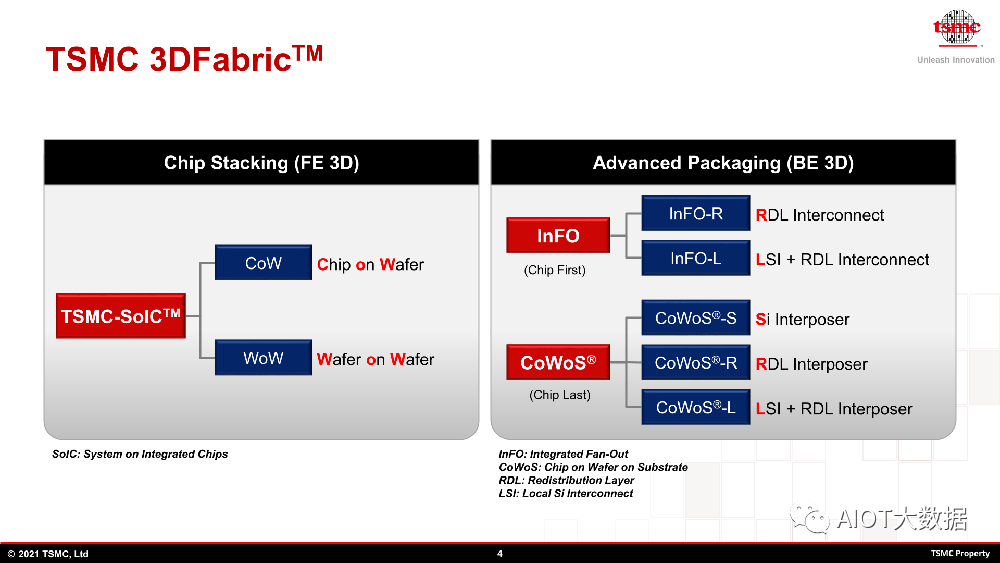

台积电:整合3DFabric平台,实现丰富拓扑结构组合

在2.5D和3D先进封装技术方面,台积电已将2.5D和3D先进封装相关技术整合为“3DFabric”平台,由客户自由选配,前段技术包含3D的整合芯片系统(SoICInFO3D),后段组装测试相关技术包含2D/2.5D的整合型扇出(InFO)以及2.5D的CoWoS系列家族。

台积电更先进的垂直芯片堆叠3D拓扑封装系列被称为“系统级集成芯片”(SoIC),利用芯片之间的直接铜键合,具有更小间距。

三星:3DIC封装方案强化Chiplet代工产业布局

2020年8月,三星公布了XCube3D封装技术(全称为extendedcube,意为拓展立方体)。在芯片互连方面,使用了成熟的硅通孔TSV工艺。目前XCube已经能把SRAM芯片堆叠在三星生产的7nmEUV工艺的逻辑芯片上,这样可以更易于扩展SRAM的容量,同时也缩短了信号连接距离,以提升数据传输的速度和提高能效。此后发布I-Cube将一个或多个逻辑die和多个HBMdie水平放置在硅中介层,进行异构集成。

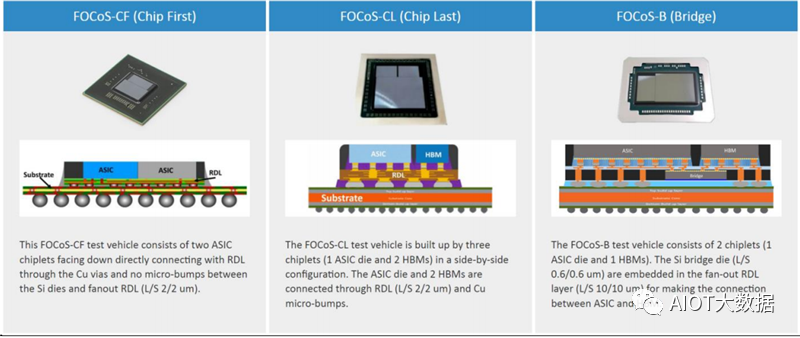

日月光:FOCoS方案力争减硅,降低成本

日月光的FOCoS提供了一种用于实现小芯片集成的硅桥技术,称为FOCoS-B(桥),它利用带有路由层的微小硅片作为小芯片之间的封装内互连,例如图形计算芯片(GPU)和高带宽内存(HBM)。硅桥嵌入在扇出RDL层中,是一种可以不使用硅中介层的2.5D封装方案。FOCoS的硅桥在封装中提供超细间距互连,可以解决系统中的内存带宽瓶颈挑战。与使用硅中介层的2.5D封装相比,FOCoS-B的优势在于只需要将两个小芯片连接在一起的区域使用硅片,可大幅降低成本。

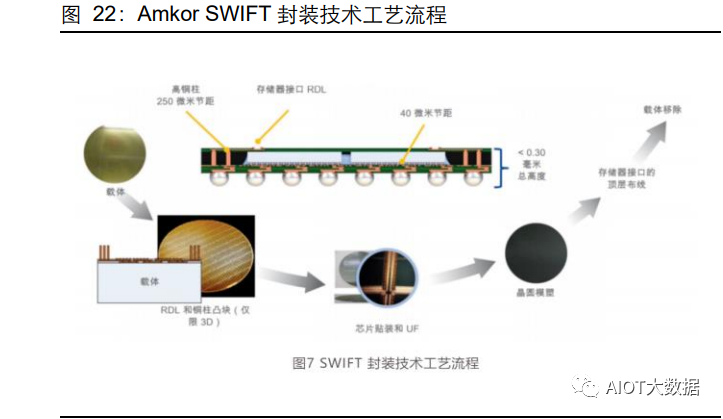

Amkor:深度布局TSV-less工艺

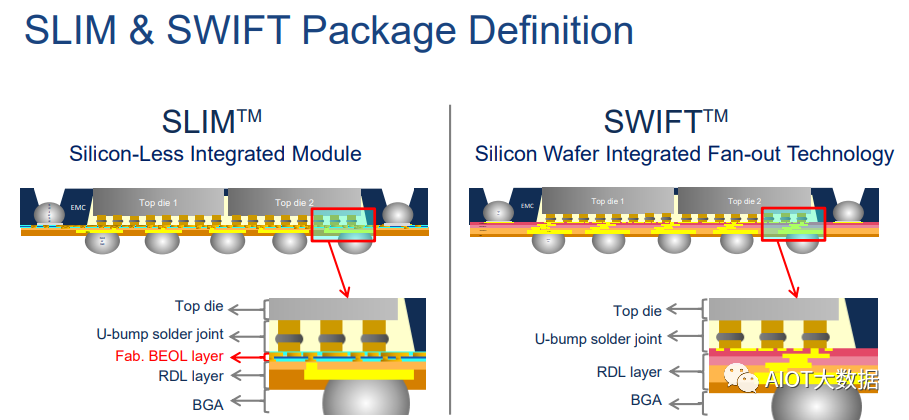

Amkor方面,公司2015年推出SLIM及SWIFT解决方案;且持续进行技术布局,具备2.5D/3DTSV封装能力。

TSV-less工艺可被用于建立先进3D结构。SLIM及SWIFT方案均采用TSV-less工艺,简化了2.5DTSV硅中介层运用时PECVD及CMP工序。以SWIFT(SiliconWaferIntegratedFan-OutTechnology)方案为例,方案采用RDLfirst技术,RDL线宽线距能力≤2um,μbumppitch40um,SWIFT封装可实现多芯片集成的3DPOP封装以及无需TSV(TSV-Less)具有成本优势的HDFO高密度扇出型封装,适用于高性能CPU/GPU,FPGA,MobileAP以及MobileBB等。3DSWIFT的独特特性要部分归功于与此项创新晶圆级封装技术相关的小间距功能。它使应用积极主动的设计规则成为现实,有别于传统的WLFO和基于层压板的封装,且能够被用于建立先进的3D结构,以应对新兴移动和网络应用中日益高涨的IC集成需求。

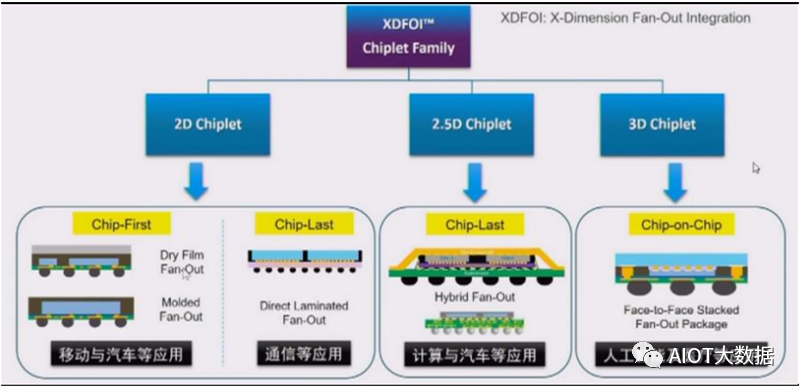

长电科技:国内封装龙头,TSV-less路线引领

长电科技聚焦关键应用领域,在5G通信类、高性能计算、消费类、汽车和工业等重要领域拥有行业领先的半导体先进封装技术(如SiP、WL-CSP、FC、eWLB、PiP、PoP及XDFOI系列等)以及混合信号/射频集成电路测试和资源优势,并实现规模量产,能够为市场和客户提供量身定制的技术解决方案。

XDFOI方案:TSV-less路线实现高性价比Chiplet封装

面向Chiplet异构集成应用推出XDFOI封装解决方案,涵盖2D/2.5D/3D集成技术。在2.5/3D集成技术领域,长电科技积极推动传统封装技术的突破,率先在晶圆级封装、倒装芯片互连、TSV等领域中采用多种创新集成技术,以开发差异化的解决方案。公司于2021年7月推出了XDFOI全系列极高密度扇出型封装解决方案,该技术是一种面向Chiplet应用的极高密度、多扇出型封装高密度异构集成解决方案,包括2D/2.5D/3D集成技术,能够为客户提供从常规密度到极高密度,从极小尺寸到极大尺寸的一站式服务。

XDFOI方案预计于2022H2实现量产,相比2.5DTSV,XDFOI具备更高性能、更高可靠性以及更低成本等特性。XDFOI为一种以2.5DTSV-less为基本技术平台的封装技术,在设计上,该技术可实现3-4层高密度的走线,其线宽/线距最小可达2μm,可实现多层布线层,另外,采用了极窄节距凸块互联技术,封装尺寸大,可集成多颗芯片、高带宽内存和无源器件。长电科技已完成超高密度布线并开始客户样品流程,预计2022H2量产,重点应用领域为高性能运算如FPGA、CPU/GPU、AI、5G、自动驾驶、智能医疗等。长电科技的无硅通孔扇出型晶圆级高密度封装技术,可在硅中介层(SiInterposer)中使用堆叠通孔技术(StackedVIA)替代TSV技术。该技术可以实现多层RDL再布线层,2×2um的线宽间距,40um极窄凸块互联,以及多层芯片叠加。

此外,XDFOI技术所运用的极窄节距凸块互联技术,还能够实现44mm×44mm的封装尺寸,并支持在其内部集成多颗芯片、高带宽内存和无源器件。这些优势可为芯片异构集成提供高性价比、高集成度、高密度互联和高可靠性的解决方案。

先进封测技术涵盖4nm制程,突破国内顶尖封装工艺节点。长电科技2022年7月公告在进封测技术领域取得新的突破,实现4nm工艺制程手机芯片的封装,以及CPU、GPU和射频芯片的集成封装。4nm芯片作为先进硅节点技术,也是导入Chiplet封装的一部分,作为集成电路领域的顶尖科技产品之一,可被应用于智能手机、5G通信、人工智能、自动驾驶,以及包括GPU、CPU、FPGA、ASIC等产品在内的高性能计算领域。

通富微电:绑定AMD,晶圆级封装助力Chiplet

针对Chiplet,通富微电提供晶圆级及基板级封装两种解决方案,其中晶圆级TSV技术是Chiplet技术路径的一个重要部分。WLP晶圆级封装大部分工艺是对晶圆进行整体封装,封装完成后再进行切割分片。晶圆级封装是通过芯片间共享基板的形式,将多个裸片封装在一起,主要用于高性能大芯片的封装,利用次微米级硅中介层以TSV技术将多个芯片整合于单一封装中,能够显著降低材料成本,利用无载片技术,在芯片到晶圆键合与缝隙填充之后,整个晶圆由于背侧硅穿孔露出而进行覆盖成型与翻转,并直接由环氧模型树脂维持。

3D先进封装技术大战还在继续

与传统封装相比,先进封装不仅能突破先进制程所不能达到的性能,还可以在技术路线上实现多样化、灵活性和创新,使得晶圆代工厂、IDM、OSAT创造融合出各具商标代号的先进封装解决技术与平台。

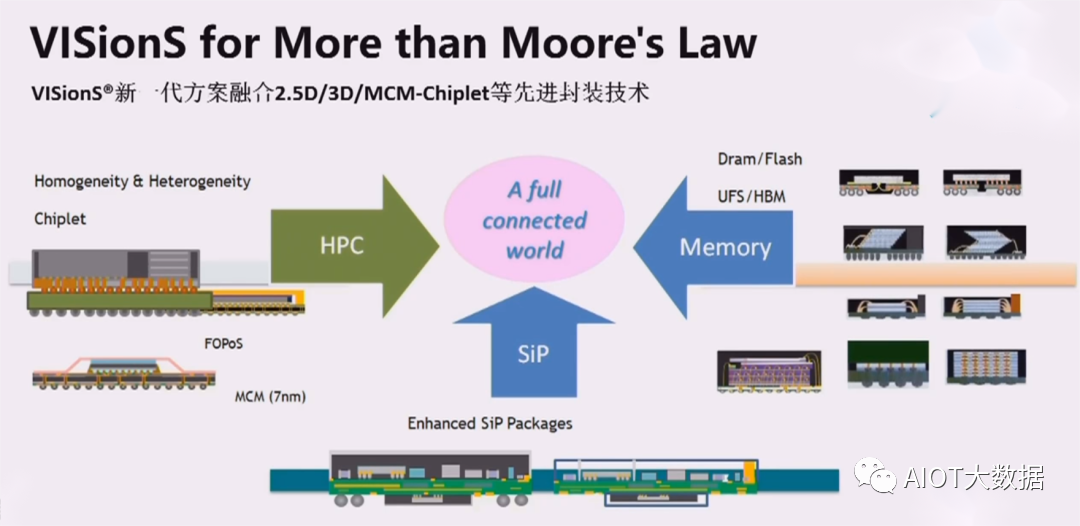

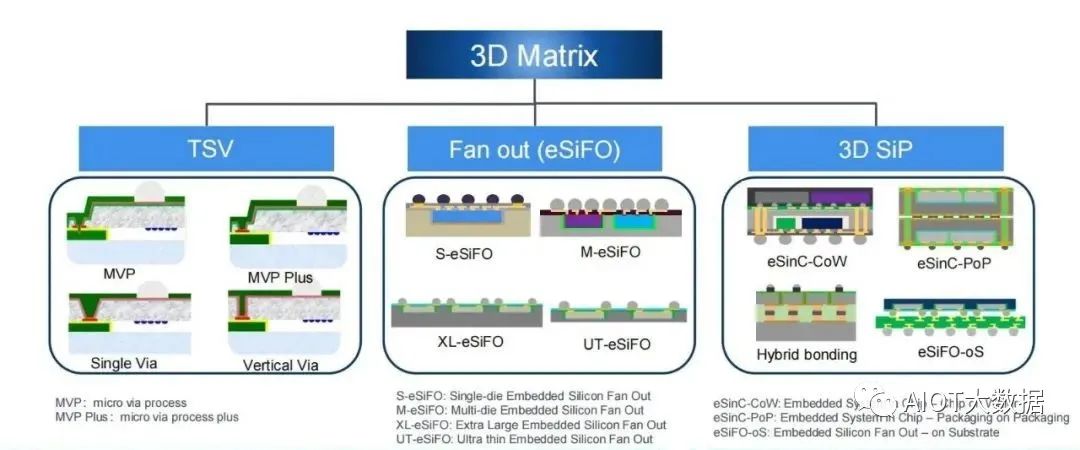

中国大陆的三大封装厂在近两年先后推出了业界为之一傲的先进封装技术与平台。长电科技推出全系列极高密度扇出型封装解决方案——XDFOI,通富推出融合了2.5D、3D、MCM-Chiplet等技术的先进封装平台——VISionS;华天推出了由TSV、eSiFo、3DSiP构成的最新先进封装技术平台——3DMatrix。

先进封装技术实例图源:CSPT2022

另一头,日月光将其六大核心封装技术整合为VIPack先进封装平台,提供垂直互连整合封装解决方案;台积电推出CoWoS作为高端先进封装平台,涉及SiInterposer进行异构集成,开发了InFO、SoIC、3DSoW等一系列系统集成技术;Intel相继开发了EMIB、Foveros、Co-EMIB架构,其先进的3DIC为HPC和5G生态提供解决方案,继而推出了基于小芯片的架构方法…各大厂先进封装技术之争从未平息,争先抢占新兴和未来应用市场,诸神之战烽火狼烟。

封装与互联方式的演变历程图源:CSPT2022

XDFOI

XDFOI是长电科技2021年7月推出全系列极高密度扇出型封装解决方案,以2.5D无TSV为基本技术平台,具备成本优势,可以实现2D/2.5D/3D集成方案。该封装解决方案是新型无硅通孔晶圆级极高密度封装技术,相较于2.5D硅通孔(TSV)封装技术,具备更高性能、更高可靠性以及更低成本等特性。该解决方案在线宽或线距可达到2um的同时,可实现多层布线层,另外,采用了极窄节距凸块互联技术,封装尺寸大,可集成多颗芯片、高带宽内存和无源器件。

XDFOI主要集中于对集成度和算力有较高要求的FPGA、CPU、GPU、AI和5G网络芯片等应用产品提供小芯片(Chiplet)和异质封装(HiP)的系统封装解决方案。

XDFOI2.5D技术特征图源:长电科技

VISionS

通富微电在CSPT2021中国半导体封装测试技术与市场年会上,介绍了其代号为VISionS的先进封装平台,融合了2.5D、3D、MCM-Chiplet等先进封装技术。一方面基于HPC应用,将同构与异构的Chiplet、FOPos、MCM从不同角度进行先进封装得到最佳的计算性能;另一方面,发挥SiP产品特色,在双面上进行高密度集成。基于SiP技术,融合waferleve、2.5D为客户提供最佳性能产品。另加上在DramFlash、UFEHBM等存储方向布局,以适应新一代高频、高速、大容量存储芯片的需求。

图源:CSPT2021

3DMatrix

2022年11月15日,华天科技在CSPT2022中国半导体封装测试技术与市场年会上,介绍了其最新的3DMatrix。该平台由TSV、eSiFo(Fan-out)、3DSIP三大封装技术构成。TSV技术,主要应用于影像传感器的封装,主要结构就是MVP、MVPPlus和直孔的工艺,目前主要推的就是直孔的工艺;eSiFo或Fan-out是华天独有的硅基扇封装,有多芯片封装、超大尺寸的eSiFO,还有超薄的eSiFO,还有高密度Fan-out;3DSiP,基于eSiFO结合TSV技术,开发了eSinC技术,基于eSinC有不同的实现SiP的结构,或者是POP的形式实现SiP。

3DMatrix平台图源:华天科技

CoWoSCoWoS(ChipOnWaferOnSubstrat,晶圆基底封装)是一种2.5D整合生成的晶圆级封装技术,即直接在硅晶圆上完成封装。先将芯片通过ChiponWafer(CoW)的封装制程连接至硅晶圆,再把CoW芯片与基板(Substrate)连接,整合成CoWoS。主要用在人工智能、网络和高性能计算。

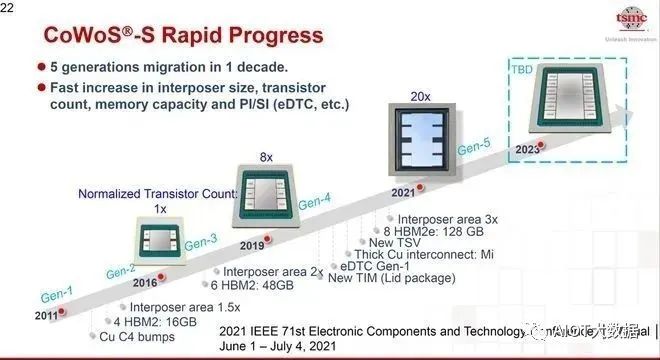

强化版CoWoS图源:台积电/博通2012年,台积电开始量产CoWoS,可以把多颗芯片封装到一起,平面上的裸芯片通过一种SiliconInterposer互联,达到了封装体积小,功耗低,引脚少的效果,并被英伟达GP100、谷歌AlphaGo和日本“富岳”超算等采用,进而拉掀起世界人工智能热潮。2021年,台积电量产第五代CoWoS。第五代CoWoS先进封装技术晶体管数量是第三代20倍,同时增加3倍中介层面积,而且使用全新TSV解决方案以及更厚的铜连接线。而第6代CoWoS封装工艺,或将集成更多的小芯片和DRAM内存,预计可以在同一封装内容纳两个计算芯片和八个或以上的HBM3DRAM芯片,可能会在2023年推出。

CoWoS封装技术路线图图源:台积电CoWoS可以分为CoWoS-S、CoWoS-R和CoWoS-L三种。台积电称,CoWoS-S可以为高性能计算应用提供最佳的性能和最高的晶体管密度;CoWoS-R则更强调小芯片间的互连,利用RDL(重新布线层)实现最小4μm的布线;CoWoS-L则是最新的CoWoS技术,结合了CoWoS-S和InFO两种技术的优点,使用RDL与LSI(本地硅互连)进行互连,具有最灵活的集成性。CoWoS制程研发到量产已有将近10年时间,已是最广泛的2.5D封装技术,具有非常高的产量。已经获得NVIDIA、AMD、Google、XilinX、NEC、Habana、华为海思等高端芯片厂商的支持。包括大部分创企的AI训练芯片都是应用了CoWoS技术。预计未来,AI处理器、机器学习处理器、高性能计算机或都有CoWoS的阴影。

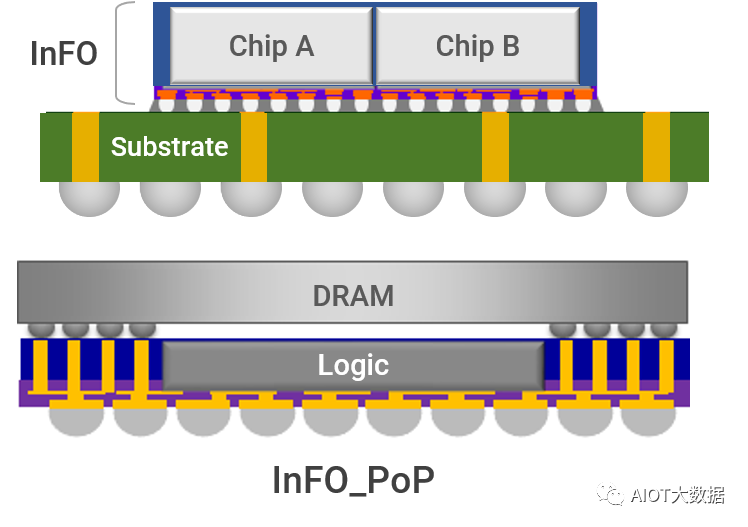

InFO

InFO(InteratedFan-out),集成扇出型封装,台积电于2017年开发出来的FOWLP先进封装技术,是将CoWos结构尽量简化,最后出来一个无须硅中介层的精简设计,可以直接连接芯片与芯片,减少厚度,降低成本,高性价比,可应用于射频和无线芯片的封装,处理器和基带芯片封装,图形处理器和网络芯片的封装。在晶圆代工大厂中,仅台积电拥有集成扇出型封装(InFO)。

InFO_PoP和InFO_oS封装技术示意图图源:台积电

台积电对CoWoS技术做了简化,降低了成本,设计出了InFo封装技术,满足了移动通讯市场高性价比的需求。InFO分为InFO_PoP和InFO_oS,前者是行业中首款3D晶圆级扇出封装,可应用在移动手机的AP和DRAM上;后者具有更高密度的RDL,可集成多个用于5G网络的逻辑芯片。

苹果处理器早年一直是三星来生产,但台积电拿下iPhone7订单开始,一直通吃到现在各iPhone,就在于全新封装技术InFO,能够使芯片与芯片之间直接互连,减少厚度,腾出宝贵的空间给电池或其他零件使用。以后其他品牌的手机也会开始普遍使用这个技术,改变了晶圆级封装的市场格局。

SoIC

SoIC(System-on-Integrated-Chips),也称TSMC-SoIC,是台积电于2019年推出了集成芯片系统(SoIC)技术。是业界第一个高密度3D小芯片(chiplet)堆栈技术,可将不同尺寸、功能、节点的晶粒进行异质整合。

SoIC技术最鲜明的特点是没有凸点(no-Bump)的键合结构,因此具有更高的bump密度和速度和更佳的运行性能,同时消耗更少的电能。将多个dice直接堆叠到一起。因此SoIC复杂度,远超以往的硅中介层或芯片堆叠工艺。可以直接透过极微小的孔隙来沟通多层的芯片。它比同等的DIP封装减少约30-50%的空间,厚度方面减少约70%。这意味着在10纳米以下的制程,芯片能在接近相同的体积里,增加双倍以上的性能。

SoIC封装来源:台积电

作为一种颠覆式创新的多芯片堆叠技适应了5G、人工智能、高效能运算(HPC)等新应用。英伟达正加紧与台积电在高端芯片上的合作。正考虑HPC芯片采用台积电的SoIC技术。

台积电2022年开始SoIC晶片堆叠制造,并计划在2026年将产能扩大到20倍以上。目前,台积电正扩大在竹南的bumping制程、测试和后端3D先进封装服务产能。

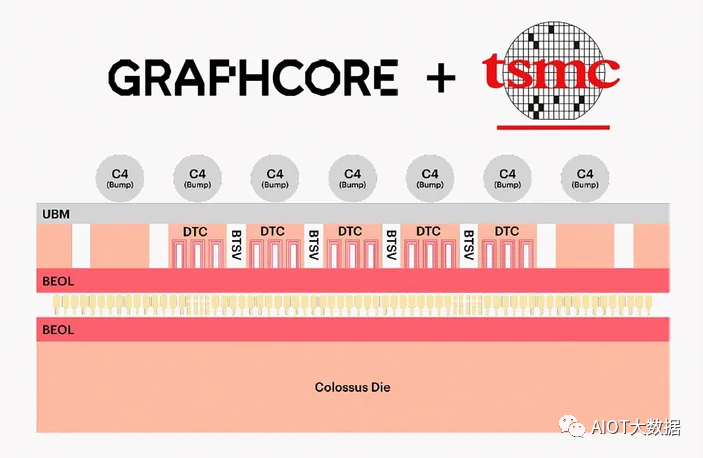

GraphcoreIPU芯片中的封装示意图图源:IEEE

SoIC-WoW是基于SoIC升级的封装技术,就是SoIC-WoW(waferonwafer)类似于3DNAND闪存多层堆叠那样,将两层裸片以镜像方式垂直堆叠起来,以更先进的封装技术提升芯片性能。

2022年3月,英国AI公司Graphcore的推出全球第一款3D封装的处理器BowIPU,采用了台积电SoIC-WoW技术,需要指出的是,这是一种用于硅晶圆的3D堆叠形式,使得单个封装芯片中的晶体管数突破了600亿个大关。

3DFabric

而为了满足当前系统效能、缩小面积以及整合不同功能的需求,台积电将SoIC(系统整合芯片)、InFO(整合型扇出封装技术)、CoWoS(基板上晶圆上芯片封装)等先进封装与芯片堆栈技术,整合为3DIC技术平台——3DFabric,可让客户自由选配。

3DFabric技术平台图源:台积电

组装测试相关技术包含整合型扇出InFO及CoWoS系列产品。CoWoS针对高端市场,连线数量和封装尺寸都比较大。InFO针对性价比市场,封装尺寸较小,连线数量也比较少。SOIC主要应用在HPC,因为它非常适合HPC的高速和节能,但对于移动应用,SOIC依赖于廉价的架构,互连密度要求和一些其他要求,台积电将有其他解决方案来解决这部分需求。更重要的是,SoIC和CoWoS/InFO可以共用,基于SoIC的CoWoS或InFO封装将会带来更小的芯片尺寸,实现多个小芯片集成。

目前在竹南已拥有首座3DFabric的全自动化工厂,将先进测试、SoIC和InFO/CoWoS运作整合在一起,并在2023年开始3DFabric的全面运作。

作为晶圆制造龙头,台积电也是最早开始布局先进封装的上游厂商之一。如今持续引领代工厂的先进封装。

I-Cube2018年,三星发布了I-Cube2,(InterposerCub2)可以集成一个逻辑裸片和两个HBM裸片的技术。2020年,三星推出新一代2.5D封装技术是I-Cube4。它是使用硅中介层的方法,将多个芯片排列封装在一个芯片上的新一代封装技术。I-Cube4包含四个HBM和一个逻辑芯片,是I-Cube2的进一步升级。

I-Cube4封装构成图源:三星

硅中介层(Interposer)指的是在飞速运行的高性能芯片和低速运行的PCB板之间,插入的微电路板。硅中介层和放在它上面的逻辑芯片、HBM通过硅通孔(TSV,ThroughSiliconVia)微电极连接,可大幅提高芯片的性能,还能减小实装面积。三星指出,随着高性能应用的爆炸式增长,必须提供具有异构集成技术的整体代工解决方案,以提高芯片的整体性能和电源效率。凭借I-Cube2的生产经验以及I-Cube4的商业竞争力,三星还将开发配置了6个和8个HBM芯片的新技术。重点部署在高性能计算领域。

X-Cube

X-Cube,eXtended-Cube,意为拓展的立方体。2020年,三星基于硅直通(TSV)技术开发,可以将包括SRAM在内的不同芯片垂直堆叠,从而释放空间堆叠更多内存芯片。X-Cube技术最早用于自家的7nm及5nm工艺,可以将SRAM与逻辑部分分离,更易于扩展SRAM的容量。另外,3D封装缩短了裸片之间的信号距离,能够提升数据传输速度并提高能效。有助于满足最前沿的5G、AI、AR、HPC、移动芯片以及VR等领域的严格性能要求。

X-Cube测试芯片封装与架构图源:三星

R-Cube

R-Cube是三星的低成本2.5D封装方案,采用高密度的RDL技术,较I-Cube具有更快的周转时间和更好的信号/电源完整性,设计灵活性较好。

H-Cube

H-Cube(HybridSubstrateCube,混合基板封装),2021年,由三星电机与Amkor共同开发的全新2.5D封装解决方案,适用于需要集成大量硅片的高性能芯片。

H-Cube通过整合两种具有不同特点的基板:精细化的ABF(AjinomotoBuild-upFilm,味之素堆积膜)基板,以及HDI(HighDensityInterconnection,高密度互连)基板,可以进一步实现更大的2.5D封装。H-Cube专用于需要高性能和大面积封装技术的高性能计算(HPC)、人工智能(AI)、数据中心和网络产品等领域。

H-Cube封装解决方案图源:三星

三星凭借I-Cube、X-Cube、R-Cube和H-Cube四套封装方案方案,通过扩大和丰富代工生态系统,为突破客户挑战提供丰富的封装解决方案。三星客户既可以选择三星电子晶圆代工部门的封装产品或安靠等封测合作伙伴产品;也可以移交COT(客户拥有的工具)、COPD(客户拥有的物理设计)模型获得。

2022年3月,三星电子在DS(半导体事业暨装置解决方案)事业部内新设立了测试与封装(TP)中心,意图与台积电在先进封装领域进行竞争。6月中旬,三星电子成立半导体封装业务特别小组,7月份又爆出这一特别小组,成员来自设备解决方案部门的多个领域,包括封测业务方面的工程师、半导体研发中心的研发人员、存储和晶圆代工业务领域的高管,三星这一特别小组,有望推出先进的封装解决方案,加强与客户的合作。

已率先量产3nm制程工艺,计划在未来5年向半导体、生物制药等领域投资超过3600亿美元的三星电子,正在大力发展半导体封装业务,以帮助公司在半导体测试和封装领域日益激烈的竞争获胜。

3DV-Cache3

2021年6月,芯片巨头AMD发布了发布3DChiplet先进封装技术——3DV-Cache。该产品使用台积电的3DFabric先进封装技术,相较于2D芯片堆叠技术,3DV-Cache技术可将芯片内互连密度提升超过200倍。3DV-Cache使用了一种新颖的混合键合技术,融合了额外的64MB7nmSRAM缓存垂直堆叠在Ryzen计算小芯片的顶部,使每个Ryzen芯片的L3缓存数量增加三倍。

图源:AMD

3DFabric是面向服务器和台式机应用的创新3D堆叠技术,使处理器实现了15%的性能提升,而先前每一代半导体工艺节点的提升对于芯片性能的提升也在15%左右。2022年,AMD宣布全面推出世界首款采用3D芯片堆叠的数据中心CPU,即采用AMD3DV-Cache技术。

AMD的3DV-Cache标志着该公司首次涉足3D封装,将继续引领先进封装技术发展。

EMIB

EMIB,EmbeddedMulti-DieInterconnectBridge,即嵌入式多芯片互连桥接,该封装技术是由英特尔2018年开发的,EMIB是独立显卡和高宽度内存之间的智慧信息桥,将这些组件紧密联合在一个封装中,也就是可以促进多个裸片封装之间的高速通信。提供每平方毫米达到500个I/O的密度,成本更低,实现包括CPU、图形卡、内存、IO及其它多个芯片间的通信。

EMIB封装图源:英特尔

英特尔EMIB技术是在2.5D封装领域的布局,因为三星和台积电先进封装的地位与日俱增。类比台积电Info封装,在功能以及设计诉求上大同小异。将不同工艺、不同架构的芯片封装在一起,灵活搭配降低成本,让那些无需顶级工艺的产品依然采用最高性价比的方案。

在EMIB正式披露后不久,FPGA龙头Altera推出了行业中第一款异构系统级封装芯片,这颗芯片利用英特尔的EMIB技术,实现了DRAM与FPGA的互连问题,初步向外界展示了英特尔先进封装的性能。

自2017年至今,英特尔的EMIB产品一直在出货且不断迭代。已经公开的EMIB已经大量生产,比如说KabyLake以及Stratix10FPGA都是基于该封装技术的产品。

Foveros

Foveros被称作3DFacetoFaceChipStackforheterogeneousintegration,三维面对面异构集成芯片堆叠技术,是英特尔2018年12月推出的全新3D封装技术。

Foveros最显著的特点是多IP组合灵活(异构),并且占用面积小、功耗低,特别是结合上英特尔10nm制程,摩尔定律从晶体管密度(2D)到空间布局(3D)两个维度得到延续。不同于以往单纯连接逻辑芯片、存储芯片,Foveros创新性地把不同逻辑芯片堆叠、连接在了一起,可以“混搭”不同工艺、架构、用途的技术IP模块、各种内存和I/O单元,其中I/O、SRAM缓存、传输总线整合在基础晶圆中,高性能逻辑单元则堆叠在顶部。

Foveros封装图源:英特尔

EMIB与Foveros的区别在于前者是2D封装技术,而后者则是3D堆叠封装技术,与2D的EMIB封装方式相比,Foveros更适用于小尺寸产品或对内存带宽要求更高的产品。虽说Foveros是更为先进的3D封装技术,但它与EMIB之间并非取代关系,英特尔在后续的制造中会将二者结合起来使用。

Co-EMIB

Co-EMIB技术:利用高密度的互连技术,将EMIB(嵌入式多芯片互连桥接)2D封装和Foveros3D封装技术结合在一起,

Co-EMIB技术是英特尔2019年7月推出的,实际上EMIB和Foveros两项技术的创新组合,基于高密度的互连技术,可以将多个3DFoveros芯片通过EMIB互连在一起,制造更大规模的芯片,最终实现高带宽、低功耗,以及相当有竞争力的I/O密度,也能实现不同芯片、模块更灵活的组合,基本达到SoC的性能,为芯片封装带来绝佳的灵活性。

图源:英特尔

ODI

ODI,全称为Omni-DirectionalInterconnect,全向互连为封装中小芯片之间的通信提供了更大的灵活性。顶层芯片可以和其他小芯片水平通信,类似于EMIB。它还可以与下方基底芯片中的硅通孔(tsv)垂直通信,类似于Foveros。并且ODI利用大的垂直通孔来允许功率从封装衬底直接传输到顶部管芯。大过孔比传统tsv大得多,具有更低的电阻,提供更强大的功率传输,同时通过堆叠实现更高的带宽和更低的延迟。同时,这种方法减少了基础芯片中所需的TSV数量,为有源晶体管释放了更多的面积,并优化了芯片尺寸。

全方位互连技术ODI图源:英特尔

MDIO

MDIO全称为Multi-DieIO,也就是多裸片输入输出,简单地说,MDIO是一种性能更好的芯片到芯片之间的接口(引脚)技术。相对于之前英特尔所使用的AIB(高级接口总线)技术,MDIO能够在更小的连接面积内实现更高的数据带宽。这样,即便是使用ODI技术中更细的针脚也能够满足芯片之间数据带宽的需求

MDIO封装产品在2020年推出,相比基于第一代AIB技术的新品,带宽、密度、电压、能效各方面指标都有了极大的提升,其中针脚可达5.4Gbps。台积电也曾宣布类似的封装技术LIPNCON。

HybridBonding

2020,Intel又宣布了全新的HybridBonding(混合键合、混合结合)技术,可取代当今大多数封装技术中使用的"热压结合"(thermocompressionbonding)。

图源:英特尔

HybridBonding可以把凸点间距降到10微米以下,带来更高的互连密度、带宽和更低的功率。这些封装技术还可以相互叠加,叠加后能够带来更大的扩展性和灵活性。

在先进封装领域,英特尔依旧是全球技术创新的领导者,创造性地推出了EMIB、Foveros、Co-EMIB、ODI等先进封装互联技术,继续驱动着技术不断向前!

SWIFT2016年,安靠推出新硅片集成扇出技术SWIFT,并与2017年量产。凭借其精细的光刻技术和薄膜电介质,SWIFT弥合了硅通孔(TSV)和传统晶圆级扇出(WLFO)封装之间的差距。与基于层压板的基板技术相比,SWIFT在外形尺寸、信号完整性、功率分配和热性能方面都有显著改进。适用于高性能CPU/GPU,FPGA,MobileAP以及MobileBB等。3DSWIFT的独特特性要部分归功于与此项创新晶圆级封装技术相关的小间距功能。它使应用积极主动的设计规则成为现实,有别于传统的WLFO和基于层压板的封装,且能够被用于建立先进的3D结构,以应对新兴移动和网络应用中日益高涨的IC集成需求。

HDFO封装互连芯片图源:安靠

基于Amkor的硅晶圆集成扇出式技术SWIFT,安靠又开发出HDFO高密度扇出封装,类似CoW,但采用的是没有TSV结构的晶圆级封装,是下一代的异构芯片封装的发展方向。

SLIM/SWIFT解决方案图源:Amkor与SWIFT方案相辅相成的还有,具备2.5D封装能力的SLIM,采用TSV-less工艺,简化了2.5DTSV硅中介层运用时PECVD及CMP工序。还与三星电机和安靠合作开发了2.5D封装解决方案“H-Cube”,在缩小半导体尺寸的同时,将多个新一代存储芯片(HBMs)整合在一起,实现了效率最大化。

CSP

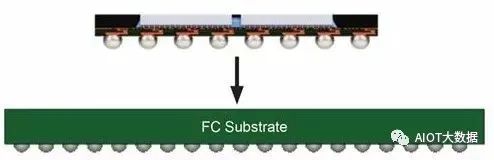

Amkor的倒装芯片CSP(fcCSP)封装是采用CSP封装格式的倒装芯片解决方案。此封装结构搭配安靠的各种可用的铜柱、无铅焊料、共晶,在面阵中实现倒装芯片互连技术,同时取代外围凸块布局中的标准焊线互连。

对于性能和外观规格都至关重要的应用来说,fcCSP封装是非常具有吸引力的选项。例如,高性能移动设备(包括5G)、适用于汽车的信息娱乐和ADAS,以及人工智能等。除此以外,低电感和布线密度的增加实现了高频信号电气通路的优化,使fcCSP适用于基带、RF和基板内天线应用。

但是FCCSP封装技术并非安靠一家独有,日月光、通富微电、长电科技等顶级OSAT以及三星、SK海力士、美光等内存供应商都是这技术领域的有利竞争者。因为它们提供像WLCSP一样的低成本和可靠的解决方案,而不会产生更高的扇出型封装成本。

不同类型的fcCSP图源:长电

全球最大封测厂日月光的六大封测技术。

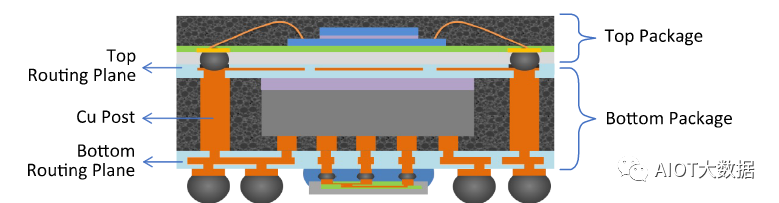

FOPoP

FOPoP封装技术基于RDL,它将扇出底部封装与安装在顶部的标准封装相结合,并利用小间距电镀铜柱进行贯穿模制的垂直互连。底部封装有两个RDL(顶部和底部布线层),由铜柱连接,铜柱由晶圆级扇出技术形成,可实现更薄、更精细的电气走线。

堆叠扇出封装(FOPoP)图源:ASE

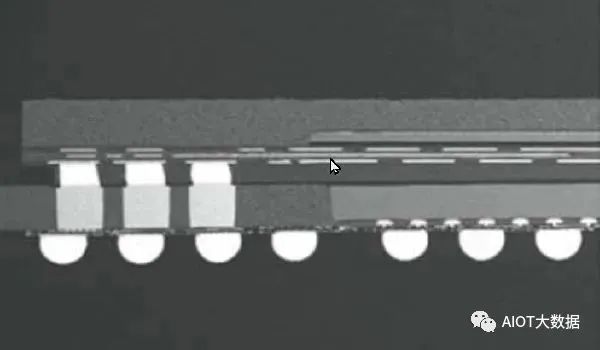

FOPoP的部分截面图图源:ASE

与传统的基于插入物的PoP相比,FOPOP具有更薄的外形和更好的电气和热性能,因为底部封装消除了对插入物的需要。便于存储器件和逻辑器件的3D集成;减小系统尺寸,节省电路板空间;提升存储器架构灵活性;缩短信号路径;且与当前的组装技术兼容;开发周期时间和成本也可以减少,因为顶部和底部封装可以从资格、产量、来源、采购时间和物流处理的角度相互分离。

FOPOP已经成为物联网(IoT)、移动电话、可穿戴电子应用中逻辑器件(例如基带和具有高性能存储器(例如高带宽存储器(HBM))的应用处理器)的有前途的3D集成解决方案。

FOCosFOCoS是一个扇出封装倒装芯片安装在高引脚数球栅阵列(BGA)基板上。扇出封装具有再分布层(RDL),允许在多个芯片之间构建更短的管芯到管芯(D2D)互连。扇出封装被视为单个管芯,然后被倒装到BGA基板上。

图源:ASE

FOCos-B日月光基于FOCoS提供了一种用于实现小芯片集成的硅桥技术,称为FOCoS-B(桥),它利用带有路由层的微小硅片作为小芯片之间的封装内互连,例如图形计算芯片(GPU)和高带宽内存(HBM)。硅桥嵌入在扇出RDL层中。FOCoS的硅桥在封装中提供超细间距互连,可以解决系统中的内存带宽瓶颈挑战。与使用硅中介层的2.5D封装相比,FOCoS-B的优势在于只需要将两个小芯片连接在一起的区域使用硅片,可大幅降低成本。

图源:ASE

以上ASEFOCoS套装产品为高性能计算(HPC)和人工智能(AI)/机器学习(ML)应用中的小芯片集成提供了广泛的选择。FOCoS非常适合为网络和服务器应用设计的大封装尺寸和高I/O密度(>1000I/O)封装。FOCoS的芯片最新版本可用于封装专用集成电路(ASICs)和高带宽存储器(HBM)。

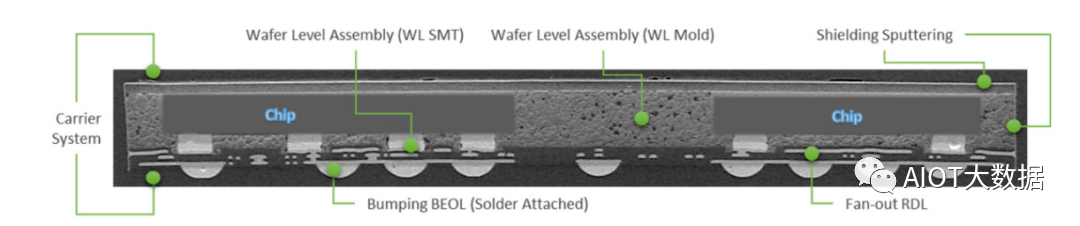

FOSiP

FOSiP是扇出SiP,基于几个核心技术构建模块,包括芯片最后RDL制造、载体系统、晶圆级组装和屏蔽溅射在内的,如下图所示:

扇出SiP和技术构建模块的横截面图源:ASE

首先,扇出RDL提供了比主流基板更好的精细线路设计能力,以增强SiP中的功能匹配。第二,载体系统使薄晶片处理成为可能。此外,晶圆级组装提供高速(>60k单位/小时)SMT服务和用于高级封装的模制底部填充(MUF)技术。最后,屏蔽溅射提供了应用于特定RF应用的选择。简而言之,日月光为客户提供了一个完整的工具箱来服务扇出SiP封装。

灵活的RDL设计来调整系统性能(与引线键合相比);用于更高性能控制的更精细的RDL线宽和间距(实现大约5X增强);基板层减少(大约减少3层);外形尺寸缩小(与典型的基于基板的SiP相比,接近24%);通过晶圆级平台和高速SMT能力(与凸块工艺兼容)实现经济高效的工艺;基于可选屏蔽技术(五面溅射)的更广泛射频(RF)应用。

扇出SiP可用市场方法范围可分为:智能手机、平板电脑、射频基础设施、边缘计算和物联网(IOT)。更高频率的应用、更好的性能和成本效益正在推动封装的创新和集成。扇出SiP提供了一个新的平台来满足这些市场的需求,使下一代产品成为可能。

2.5D/3D

2.5D/3D是用于在同一封装内包括多个IC的封装方法。在2.5D结构中,两个或多个有源半导体芯片并排放置在硅内插器上,以实现极高的管芯到管芯互连密度。在3D结构中,通过管芯堆叠来集成有源芯片,以实现最短的互连和最小的封装尺寸。

日月光2.5D/3DIC封装解决方案提供了集成GPU、CPU和存储器以及去耦电容的优势。具有TSV(硅通孔)的Si内插器可以用作桥接组件基板和集成电路板之间的精细间距能力差距的平台。它还有助于保持焊盘间距缩放路径,而不受组装基板技术的限制。

2.5D图源:ASE

日月光通过创新在行业内变得越来越重要的2.5D和3D技术不断拓展新领域:高端GPU、高端FPGA、面向数据中心和5G基础设施的网络交换机/路由器、用于人工智能培训的人工智能加速器。在小芯片时代,2.5D和3DIC封装将在CPU、移动AP、Si光子学、显示驱动IC等应用中发挥越来越重要的作用。

日月光已经确立了其在2.5D技术领域的领导者地位,成功交付了开创性的2.5D解决方案,帮助将先进的ASIC和HBM产品推向市场。为了延续这一技术创新势头,日月光正在推出用于芯片堆叠和多芯片解决方案的高密度扇出技术,以实现整个市场的高带宽和高性能,满足从高密度数据中心到消费者和移动空间的需求。

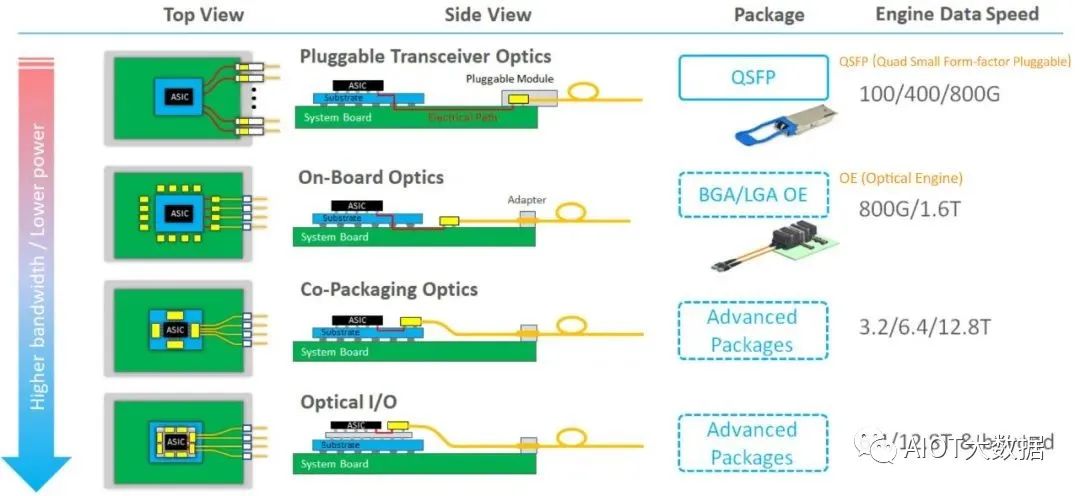

Co-PackagedOptics

数据传输在高性能计算应用中变得越来越重要,而传统的铜线受到带宽、距离和功率要求的限制。硅光子学是一种很有希望取代铜线的技术,它提供更大的带宽、更长的传输距离和更好的能效。因此,在未来的超大规模数据中心,硅光子技术将被广泛用于光收发器或板载/共封装光学器件。

用光路代替电路的数据传输的演变图源:ASE

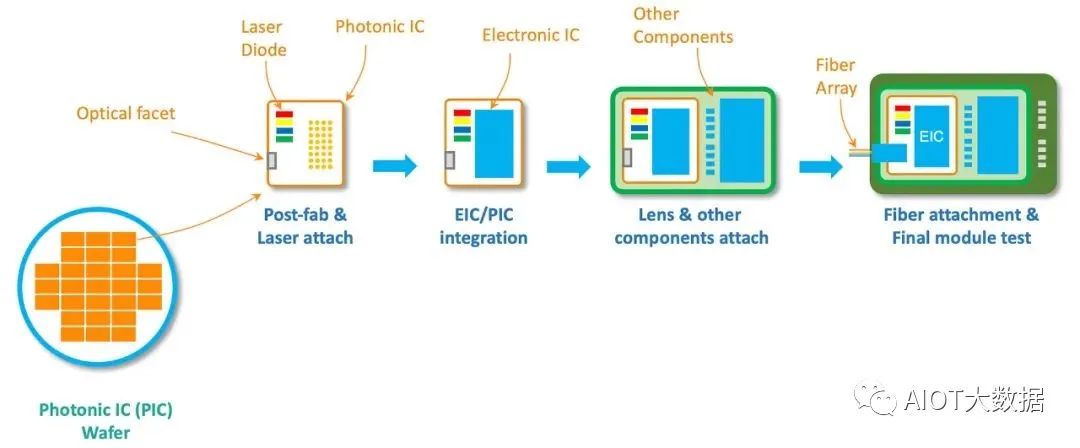

Co-PackagedOptics是与矽光子晶片共同封装的技术。硅光子学(SiPh)作为一种介质,允许光在其中传播。得益于现代半导体技术,硅光子学能够利用现有的互补金属氧化物半导体(CMOS)生态系统,包括前端和后端工艺来实现高密度光子集成电路(PIC),并以低成本在紧凑的芯片上实现复杂的光学功能(例如:滤波或调制)。与传统的电子集成电路相比,硅光子技术具有更高的带宽和更好的能量效率来传输数据,传统的电子集成电路在高速传输数据时可能会遭受严重的信号完整性失真。

基于SiPh的可插拔模块制造流程图源:ASE

硅光子学使异质板载光学器件、共同封装光学器件和光学I/O封装成为可能,在超大规模数据中心、高性能计算(HPC)、人工智能和机器学习(AI&ML)有望实现应用。

VIPack

2022年6月,日月光宣布推出VIPack先进封装平台,提供垂直互连整合封装解决方案。VIPack是日月光扩展设计规则并实现超高密度和性能设计的下一代3D异质整合架构。此平台利用先进的重布线层(RDL)制程、嵌入式整合以及2.5D/3D封装技术,协助客户在单个封装中集成多个芯片来实现创新未来应用。

图源:ASE

VIPack由以上六大核心封装技术组成,通过全面性整合的生态系统协同合作,包括基于高密度RDL的FanOutPackage-on-Package(FOPoP)、FanOutChip-on-Substrate(FOCoS)、FanOutChip-on-Substrate-Bridge(FOCoS-Bridge)和FanOutSystem-in-Package(FOSiP),以及基于硅通孔(TSV)的2.5D/3DIC和Co-PackagedOptics。除了提供开拓性高度整合硅封装解决方案可优化时脉速度、频宽和电力传输的制程能力,VIPack平台更可缩短共同设计时间、产品开发和上市时程。

VIPack平台提供应用于先进的高效能运算(HPC)、人工智能(AI)、机器学习(ML)和网络等应用的整合分散式SoC(系统单晶片)和HBM(高带宽记忆体)互连所需的高密度水平和垂直互连解决方案。

HBM

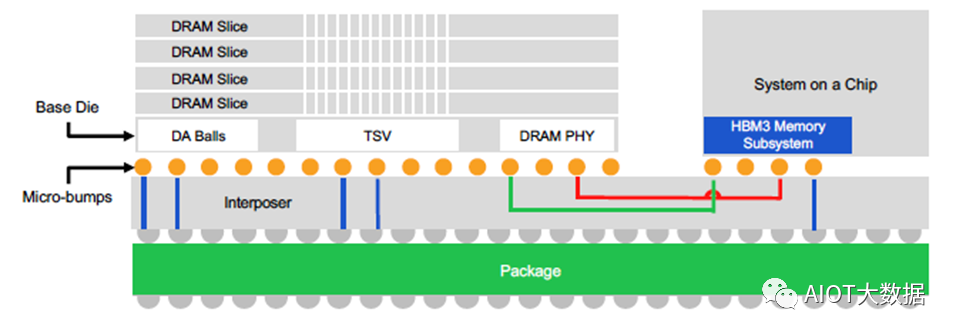

HBM(High-BandwidthMemory)高带宽内存,主要针对高端显卡市场,是AMD、NVIDIA和海力士主推的HBM标准,HBM技术与其他技术最大的不同,就是采用了3D堆叠技术。HBM用3DTSV和2.5DTSV技术,通过3DTSV把多块内存芯片堆叠在一起,并使用2.5DTSV技术把堆叠内存芯片和GPU在载板上实现互连。

对比HBM2E/HBM3、DDR、GDDR就会发现,它们的基本单元都是基于DRAM,但不同之处在于其他产品采用了平铺的做法,而HBM选择了3D堆叠,其直接结果就是接口变得更宽。比如DDR的接口位宽只有64位,而HBM2E通过DRAM堆叠的方式就将位宽提升到了1024位,这就是HBM与其他竞争技术相比最大的差异。

美光用于HBM2E的垂直堆叠DRAM,并通过TSV通道连接各层图源:美光

RambusHBM3-Ready内存子系统产品主要架构图源:Rambus

HMC

HMC是由HMCC(混合存储立方体联盟)制定的一种基于TSV技术3D堆叠内存标准,它是把一层层DRAM晶圆叠在一起,就像盖楼一样,这样就可以组成一个大容量的“内存”芯片,芯片之间通过TSV(硅通孔)进行垂直相连。

HMC由美光主推,目标市场是高端服务器市场,尤其是针对多处理器架构。HMC使用堆叠的DRAM芯片实现更大的内存带宽。另外HMC通过3DTSV集成技术把内存控制器(MemoryController)集成到DRAM堆叠封装里。

图源:美光

当然,除了以上晶圆制造与封装大厂拥有独立命名和通用技术外,紧随其后的力成(PTI)、智路封测(WiseRoad)、京元电子(KYEC)、南茂(ChipMOS)也正在先进封装技术上发力追赶。

UCle

2022年3月初,英特尔、台积电、三星和日月光等十大巨头宣布成立通用芯片互连标准——UCIe,将Chiplet(芯粒、小芯片)技术标准化,旨在标准化小芯片的构建和相互通信方式。这一标准同样提供了“先进封装”级的规范,涵盖了EMIB和InFO等所有基于高密度硅桥的技术。而且UCIe支持2D、2.5D和桥接封装,预计未来还会支持3D封装。

UCIe联盟所推荐的4种Chiplet封装方式

而在此之前,众多的芯片厂商都在主张自己的互联标准,比如Marvellandou总线接口;NVIDIA高速互联NVLink方案;英特尔EMI接口;台积电和Arm合作的LIPINCON协议;AMD也有InfinityFabrie总线互联技术等等。国内芯动还自主研发的InnolinkChiplet标准。但这些早期的Chiplet发展协议混乱,各公司制定标准也不过为各自的利益而战。

在产业链内,Chiplet所依靠的先进封装技术仍然未实现统一,全球顶级的晶圆厂努力以硅片加工实现互联为主,可提供更高速的连接和更好的延展性;中国大陆、台湾的封装厂却在努力减少硅片加工需求,输出性价比更优于头部晶圆大厂的廉价方案。

只有当标准得到普遍采用时,才能最大程度体现其价值。UCIe拥有英特尔、日月光(ASE)、AMD、Arm、谷歌云、Meta、微软、高通、三星、台积电10个初始成员,虽然是Fabless、Foundry,OSAT和IP的“代表”,却维护了头部企业的价值链。

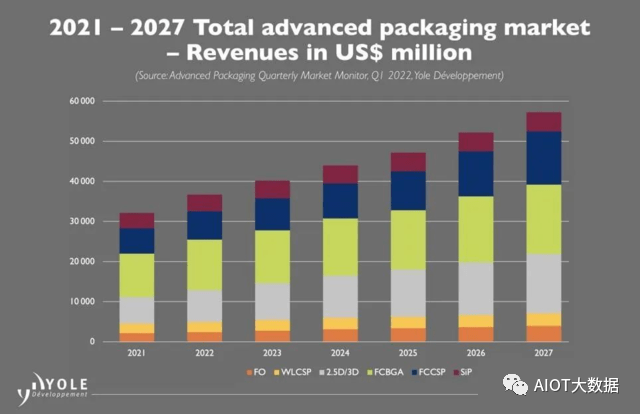

根据Yole数据,2021年全球封装市场规模约达777亿美元。其中,先进封装全球市场规模约350亿美元。5G、ADAS、人工智能、数据中心及可穿戴电子等应用市场的蓬勃发展,推动先进封装市场的业绩持续上扬。

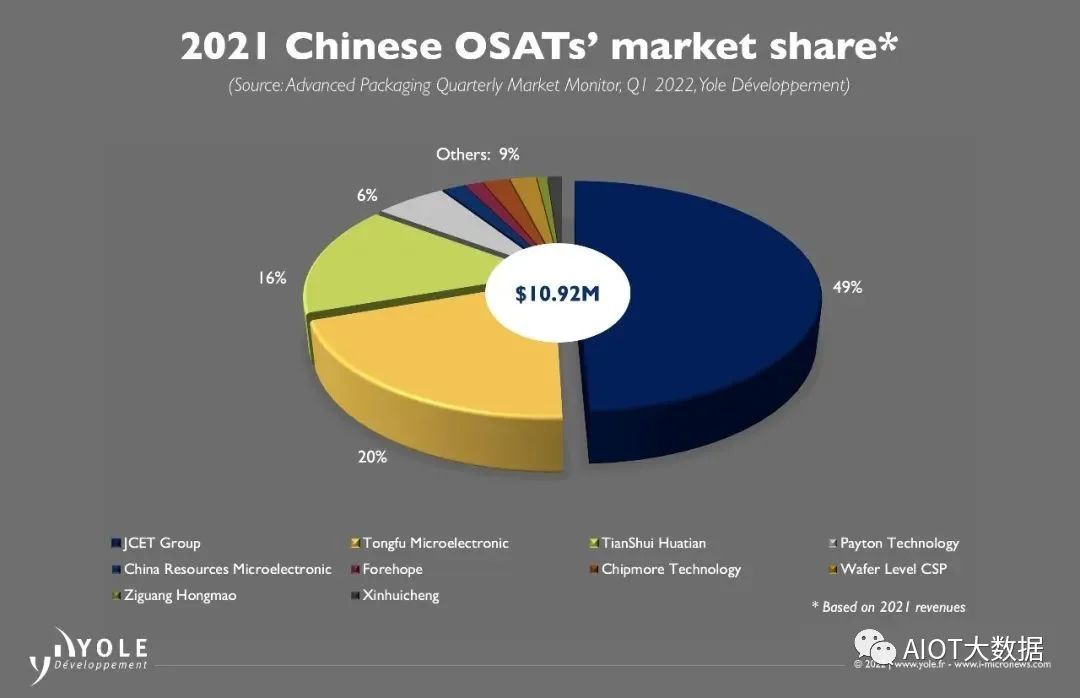

根据2021年营收情况,长电科技、通富微电和天水华天占据了中国前十OSAT营收的85%,并跻身全球前十之列。此外,沛顿科技、晶方半导体、颀中科技、华润微电子和甬矽电子等公司2021年营收增长处于领先地位。

2021年中国OSAT市场图源:Yole

在先进封装市场持续扩张的情况下,无论是晶圆代工厂还是封测厂,都提前布局先进封装。于是乎,先进封装的赛道挤满了各大玩家,2022年,英特尔、台积电和三星等芯片制造巨头将进一步加大先进封装领域的布局力度。日月光、安靠、长电科技、通富微电的资本支出有增无减。

封装技术发展方向图源:美国应用材料

编辑:黄飞

-

无线串口延伸器2014-12-11 2380

-

国产CAD软件中裁剪延伸功能如何使用?2020-11-11 1439

-

车箱灯延伸器电路图2009-03-24 719

-

遥控延伸器2009-10-06 515

-

图尔克RFID系统应用延伸2009-11-17 1078

-

MATLAB入门教程之基本xy平面绘图命令2011-02-18 7132

-

CAD制图中修剪与延伸的使用技巧2012-10-19 14879

-

基于CANopen协议的延伸报警器研制2016-01-04 1508

-

ChatGPT,人类认知力延伸的竞赛2023-03-06 1556

-

「观点」外骨骼是人类肢体的延伸2023-09-20 1969

-

先进封装,在此一举2023-10-10 2430

-

先进封装的核心概念、技术和发展趋势2024-12-18 3023

-

自动化新宠来袭——XY双轴直线模组大揭秘2025-07-01 1839

-

2D、2.5D与3D封装技术的区别与应用解析2026-01-15 1122

-

矢量网络分析仪的去嵌入与端口延伸技术解析2026-03-03 1745

全部0条评论

快来发表一下你的评论吧 !