集成电路测试定义

描述

集成电路进人后摩尔时代以来,安全、可靠的软硬件协同设计、冗余定制、容错体系结构和协议、光机电一体化等新的设计趋势促使片内测试 (On-ChipTest)/片外测试(OIf-Chip Test) 整体测试解决方案趋于复杂化:先进工艺路线的发展,促使集成电路失效故障测试模型不断演化:芯片尺寸封装 ( ChipScale Package, CSP)、圆片级封装( Wafer Level Package, WLP)、硅通孔(Through Silicon Via, TSV)、三维集成等先进封装工艺,带来了新的测试工序和复杂光机电集成失效特性:这些技术的演进也导致集成电路测试变得日益复杂。互联网、物联网、云计算、大数据等新应用、新业态的出现,不断推动集成电路测试技术的发展和信息化进程。

集成电路测试既是集成电路设计的组成部分,也是芯片制造的一个环节,集成电路测试的主要作用是检测电路存在的问题、问题出现的位置和修正问题的方法。如果一个电路未能通过测试。可能的原因包括测试本身、产品设计,制造过程等方面。测试技术研究就是在兼顾品质和经济性的条件下制定合适的测试方案,即用最低的成本检出最多的故障。

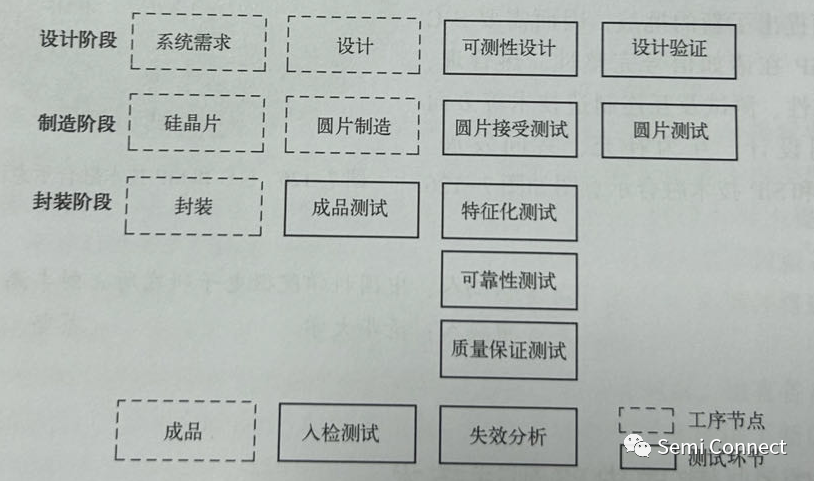

测试贯穿于集成电路生产过程,分为设计验证、检测筛选、质量控制等。下图所示的是集成电路产业链中主要的测试环节。由图可以看出,设计阶段的可测性设计和设计验证,制造阶段的圆片接受测试和圆片测试 ( Circuit Probe),以及封装阶段的成品测试、失效分析等,都属于测试技术领域。

特征化测试是对功能、直流特性、交流特性进行全面的功能/性能检测,用以表征集成电路各项极限参数,验证设计的正确性。

圆片级测试是在集成电路制造后进行的园片状态下的测试,用于最初阶段的合格电路的筛选。随着圆片级封装、三维异质集成、测试模式演变、电路修调定制等需求的发展,圆片级测试变得更具挑战性。

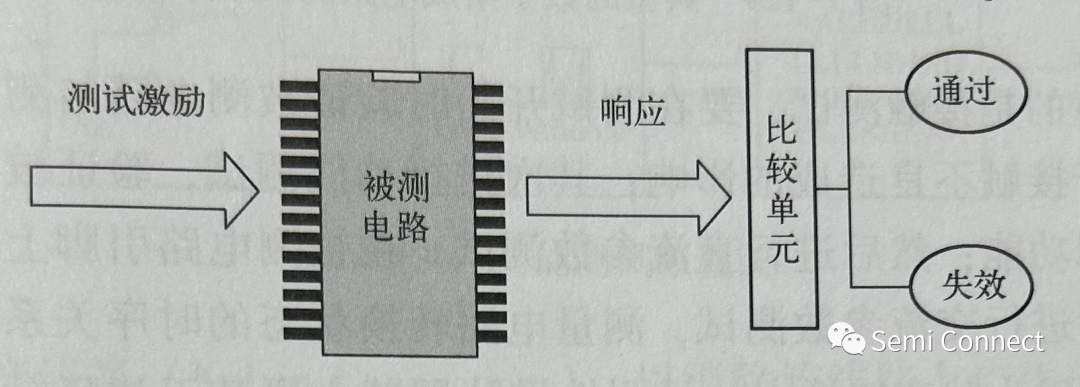

成品测试是封装后的测试环节,用以检测集成电路在此阶段是否符合规格要求。有时也会加人系统应用级测试,通常会将前面环节中实施成本较高的测试项目放在该测试环节,以避免不合格产品进人最终应用环节下图所示的是基本的测试原理框图。由图可知,基本的测试原理是对被测电路施加一定的激励条件,观测被测电路的响应,与期望值进行对比,如果一致,表明电路是好的;如果不一致,则表明电路存在故障。

按测试方案的区位界定,集成电路测试可以分为片内测试和片外测试两类。片内测试又称可测性设计 (Design For Testability, DFT)。DFT 技术研究的主要目的是提高故障可观测性,降低对外部测试仪器仪表性能的要求,减少测试时问,以实现测试品 质和经济性的均衡。但考虑其带来电路设计复杂性的增加、芯片面积的增加、额外故障的引 ,以及在模拟/射频等范围技术尚不完善等因素,片外测试技术依然是不可忽视的研究重点。

根据被测集成电路类型的不同,集成电路测试可以分为数宇集成电路测试模拟集成电路测试、混合信号集成电路测试、高速信号集成电路测试、射频集成电路测试、可编程器件测试、存储器集成电路测武、系统芯片测试、物联网芯片/微机电系统芯片测试等。

-

集成电路测试方法与工具2024-11-19 2659

-

如何用集成电路芯片测试系统测试芯片老化?2023-11-10 2602

-

集成电路封装测试2023-05-25 4133

-

基于ATE的集成电路测试原理和方法综述2021-06-17 2310

-

请问集成电路的测试有什么技巧?2021-04-14 1882

-

集成电路IC的EMC测试标准2021-01-04 7723

-

集成电路测试仪有什么类别?2019-08-21 3257

-

什么是小尺寸集成电路CDM测试?2019-08-07 5399

-

集成电路测试仪器有哪些_集成电路测试仪组成结构介绍2017-12-20 15420

-

集成电路测试技术与应用2016-09-01 1344

-

模拟集成电路,模拟集成电路是什么意思2010-03-09 2342

-

集成电路测试仪电源电路的仿真设计研究与应用2009-11-21 796

-

集成电路电磁骚扰测试方法2009-10-07 740

-

集成电路2009-09-30 1469

全部0条评论

快来发表一下你的评论吧 !