一本Verilog HDL代码对应电路的书,助你快速编写可综合模型

描述

有很多朋友在后台咨询怎么在编写Verilog HDL代码的同时“脑中有电路”,今天推荐一本图书《Verilog HDL综合实用教程》(英文-Verilog HDL Synthesis A Practical Primer (J. Bhasker) ),我们先看下这本书的定位:

迅速开始编写可综合的Verilog模型。

获悉哪些语言结构可用于综合,这些结构如何映射成硬件,以得到所期望的逻辑电路。

学习如何避免功能的不匹配。

立即开始使用许多常用的硬件元件模型,或针对应用稍作修改后为己所用。

作者也是一位大佬:

J.Bhasker 是IEEE PAR 1364.1 Verilog Synthesis Interoperability Working Group(Verilog SIWG)的主席,该组织致力于建立用于RTL综合的Verilog标准化子集。他是贝尔实验室所开发的ArchSyn综合系统的主要设计者之一。他曾为AT&T和Lucent的许多设计师讲授Verilog HDL语言和Verilog HDL综合课程。他还著有另外一本畅销书“A Verilog HDL Primer”(文末也会提供)。

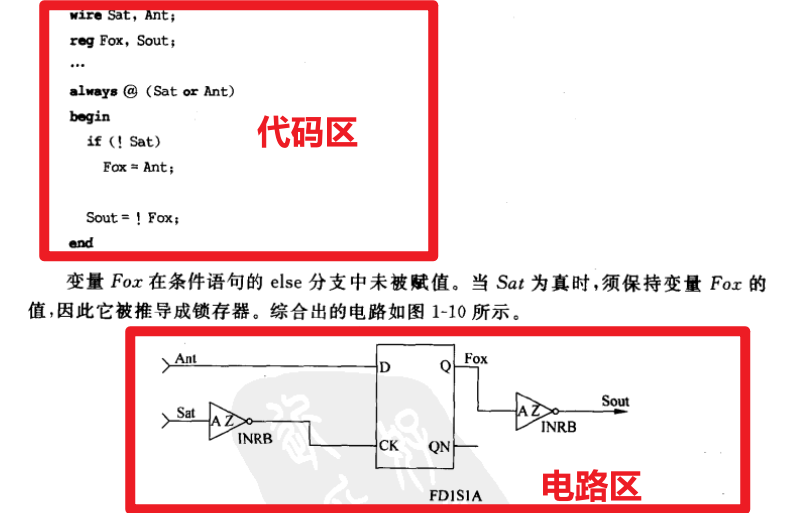

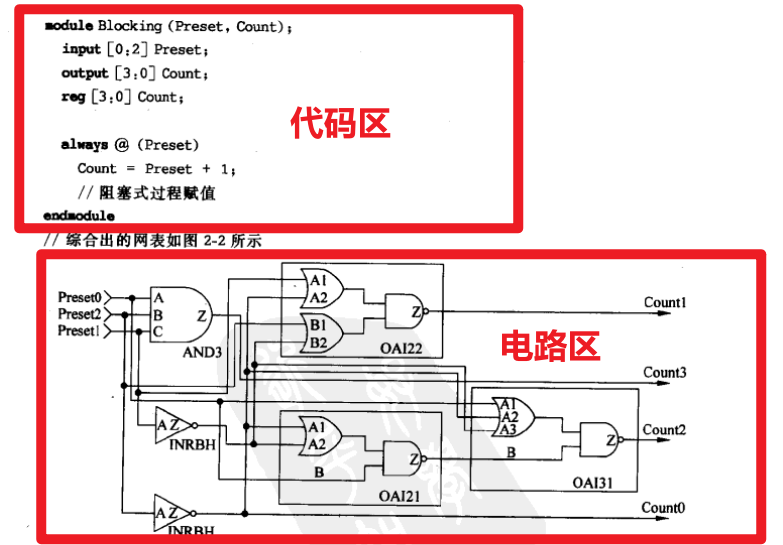

就不过多的进行介绍了,主要是内容我给大家截几张图片看下:

书中基本所有的代码都有相应的电路,这种从代码到电路的映射,会逐渐在你脑海里形成一个“习惯”,以后你再写代码的时候会逐渐在脑海中有这种电路。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

求告知 一本好的verilog HDL教材2011-05-03 2441

-

verilog HDL 可综合模型的结构2012-10-20 2774

-

Verilog+HDL数字设计与综合(第二版2013-10-23 12

-

Verilog HDL代码书写规范2017-12-08 10072

-

Verilog HDL的基本语法2019-09-06 3434

-

基于模型设计的HDL代码自动生成技术综述2021-06-08 4473

-

《Verilog HDL数字系统设计教程》(第四版)学习笔记 part1 Verilog数字设计基础——第一章知识点总结2022-03-22 3342

-

已结束-【盖楼送书NO.10】Verilog HDL与FPGA数字系统设计 第2版2022-04-19 52274

-

Verilog HDL综合实用教程2009-07-20 834

-

Verilog HDL代码描述对状态机综合的研究2011-12-24 785

-

HDL的可综合设计简介2012-01-17 1462

-

设计与验证:Verilog HDL(清晰PDF)2016-10-10 6576

-

如何使用Verilog HDL描述可综合电路?2021-04-04 5236

-

如何使用参数化编写可重用的verilog代码2023-05-11 2051

-

Vivado HDL编写示例2023-05-16 2118

全部0条评论

快来发表一下你的评论吧 !