Verilog边码边学Lesson:图像采集与显示设计之PLL配置与例化

描述

图1 实验平台

视频内容:

Lesson38 图像传感器介绍与设计架构(本节视频)

Lesson39 时钟拓扑、PLL配置与例化

● 图像采集显示设计架构的回顾

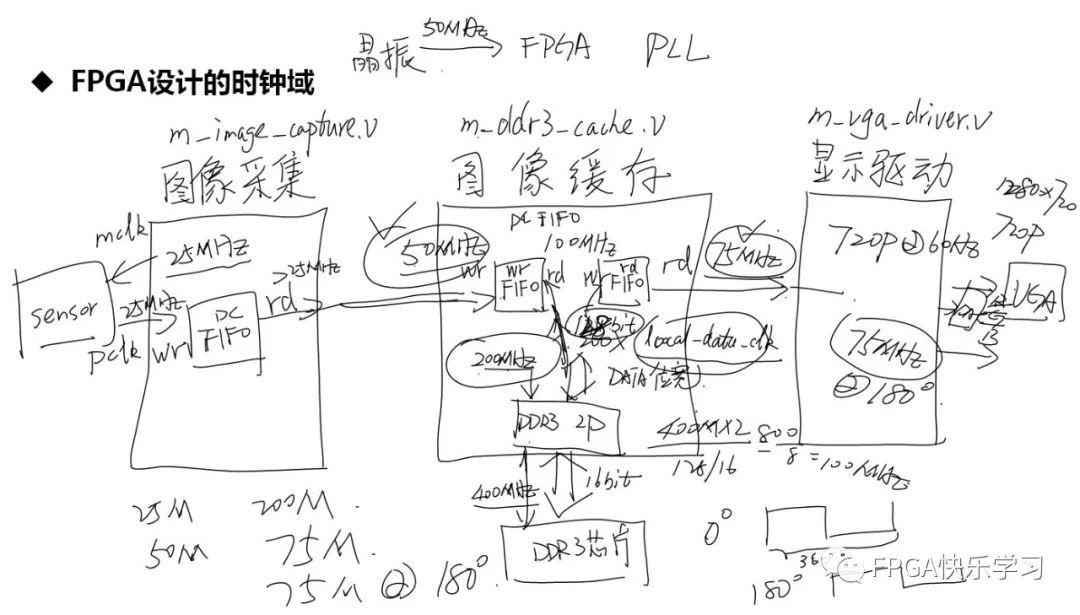

● 设计中各个模块的时钟频率定义

● PLL的输入输出时钟信号拓扑图

● Vivado中PLL IP的配置和添加

● PLL IP的仿真验证

Lesson40 FIFO的配置与使用

Lesson41 图像传输接口时序与在线调试

Lesson42 图像采集模块代码设计

Lesson43 图像采集模块仿真验证

Lesson44 可变位宽的FIFO配置与仿真

Lesson45 DDR3 IP接口说明与地址映射

Lesson46 DDR3缓存模块写控制设计

Lesson47 DDR3缓存模块仿真平台构建

Lesson48 DDR3缓存模块读控制设计

Lesson49 DDR3缓存模块集成仿真

Lesson50 VGA显示驱动模块代码设计

Lesson51 VGA显示驱动模块仿真验证

PLL定义

PLL(Phase Locked Loop):为锁相回路或锁相环,用来统一整合时脉讯号,使内存能正确的存取资料。PLL用于振荡器中的反馈技术。许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

而我们在这里所说的PLL,没有上面一段定义那么晦涩难懂,大家记住PLL一个最主要的功能,即能够对输入的基准时钟信号进行一定范围内的分频或者倍频,从而产生多个输出时钟信号供芯片内部的各个功能模块使用。

多时钟设计

在FPGA的实际工程设计中,很难以一个特定的时钟频率打天下。由于FPGA具备丰富的接口协议,能以应对各种不同外设所需要的或高速、或低速、或差分、或单端、电平或高或低等不同接口。那么,要在这些外设之间游刃有余,平稳过度,就需要产生各种不同的时钟频率和提供跨时钟域的数据通信能力。这些,对于FPGA来说都是再基本不过的功能了。

以图像采集和显示设计为例,FPGA外接的图像传感器需要25MHz的时钟,而返回的有效数据也是以同样的同频不同相的时钟进行同步;在FPGA内部为了更好的达到时序收敛和性能水平,需要一个更稳定和能以满足处理需要的的时钟频率(如本设计的50MHz);接着是图像的缓存,其数据的同步时钟是由DDR3控制器IP给出的100MHz的时钟,而在此之前,需要有一个200MHz的时钟作为DDR3控制器IP的输入;最后的显示驱动,720p的分辨率,要达到60Hz的显示刷新率,就需要75MHz的时钟。这么一看,就这么个不大的设计,涉及的时钟频率还真不少。

图2

时钟的定义和分配,可以说是由设计的各个外设和设计本身的处理性能需要共同决定的,那么我们这个设计中又是如何进行具体的定义、分配、产生呢?欢迎进入我们的视频课程进行深入的学习!

审核编辑:汤梓红

-

例说FPGA连载31:PLL例化配置与LED之PLL的IP核配置2016-09-12 5931

-

UART串口收发实验发送数据和接收的数据不一致(FPGA/CPLD边学边练---快速入门Verilog/VHDL)2017-11-30 9959

-

特权同学 Verilog边码边学 Lesson01 Vivado下载与安装2020-04-22 3211

-

** Error: ddr3_model_parameters.vh(2968): (vlog-2155) Global declarations are illegal in Verilog 2001 syntax.2020-10-18 4401

-

基于OpenCV的灰度图像伪彩色化研究边栓成2017-03-17 1183

-

Lesson38 图像传感器介绍与设计架构2023-05-22 1431

全部0条评论

快来发表一下你的评论吧 !