通过简单的保存-恢复策略避免UVM VIP的冗余仿真周期

描述

在许多验证环境中,我们在不同的测试用例中重复使用相同的配置周期。这些周期可能涉及从不同的配置和状态寄存器写入和读取、加载程序存储器和其他类似任务,以为其目标激励设置DUT。在许多此类环境中,这些配置周期所花费的时间非常长。此外,由于验证工程师必须为不同的测试用例运行同一组经过验证的配置周期,因此存在大量冗余,从而导致生产力下降。对于具有多个接口的复杂验证环境尤其如此,这些接口需要配置不同的组件。

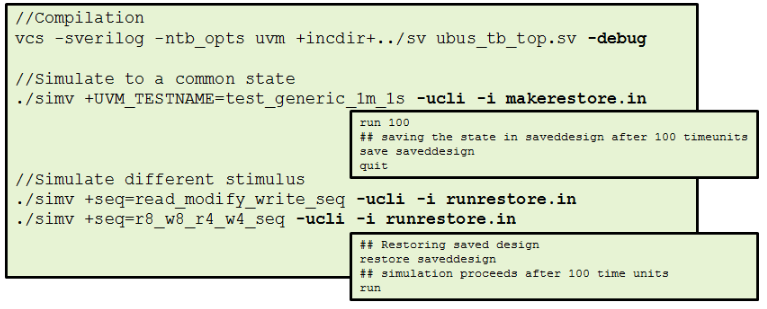

Verilog 提供了在特定时间点保存设计及其测试平台状态的选项。我们可以将模拟恢复到相同的状态,然后从那里继续。这可以通过从Verilog代码添加适当的内置系统调用来完成。VCS 提供与统一命令行解释器 (UCLI) 相同的选项。

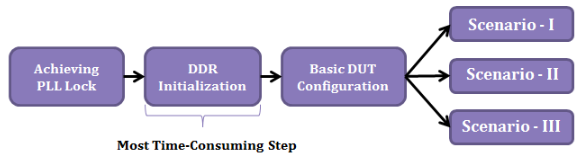

但是,我们仅从保存的状态恢复仿真是不够的。对于不同的模拟,我们可能希望对DUT应用不同的随机激励。在 UVM 的上下文中,最好从保存的状态运行不同的序列,如下所示:

在上面的例子中,除了最后一步在很大程度上变化之外,其余步骤一旦建立就不需要迭代。

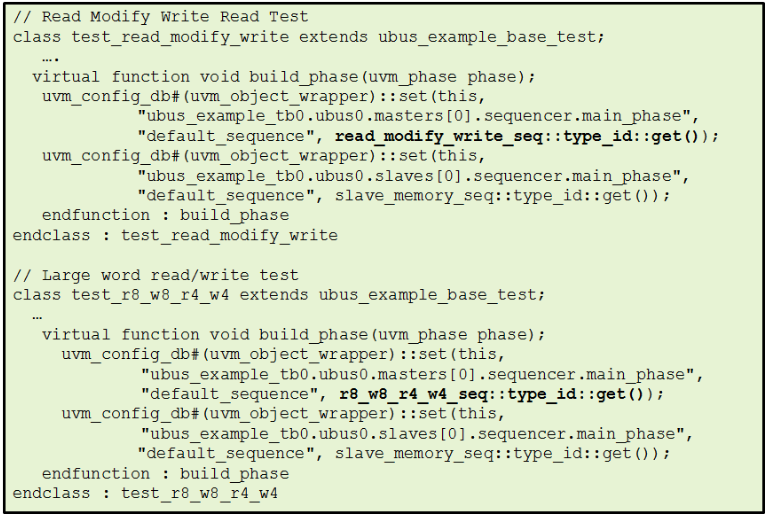

在这里,我们将解释如何使用标准UVM安装中可用的简单现有UBUS示例来实现上述策略。在环境中进行了简单的更改,以显示引入此附加功能需要执行的操作。在现有的测试集中,它们中的两个,“test_read_modify_write”和“test_r8_w8_r4_w4”,仅在执行的主序列上有所不同:“read_modify_write_seq”和“r8_w8_r4_w4_seq”。

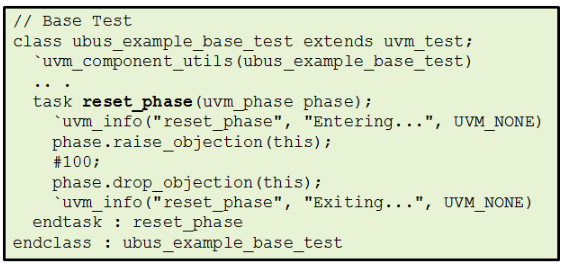

假设我们有一个场景,我们希望在reset_phase完成后保存模拟,然后在恢复的模拟reset_phase后开始执行不同的序列。为了通过UBUS测试演示类似的场景,我们在基本测试的reset_phase中引入了延迟(在实际测试中,这可能对应于PLL锁,DDR初始化,基本DUT配置)。

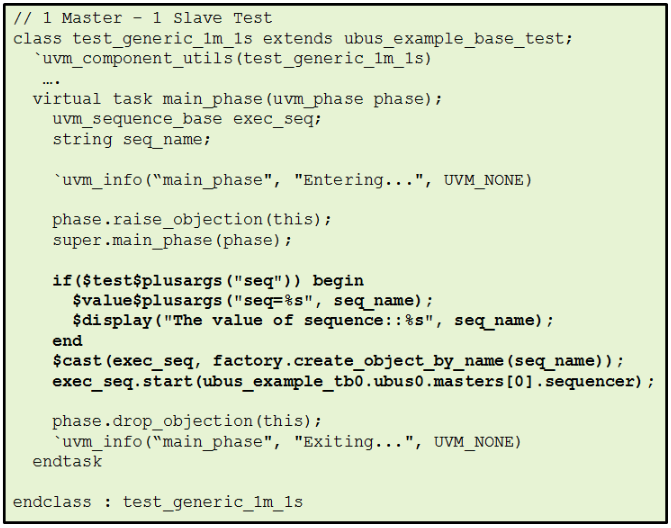

以下代码片段显示了如何修改现有测试,以引入在不同“还原”模拟中运行不同测试的功能:

在这里,我们进行了两个主要修改:

将阶段default_sequence的设置从构建阶段转移到主阶段的开始。

从命令行获取序列的名称作为参数,并在代码中适当地处理字符串,以在相关排序器上执行序列。

如您所见,更改保持在最低限度。有了这个,上面的通用框架就可以进行了仿真。在 VCS 中,启用保存/恢复流程的一种方法是:

因此,上述策略有助于通过验证流程中的简单更改来优化计算资源。希望这很有用,并且您可以轻松地在验证环境中进行更改以采用此流程并避免冗余的模拟周期。

审核编辑:郭婷

-

图像处理:HDMI显示代码的UVM仿真2020-11-10 6274

-

vcs和xrun搭配uvm1.1/uvm1.2版本库的使用情况2023-10-27 7807

-

UVM环境的看门狗怎么没看住超时了?2023-12-04 2334

-

UVM手把手教程系列(二)Phase机制简单介绍2024-02-29 3255

-

如何避免存储示波器再次崩溃?2025-05-23 1498

-

NVMe高速传输之摆脱XDMA设计18:UVM验证平台2025-07-31 14563

-

NVMe高速传输之摆脱XDMA设计23:UVM验证平台2025-08-26 1055

-

IC验证"一个简单的UVM验证平台"是如何搭建的(六)2020-12-04 2804

-

什么是uvm?uvm的特点有哪些呢2022-02-14 1882

-

请问一下在UVM中的UVMsequences是什么意思啊2022-04-11 5557

-

如何使用Xilinx AXI VIP对自己的设计搭建仿真验证环境的方法2022-10-09 5121

-

NetScreen防火墙策略与冗余配置指南2010-05-16 930

-

基于最大信息系数与冗余分摊策略的特征选择方法2021-03-26 1016

-

开始使用AXI VIP,对UVM有一些基本的了解2023-05-25 11590

-

Jtti:如何在服务器扩展时避免单点故障?有哪些常见的高可用性策略?2024-07-18 872

全部0条评论

快来发表一下你的评论吧 !