常见的Verilog行为级描述语法

电子说

1.4w人已加入

描述

常见的模块介绍:选择器;译码器;解码器;比较器。这里我们主要从常见的Verilog描述的层面去介绍,而不着重考虑电路。将会提到的Verilog语句有 条件选择语句,case语句,if-else。

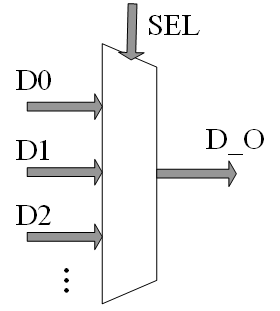

选择器:电路示意图如下。根据SEL信号,选择将D0还是D1,或者D3传递给D_O。即根据SEL信号选择,将某一个输入信号传递给D_O。

对于只有两个输入信号的选择器,我们可以用单层条件选择语句描述。例如输入只有D0,D1两个。那么SEL只要为单bit即可实现选择。SEL为0时,选择将D0传递给D_O;SEL为1时,选择将D1传递给D_O;

assign D_O = (SEL) ? D1:D0;

注意:条件选择语句功能: 当 ( ) 里面的 expression0 的条件为真时,则选择第一个表达式expression1里面的结果,否则选择 :后面expression2的结果。结构如下:

assign out = (expression0) ? expression1 : expression2

有多个输入信号时。例如:有3个输入,D0,D1,D2; 因为2的2次方等于4,故SEL最小的位宽应该为2。若要实现如下选择功能。

对应可以使用 case 语句描述:

reg[7:0] D_O;*

always @(*) begin*

case(SEL[1:0])*

2b00: D_O = D0;*

2b01: D_O = D1;*

2b10: D_O = D2;*

default: D_O = h0; *

endcase*

end*

注意:case语句,如果SEL的所有组合没有列全,最好在最后要加上 default: ... 项,使得信号完整。如此综合出来的电路才不会出现锁存器。

3-8译码器,功能如下真值表:

对应的可以用case语句去描述它的功能:

reg[7:0] D_O;*

always @(*) begin*

case(D_IN[2:0])*

3b000: D_O = 8b1111_1110;*

3b001: D_O = 8b1111_1101;*

3b010: D_O = 8b1111_1011;*

3b011: D_O = 8b1111_0111;*

3b100: D_O = 8b1110_1111;*

3b101: D_O = 8b1101_1111; *

3b110: D_O = 8b1011_1111;*

3b111: D_O = 8b0111_1111;*

endcase*

end*

同样对于8-3解码器,大家可以自行去练手。

比较器,或者说判断器。比如比较两个数的大小,当a>b是,输出信号en为高,否则为低。

if-else描述:

reg en;*

always @( * )*

if( a>b )*

en = 1;*

else*

en = 0;*

当然也可以用条件选择语句:

wire en;*

assign en = (a>b) ?1b1 : 1b0;*

本文重在通过逻辑实例帮助大家理解常见的Verilog逻辑描述语言。大家在知道自己要实现的功能的情况下,去选择合适的描述方式。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

使用Verilog/SystemVerilog硬件描述语言练习数字硬件设计2022-08-31 2654

-

Verilog硬件描述语言参考手册免费下载2021-02-05 1434

-

Verilog硬件描述语言的学习课件免费下载2021-01-22 1089

-

通过实例设计来加深Verilog描述语法理解2021-01-02 2227

-

硬件描述语言(HDL)编码技术:xilinx verilog语法技巧2020-12-13 4336

-

基于Verilog硬件描述语言的IEEE标准硬件描述语言资料合集免费下载2020-06-18 1056

-

常见的Verilog行为级描述语法2018-09-15 10855

-

新手求教、verilog中行为描述与结构描述区别?2016-10-27 9591

-

Verilog硬件描述语言2016-09-01 765

-

Verilog HDL硬件描述语言_行为建模2016-04-25 721

-

Verilog HDL硬件描述语言2015-12-29 707

-

Verilog硬件描述语言参考手册2015-11-12 844

-

verilog硬件描述语言课程讲义2012-05-21 870

-

Verilog硬件描述语言描述.2006-03-27 1535

全部0条评论

快来发表一下你的评论吧 !