谈谈Verilog/System Verilog和C的几种交互模式

电子说

描述

最近有群友问我system Verilog 和C怎么交互,在网上搜了一圈发现资料比较少,今天这里就和大家讲讲system Verilog 和C的交互。话不多说直接上干活。

第一种 Verilog 通过PLI调用C函数。

PLI全称 Program Language Interface,程序员可以通过PLI在verilog中调用C函数,这种访问是双向的。这些用户定义的系统任务和函数的名称必须以美元符号"" 开头。大家用得比较多的PLI函数有display,$finish等。

用户可以自定义PLI函数,下面是一个简单的PLI应用例子。

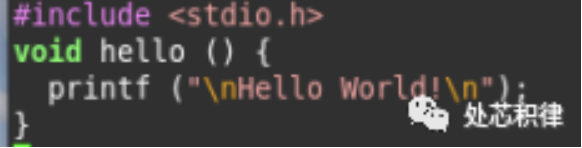

以下是一段C代码

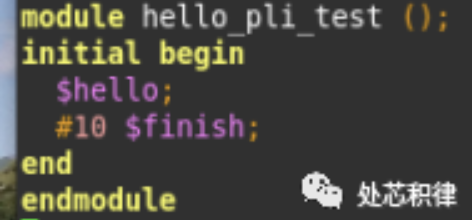

下面是一段调用C的verilog的代码

第二种 System Verilog 通过DPI和C进行交互

为了更加简洁的连接C,system verilog 引入了DPI(Direct Programming Interface)。只要使用import声明和使用,导入一个C子程序,就可以像调用System Verilog中的子程序一样来调用它。相反,如果C想用system verilog里面的函数用export 声明即可。下面是一个简单的例子。

在System Verilog 里面调用C函数

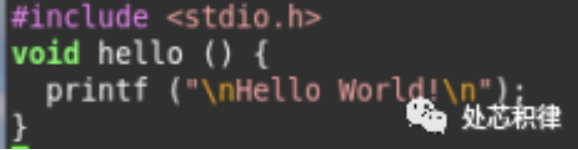

C代码和上面一样

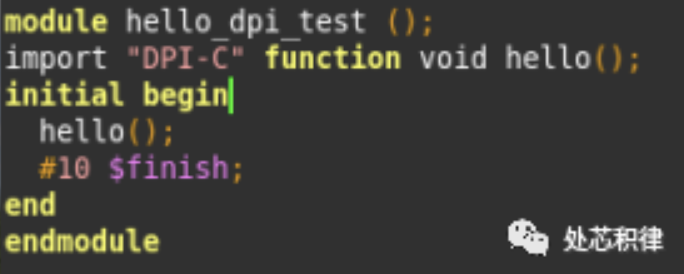

System Verilog的代码如下

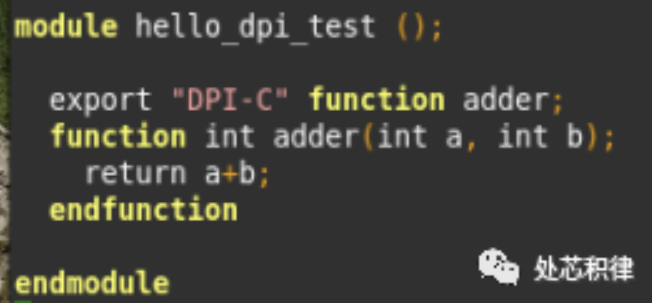

在C中调用System Verilog 函数

System Verilog 的代码如下

C代码如下

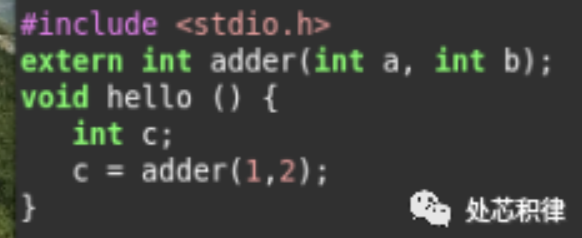

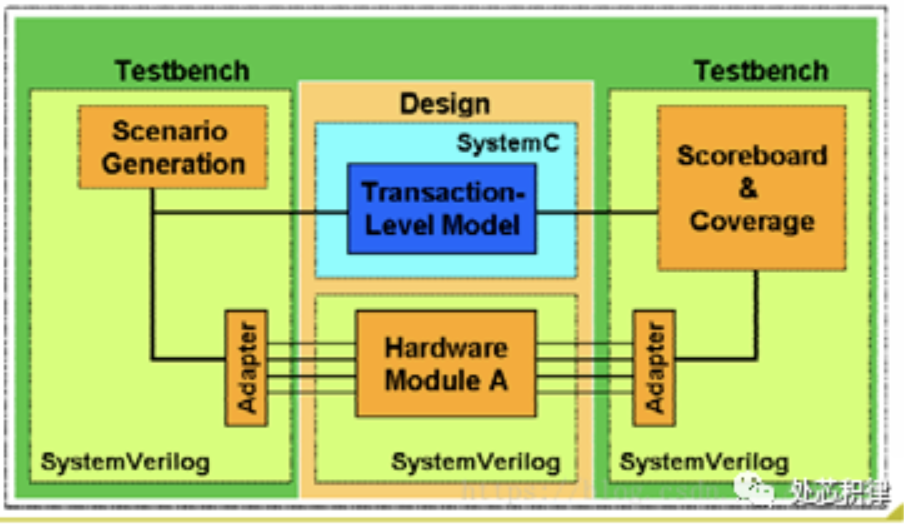

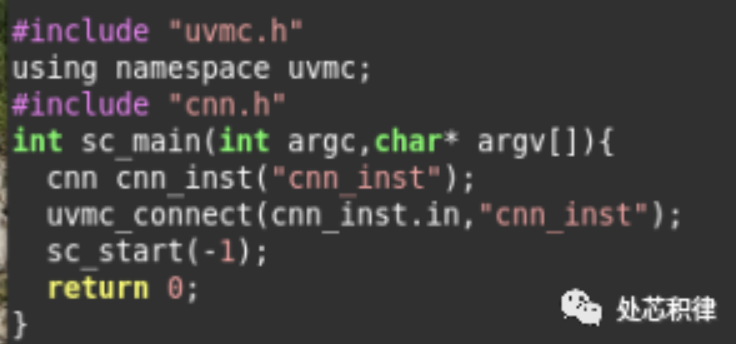

第三中 System Verilog 和C的交互方式是通过TLM1.0或者TLM2.0 进行交互。

这种交互方式主要应用在System Verilog 和systemc 上。对于systemc一般人用得比较少,所以这类交互也比较少用。下面是一个简单的例子

Systemc 的编码,其中cnn_inst的接口in是tlm1/tlm2类型port。

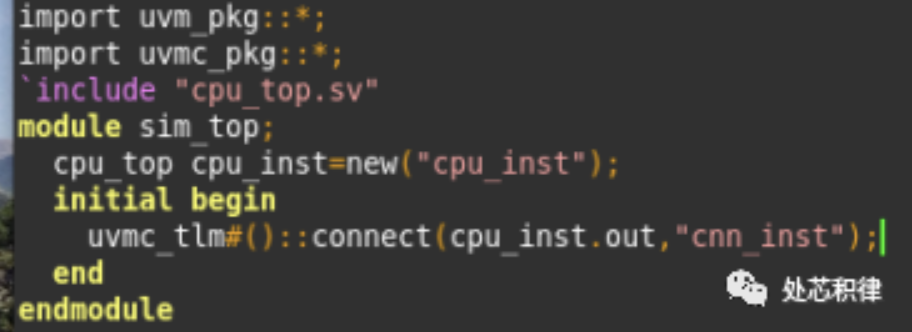

System verilog 的编码,cpu_inst.out 为tlm1/tlm2类型的port。

第四种交互方式,通过CPU执行C代码,从而实现verilog 和C的交互。

C代码通过工具链编译成CPU可以执行的汇编指令,再将汇编指令转成对应的指令代码,然后通过CPU读取指令代码产生激励,实现C代码所描述的功能。

以上是Verilog/System Verilog 和C的几种交互模式,小伙伴们学会了吗?

-

System Verilog问题和语言参考手册规范2020-12-24 3024

-

Verilog Digital System Design2009-07-23 987

-

VHDL,Verilog,System verilog比较2012-01-17 2011

-

基于System Verilog中的随机化激励2017-10-31 1051

-

verilog是什么_verilog的用途和特征是什么2018-05-14 47456

-

浅谈Verilog-95、Verilog-2001与System Verilog之间的区别2021-06-21 12624

-

System Verilog与verilog的对比2021-09-28 4829

-

Verilog HDL入门教程-Verilog HDL的基本语法2022-01-07 2467

-

学会这些System Verilog方法,芯片验证入门没问题2022-12-09 5936

-

浅谈System Verilog的DPI机制2023-05-23 3953

-

谈谈system Verilog 和C的交互2023-05-31 1119

-

System Verilog的概念以及与Verilog的对比2023-06-12 2531

-

system verilog语言简介2024-11-01 475

-

如何自动生成verilog代码2024-11-05 2241

-

Verilog与VHDL的比较 Verilog HDL编程技巧2024-12-17 3569

全部0条评论

快来发表一下你的评论吧 !