锁相环(PLL)规格及架构研究

描述

锁相环(PLL),作为Analog基础IP、混合信号IP、数字系统必备IP,广泛存在于各类电子产品中。

本文以SoC中的PLL为例,对PLL规格及架构分别进行研究和确定。

先进行规格研究:

典型的PLL规格如下:

| 参数 | 示例 |

|---|---|

| 参考时钟频率 | 13MHz~76.8MHz |

| 输出时钟频率 | 100MHz~2GHz |

| 锁定时间 | <100uS |

| Period Jitter RMS | <2ps |

| 输出时钟duty cycle | 40%~60% |

| 功耗 | <5mA |

| 输出时钟频率精度 | <±300ppm |

对于SoC中的数字系统,CPU、GPU、ISP、NPU等,PLL规格分别如下:

1)参考时钟频率

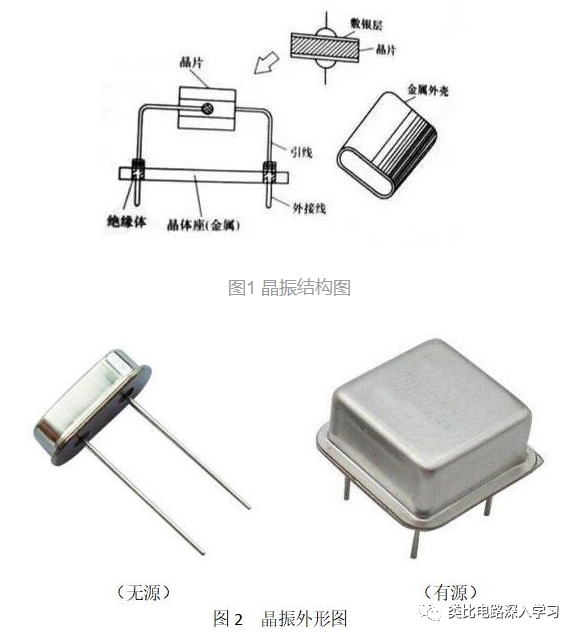

PLL参考时钟一般来自于晶振(有源晶振或无源晶振),或者来自于系统中PCB上的其它芯片;

晶振的频率选择一般是,价格、精度要求、phasenoise需求、频偏要求、温度系数等因素折中考虑;

本设计仅考虑SoC数字系统,因此参考时钟频率考虑兼容常用的频率,13MHz~76.8MHz,频率精度<±300ppm;

2)输出时钟频率

输出时钟频率的下限,系统一般没有要求,因为数字电路可以通过分频器分频实现;而频率的上限在芯片规格定义中有规定,一般由数字IP spec、工艺、数字后端物理实现综合决定。

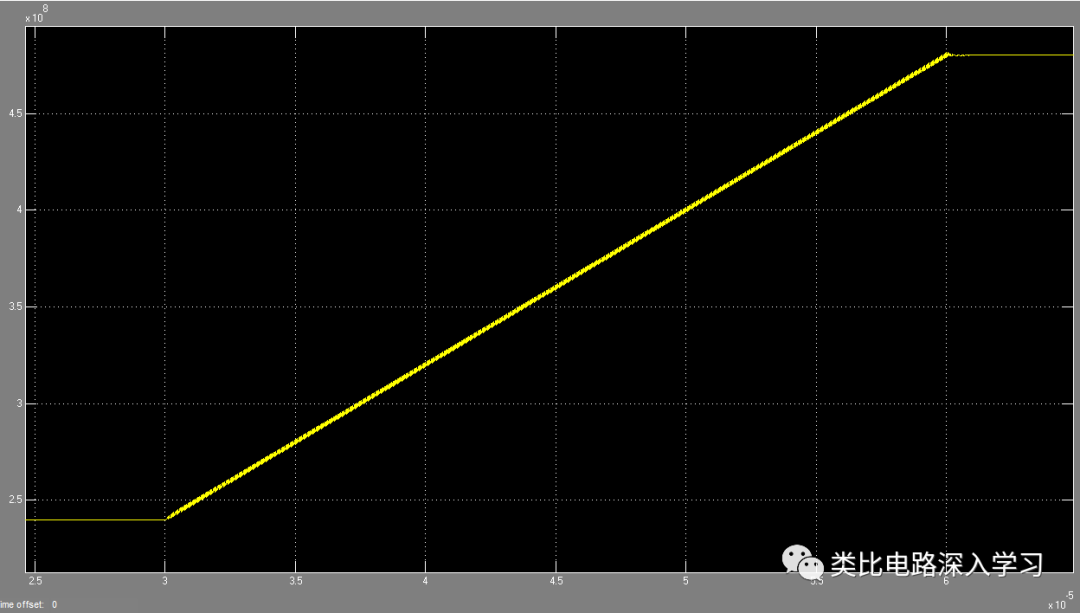

如果是给CPU提供时钟,如果系统需要支持DVFS,那么PLL需要支持线性调频;

如果是给外设、接口提供时钟,那么PLL可能需要支持展频。

3)锁定时间

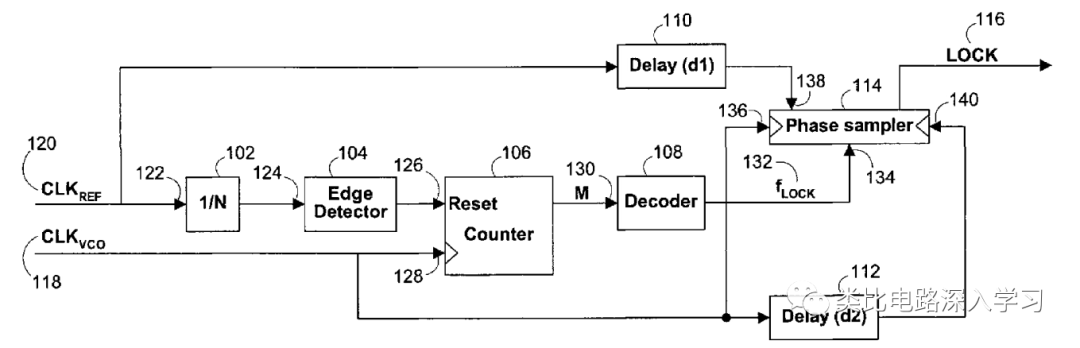

数字系统一般对于锁定时间没有严格的要求,Ring PLL一般锁定时间都在200us以内,可以采用reference频率数counter的“硬等”方式。更合理的方式是增加锁定检测电路lock detect,输出标志锁定的数字信号。

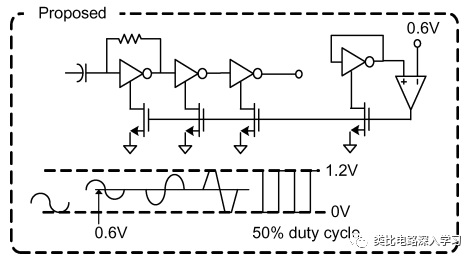

4)duty cycle

输出时钟占空比,如果直接从VCO送出来的时钟,占空比会在40%~60%。为了得到45%~55%占空比时钟,可以采用DCC、self-bias、二分频等处理。

5)功耗

SoC PLL由于性能要求不高,其消耗总电流约为几mA,对于数字系统而言占比很小。所以通常不会有特殊要求。

6)RMS Jitter

数字系统关心的是哪种jitter?jitter数值应该如何确定?

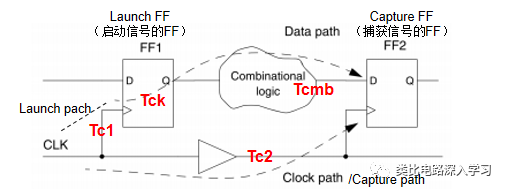

我们知道数字后端设计STA的两个主要的指标,setup和hold。

本质是保证DFF的正常功能PVT下仍有一定的margin,

a) 上一个时钟沿同步过来的数据,必须发生在下一个时钟沿之前;

b) lauch DFF在当前时钟沿得到的数据,必须发生在capture DFF当前时钟沿之后。

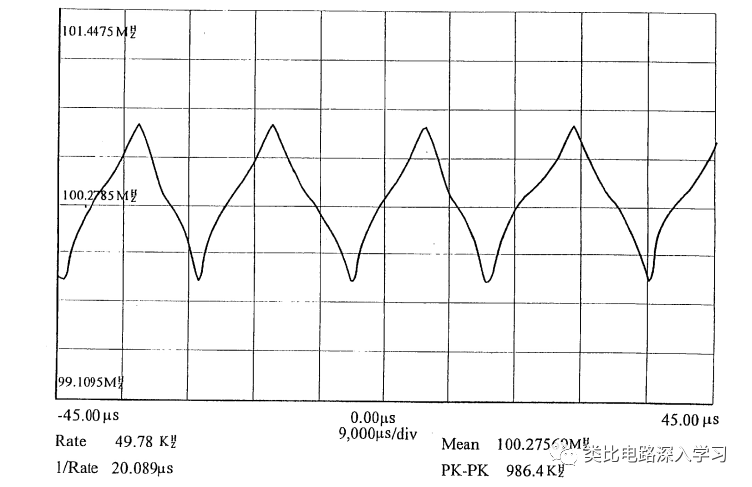

从a)和b)可以得知,数字系统对于时钟的要求是,相邻时钟沿最小的变化,也就是时钟周期period最小的变化。

因此数字系统关心时钟的jitter类型为Period Jitter,越小越好。

综上SoC PLL的规格确定如下:

| 参数 | 示例 |

|---|---|

| 参考时钟频率 | 13MHz~76.8MHz |

| 输出时钟频率 | 100MHz~2GHz |

| 锁定时间 | <100uS |

| Period Jitter RMS | <2ps |

| 输出时钟duty cycle | 40%~60% |

| 功耗 | <5mA |

| 输出时钟频率精度 | <±300ppm |

下面进行架构研究:

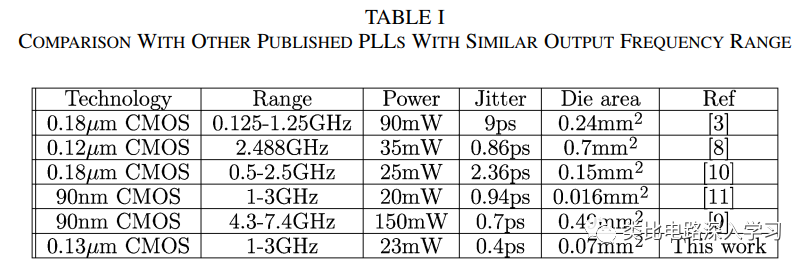

PLL的相位噪声要求低、需要宽频率调节范围、小面积。因此PLL中的VCO采用环形振荡器的结构,即Ring PLL。

PLL架构分为

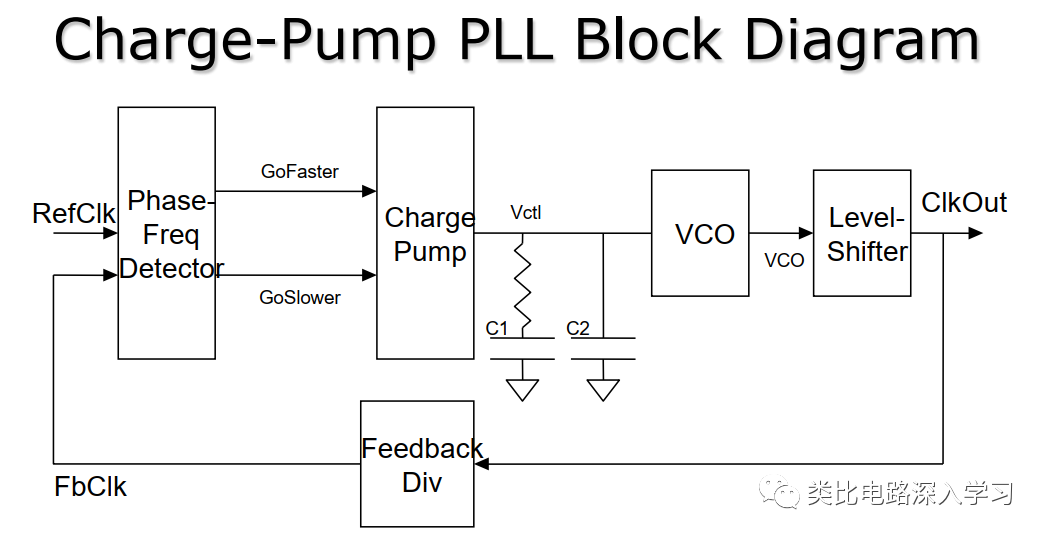

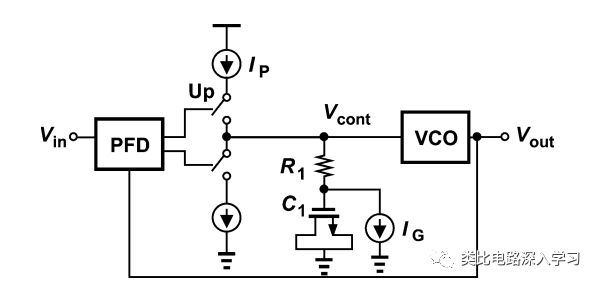

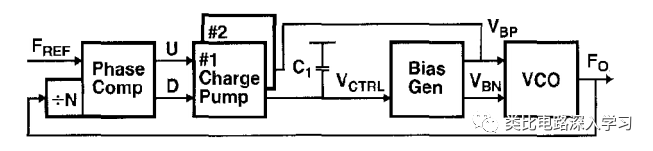

CP PLL(single-path loop filter/dual-path loop filter)

Self-bias PLL

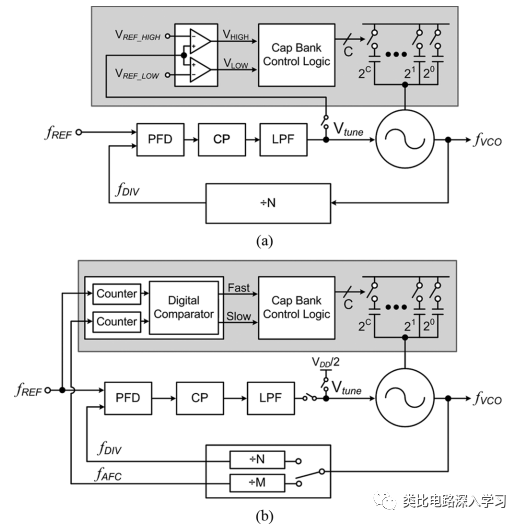

coarse/fine PLL

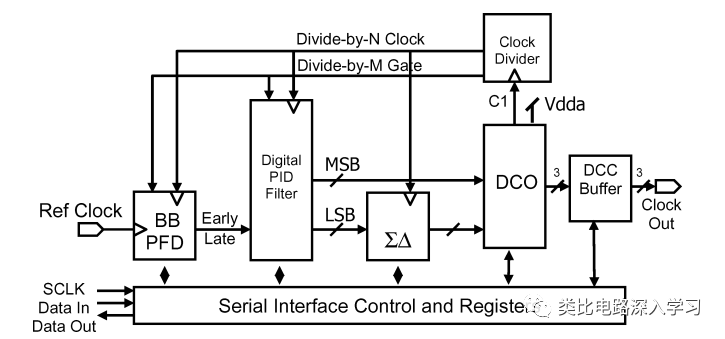

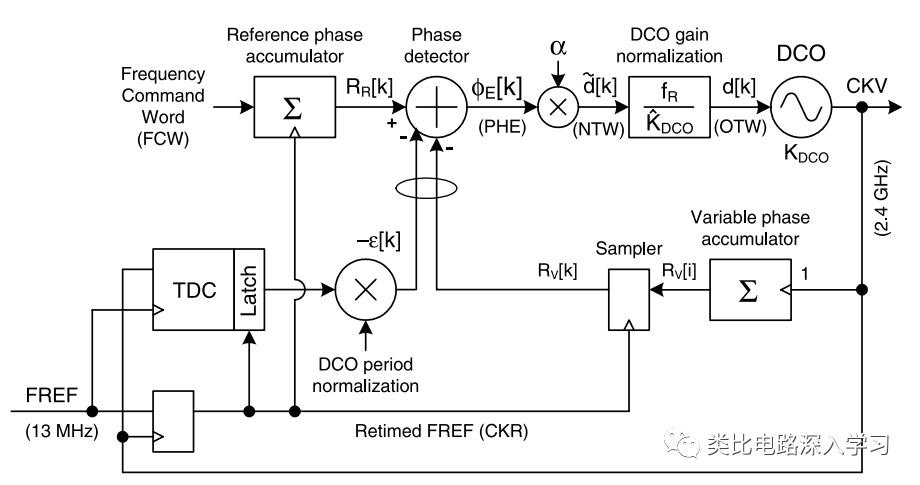

counter-based ADPLL

divider-based ADPLL

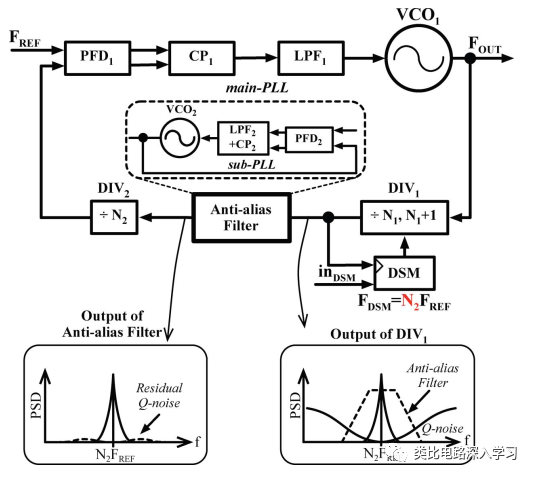

nested-PLL

本文将采用CP PLL(single-path loop filter),即最传统也是最可靠的结构进行设计。子模块结构的选择将在设计中逐步展开。

-

锁相环PLL的工作原理 锁相环PLL应用领域2024-11-06 4462

-

锁相环(PLL)基本原理 当锁相环无法锁定时该怎么处理的呢?2023-10-23 5370

-

pll锁相环的作用 pll锁相环的三种配置模式2023-10-13 5673

-

pll锁相环倍频的原理2023-09-02 5262

-

关于锁相环(PLL)的工作原理2023-04-28 10289

-

pll锁相环倍频2023-02-14 3790

-

LabVIEW锁相环(PLL)2022-05-31 8100

-

锁相环(PLL)的工作原理及应用2022-03-29 16301

-

PLL(锁相环)电路原理是什么?2022-01-21 4108

-

MT-086: 锁相环(PLL)基本原理2021-03-21 1983

-

如何设计并调试锁相环(PLL)电路2016-01-07 1341

-

锁相环2011-10-26 17708

-

锁相环(PLL)电路设计与应用2011-09-14 7976

-

锁相环(PLL),锁相环(PLL)是什么意思2010-03-23 6462

全部0条评论

快来发表一下你的评论吧 !