锁相环(PLL)建模及仿真分析

描述

behavior model,即建立行为级模型。主要采用matlab、veriloga等工具,对设计进行行为级建模。

通过建模,确定设计核心参数、非理想因素对于电路的影响、对电路的功能进行快速验证。

本文以SoC中的整数PLL为例,行为级建模工具选择matlab。

对PLL的环路参数进行设计,并通过行为级模型进行仿真。

PLL,是一个小型的控制系统。规格如下:

| 参数 | 示例 |

|---|---|

| 参考时钟频率 | 13MHz~76.8MHz |

| 输出时钟频率 | 100MHz~2GHz |

| 锁定时间 | <100uS |

| Period Jitter RMS | <2ps |

| 输出时钟duty cycle | 40%~60% |

| 功耗 | <5mA |

| 输出时钟频率精度 | <±300ppm |

其环路参数的分析、假定和计算如下:

1)环路分频比N

根据输入频率范围26M76.8MHz,输出频率范围104M2.002GHz。可以计算得到环路分频比N范围为4~77

2)电荷泵电流Icp

这里先假定为2uA

3)压控振荡器的增益Kvco

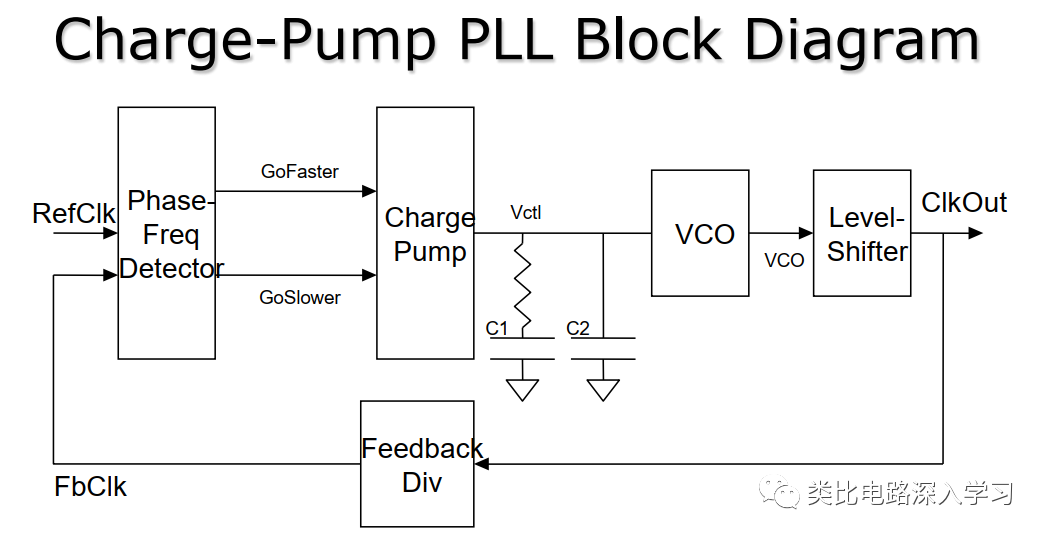

由于本文采用CP PLL(single-path loop filter),即最传统也是最可靠的结构进行设计。因此控制电压在0~vdd范围内变化,频率需要在PVT下覆盖输出频率范围,因此Kvco这里假定为4GHz/V

- 环路带宽和相位裕度

这里先假定为500kHz和50°

环路参数汇总如下

| 参数 | 选定值 |

|---|---|

| 参考时钟频率FIN | 26MHz |

| 输出时钟频率FOUT | 104MHz~2.002GHz |

| 环路分频比N | 4~77 |

| 电荷泵电流Icp | 2uA |

| 压控振荡器的增益Kvco | 4GHz/V |

| 环路滤波器阶数 | 二阶 |

| 环路带宽BW | 500KHz |

| 环路相位裕度PM | 50° |

根据上述参数进行环路滤波器设计,

1)hands on

R1=BWN/(IcpKvco2PI)=6.87kΩ

C1=tan(PM)/(BWR12PI)=55pF

C2=0.1*C1=5.5pF

2)ToolBox Get

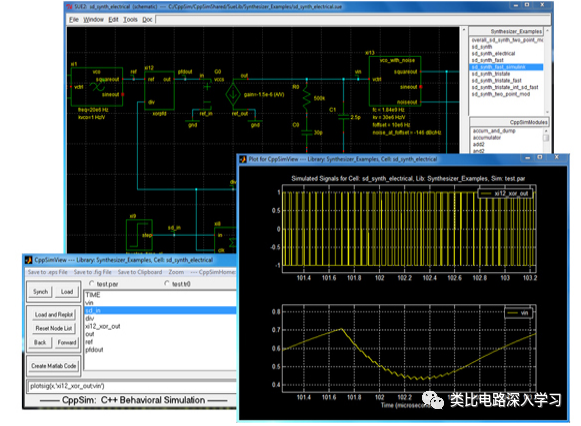

ToolBox CPPSIM by Perrott (http://www.cppsim.com)

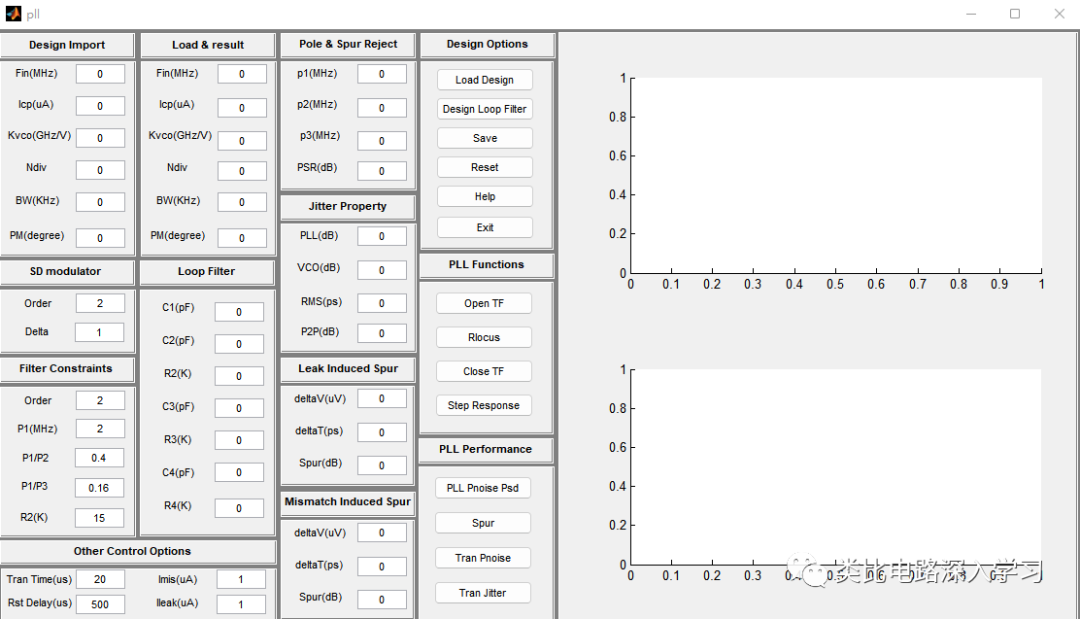

ToolBox pll_tool by EETOP Senior(https://bbs.eetop.cn/thread-448188-1-1.html)

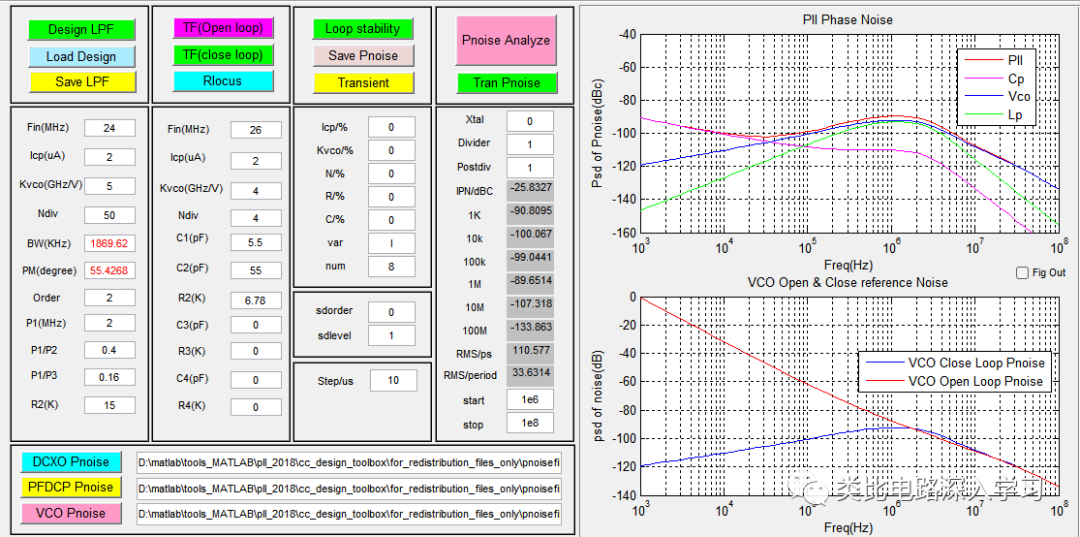

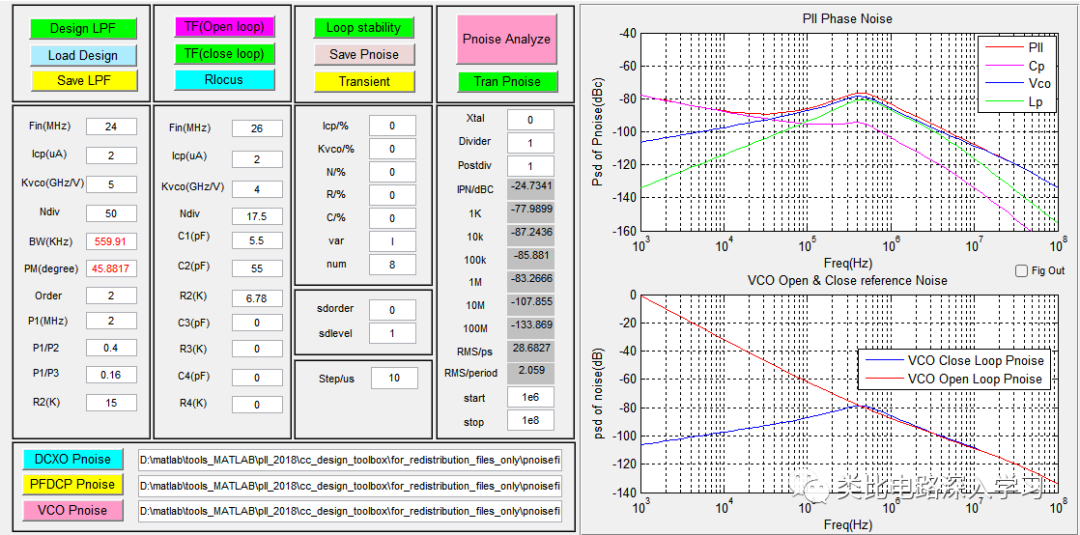

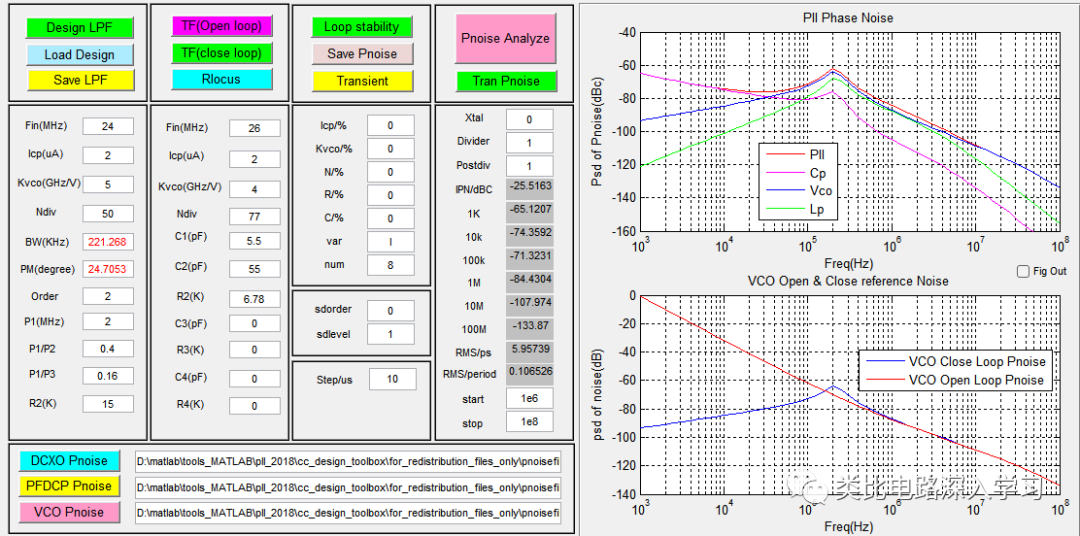

上述参数利用pll_tool进行验证,其中各模块的噪声取设计中的典型值。

N=4/17.5/77

N=17.5

1)环路带宽和相位裕度分别为,560KHz和45.9°

2)period jitter rms=2.06ps@455MHz

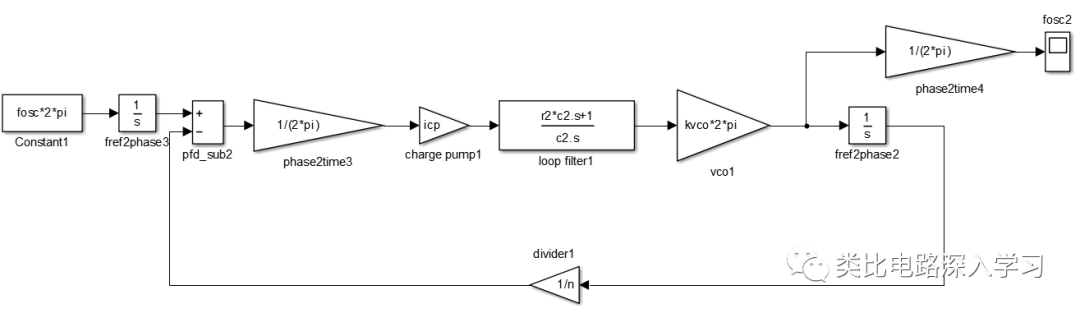

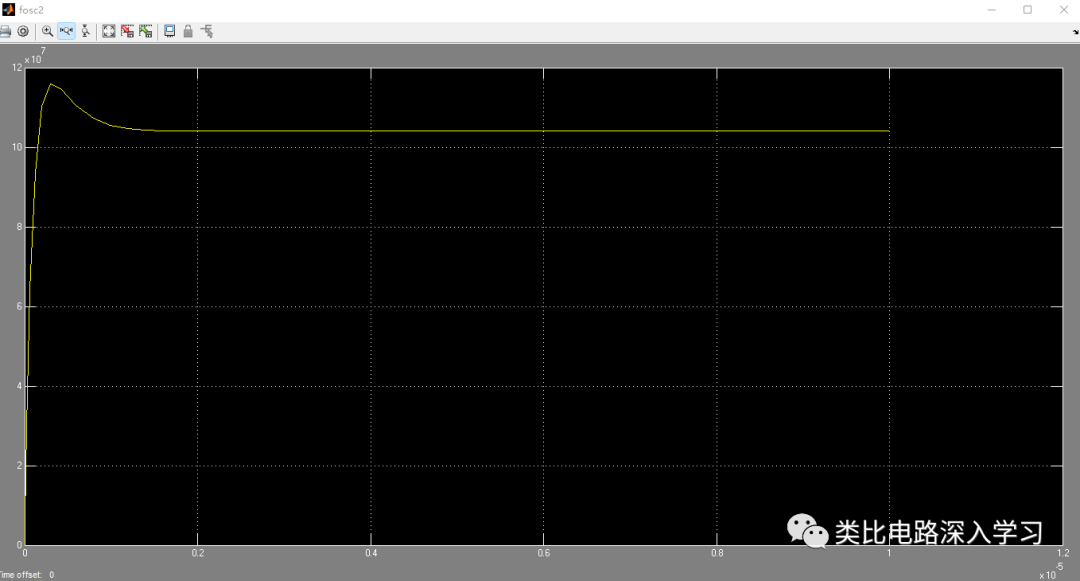

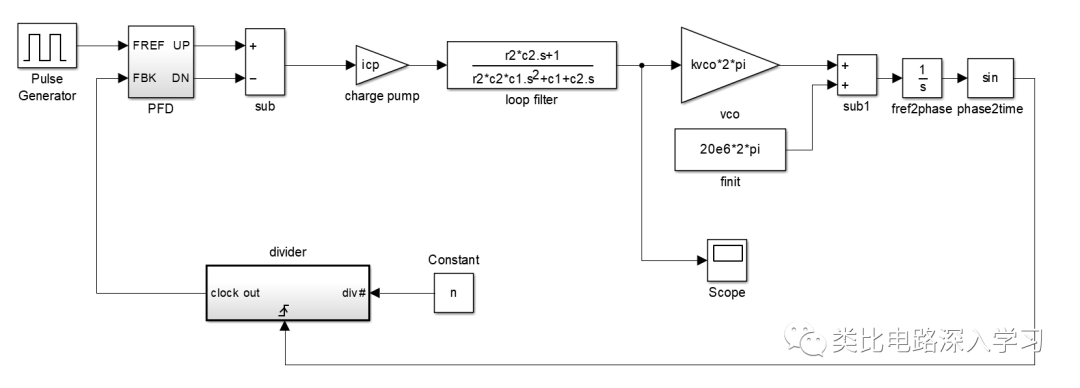

下面用matlab simulink对设计进行仿真

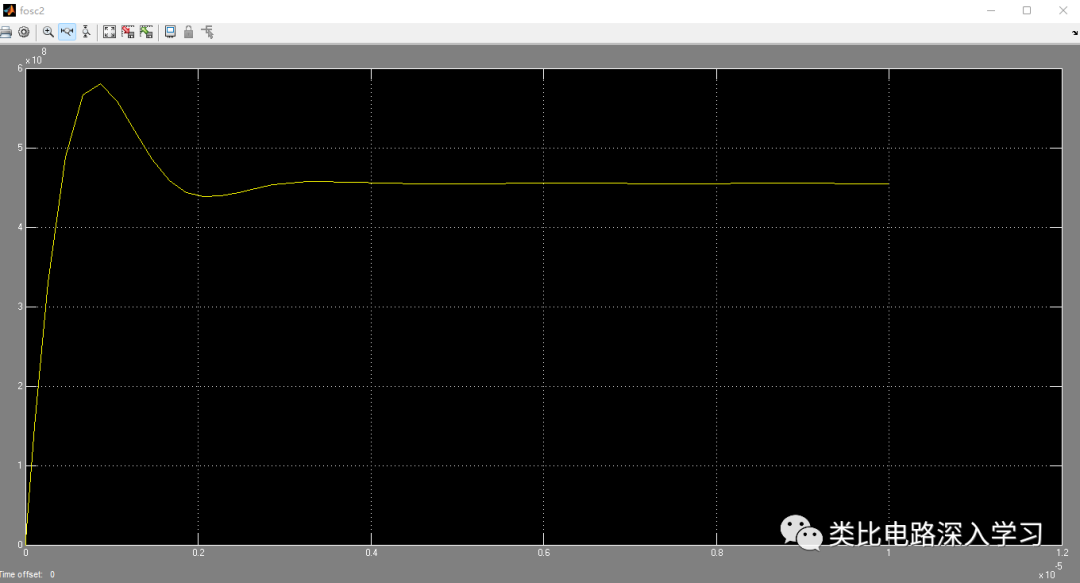

1)ac小信号模型

N=4/17.5/77

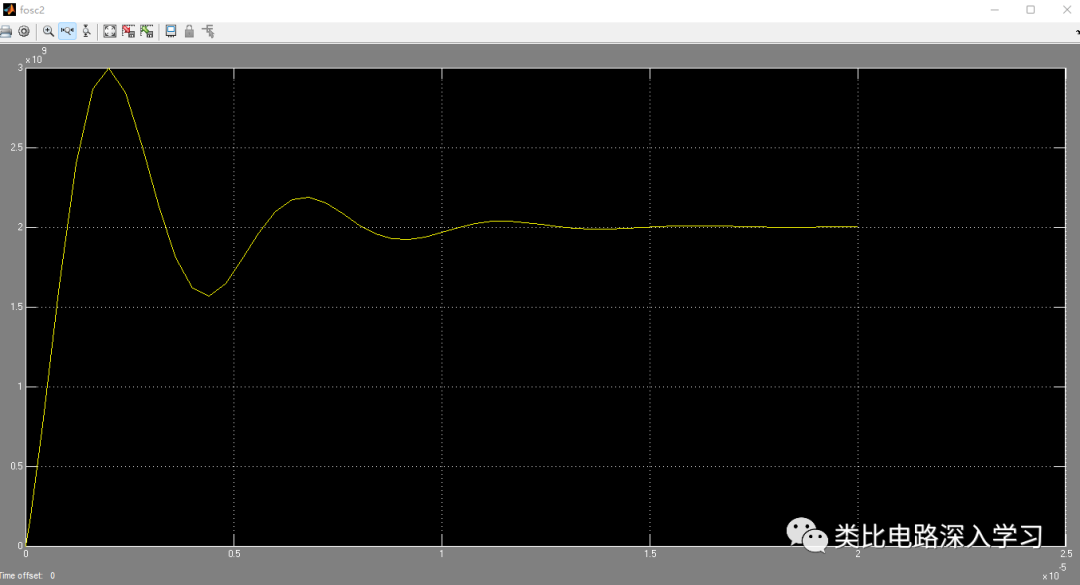

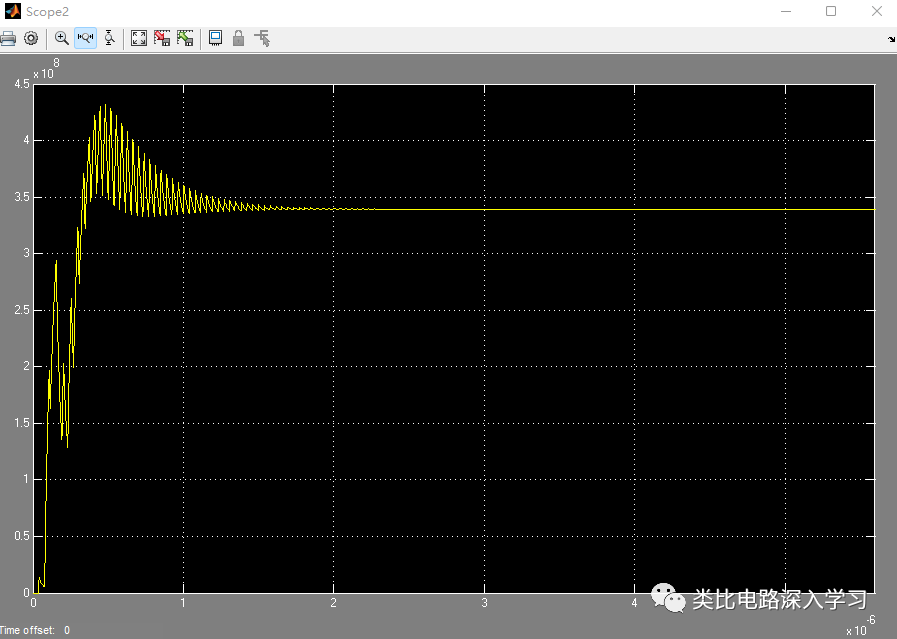

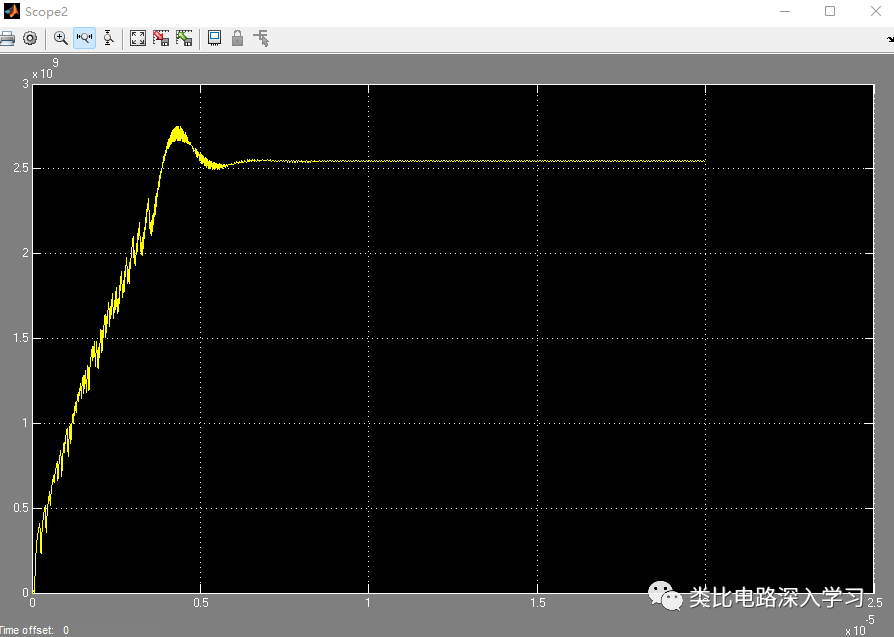

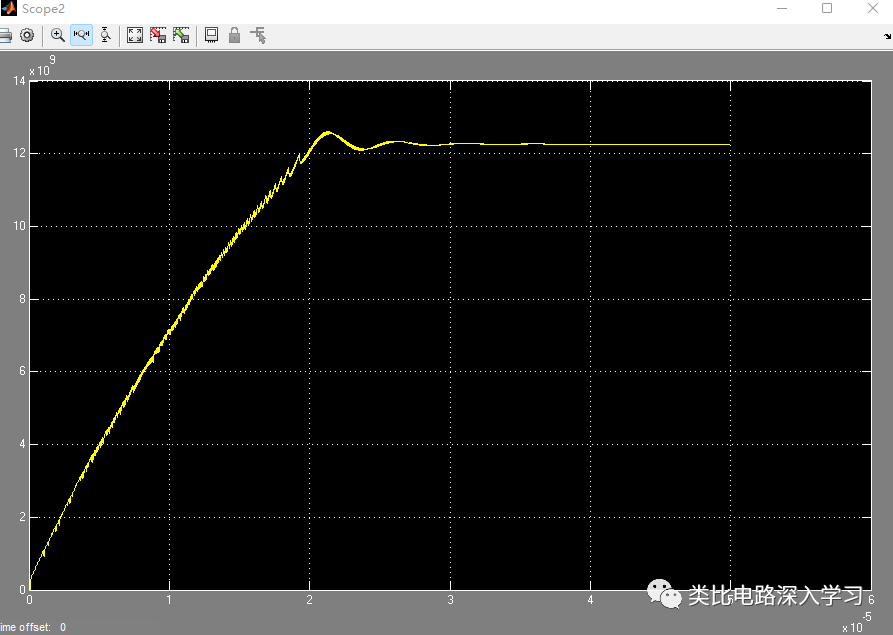

2)大信号模型

N=4/17.5/77

综上,环路参数汇总如下

| 参数 | 选定值 |

|---|---|

| 参考时钟频率FIN | 26MHz |

| 输出时钟频率FOUT | 104MHz~2.002GHz |

| 环路分频比N | 4~77 |

| 电荷泵电流Icp | 2uA |

| 压控振荡器的增益Kvco | 4GHz/V |

| 环路滤波器阶数 | 二阶 |

| 环路带宽BW | 500KHz |

| 环路相位裕度PM | 50° |

| R1 | 6.87kΩ |

| C1 | 55pF |

| C2 | 5.5pF |

-

锁相环(PLL)基本原理 当锁相环无法锁定时该怎么处理的呢?2023-10-23 5531

-

pll锁相环的作用 pll锁相环的三种配置模式2023-10-13 5770

-

pll锁相环倍频的原理2023-09-02 5380

-

关于锁相环(PLL)的工作原理2023-04-28 10414

-

pll锁相环倍频2023-02-14 3841

-

锁相环PLL的基础知识2022-12-23 7045

-

LabVIEW锁相环(PLL)2022-05-31 8127

-

锁相环(PLL)的工作原理及应用2022-03-29 16397

-

PLL(锁相环)电路原理是什么?2022-01-21 4121

-

如何设计并调试锁相环(PLL)电路2016-01-07 1354

-

锁相环2011-10-26 17727

-

锁相环(PLL),锁相环(PLL)是什么意思2010-03-23 6505

-

锁相环的性能,仿真和设计(第3版)2009-07-25 1060

-

锁相环设计仿真与应用2008-08-16 1504

全部0条评论

快来发表一下你的评论吧 !